大家好,欢迎Vivado的一个快速演示,它是xilinx新的设计套件,应用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 电子发烧友网讯 :Altera 公司与FPGA高性能知识产权(IP)内核领先供应商Northwest Logic2012年11月14号宣布,开始提供硬件成熟的1,600 Mbps低延时DRAM (RLDRAM) 3存储器接口解决方案,可用于

2012-11-15 09:32:59 795

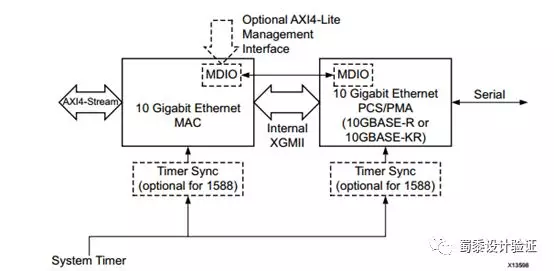

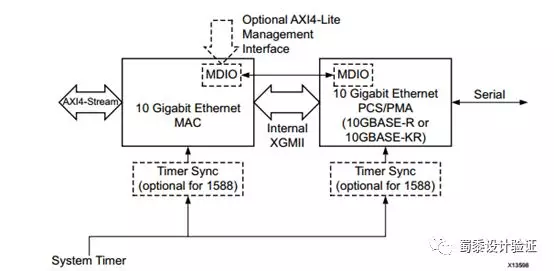

795 IP核描述 10 Giga Ethernet Sub System , 参考文档PG157: https://www.xilinx.com/support/documentation

2020-12-30 12:56:30 2887

2887

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

推出的FPGA设计工具集搭配Zynq UltraScale+ RFSoC会提供所有生产用的IP以及一些通用功能的IP库,用户在搭建自己设计时可以用到。这些IP集成模块可以轻松的导入Xilinx Vivado设计工具,所有IP都支持AXI4协议并且可以无缝对接Xilinx提供的IP资源。

2019-02-13 10:53:59 4004

4004 在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在启动时收到Windows错误。相同的安装文件已加载到win7 pc上,MIG IP生成器运行正常。在Win8.1机器上,我

2018-12-07 11:18:46

怎样能使35集成器运行起来?连完电路,三极管导通,35应该通电工作输出高电平才对。为啥工作不了?

2021-10-20 14:06:11

`无线充方案:IP6806 10W过QI认证 全集成 方案概述IP6806 是一款无线充电发射端控制SoC 芯片, 兼容WPC Qi v1.2.4 最新标准,支持 A11 或A11a 线圈,支持5W

2020-01-17 14:26:50

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

XILINX ISE 14.7,我想建立一个工程,里面要调用之前别人的包含SRAM IP核的模块,需要使用.v和.ngc文件,可是不知道那个.ngc文件该怎么使用,是copy到自己工程目录然后在工程里面添加进去吗?为什么加进去后我的工程文件层次就乱了。。。

2015-04-18 14:21:49

下载到板子测试的时候,却得不到输出数据,求大神帮忙看看是否是代码的问题呢?多谢啦library IEEE;use IEEE.STD_LOGIC_1164.ALL;use

2016-12-23 12:53:46

最近收集了一些 xilinx FIFO IP的资料整理了一下拿出来大家分享分享。

2013-05-11 08:36:29

嗨,出于移植和维护的原因,我需要安装Xilinx ISE 10.1 Foundation,完全支持所有FPGA,尤其是Virtex-5 XC5VFX70T。我有这个版本的有效许可证(即注册ID)但我

2018-11-15 11:30:24

Xilinx TCP_IP协议实现

2012-08-17 09:03:39

大家好,我拥有Xilinx Vivavo 14.4和Matlab 2015a,当我试图将两者集成到系统生成器时,我得到的错误是“没有matlab exixting的余地”我该怎么办,请帮助我

2020-05-05 08:09:03

嗨, 我正在寻找一个数字多相上变频器。 我在Altera的应用笔记和设计实例中找到了一些。 只是想知道Xilinx有没有任何应用笔记和系统生成器设计实例?谢谢,将以上来自于谷歌翻译以下为原文Hi,I

2019-01-30 10:08:42

我在Xilinx核心生成器(vivado 2016.2)生成的AsynFifo(独立时钟块Ram,FIFO生成器版本13.1)上遇到了问题。设置如下:输入数据宽度:260输入数据宽度:520问题是当

2020-05-05 17:41:49

`Xilinx系列FPGA芯片IP核详解(完整高清书签版)`

2017-06-06 13:15:16

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

嗨,我在系统生成器2014中使用黑盒子.4在模拟模式下选择vivado模拟器。如果我运行该项目它正常工作,但如果我在系统生成器或黑盒vhdl中更改某些内容,则会出现此错误:Xilinx模块库中发

2018-10-30 11:07:57

本帖最后由 何立立 于 2018-1-9 17:29 编辑

在Microblaze系统中添加用户自定义IP,可以使用Xilinx Platform Studio (XPS) Create

2018-01-09 14:53:42

以及用于约束文件的编辑 Constraint Editor 等。• 综合(Synthesis) ISE 的综合工具不但包括了 Xilinx 自身提供的综合工具 XST,同时还可以集成 Mentor

2018-09-27 09:29:57

介绍ViCANdo工具支持的另外一个功能:XCP解析功能集成。

2020-12-28 07:41:52

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

本帖最后由 lee_st 于 2017-11-2 15:01 编辑

《FPGACPLD设计工具──Xilinx+ISE使用详解》第 1 章 ISE 系统简介

2017-11-02 10:02:32

除了在Xilinx官网上在哪里能下载到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

Logic组件仍在使用中。如果我使用Xilinx / Logicore DMA,请确认它没有使用任何将超时的Northwest Logic DMA系统。如果它不使用和Northwest Logic组件,我将在我能够达到销售时立即订购该板,并且在该板中不存在与以太网相关的另一个问题。谢谢!

2019-10-08 07:54:35

System View公司是一家位于美国加州的早期创业型公司,公司的主要产品和业务是设计开发当今嵌入式系统集成开发所使用的工具,打破传统,推出更加高效便捷的开发工具。近期该公司推出一款嵌入式系统开发工具,命名为“可视化系统集成器(VSI)”。

2019-10-09 07:56:13

设备接口,如 NVMe® 固态盘和主机处理器内置 100G EMAC 硬 IP,用于高速 100G 网络接口DDR4 和 LPDDR4 内存接口协同优化工具和调试方法Vivado® ML, Vitis

2022-11-25 16:29:20

大家好我可以在Matlabwith Vivado上安装Xilinxsystem生成器吗?有了ISE,有一个应用程序调用System Generator Matlab Configuration

2018-12-27 10:57:02

HI, 我正在尝试使用浮点IP在Zedboard上生成一个系统(SoC)(使用VIVADO 2016.4)。由于这个IP具有分层接口,我使用AXI DMA将此ip添加到AXI系统总线。但现在我的问题是如何使用Xilinx SDK检查此IP? (表示如何向IP发送输入以及如何检查输出)。谢谢

2020-05-26 14:04:10

你好,我对Xilinx工具的自下而上合成流程有一些疑问。由于我对这个领域很新,所以我只知道ISE和XST。在我的顶级设计中,我实例化了几个优化的多线程(不是库中的标准乘法器),但我不希望它们在综合

2019-03-22 06:51:51

,它们具有eval和完整版本的IP,但是当您使用设计中提供的tcl脚本创建项目时,它使用NWL IP的eval版本创建项目。我想知道是否有人知道eval版本的实际限制是什么,以及是否可以使用完整版IP的许可证来使用Northwest Logic提供的后端DMA创建新设计。祝你有个好的一天,史蒂夫

2019-09-19 08:25:52

我想使用系统生成器来生成sinc信号。但我不知道在哪里可以获得这个系统生成器?这是xilinx ISE设计工具的一部分。如果是这样,请告诉我如何使用它来生成sinc信号?谢谢以上来自于谷歌翻译以下

2019-01-28 06:37:12

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

您好,我被要求执行序列生成器。我已经用纸做过一切,但我不知道如何在Xilinx上正确创建它。我完成了转换表和输出表。我的输出函数已经用karnaugh等进行了简化。但是当我实现它时,我认为它在

2019-01-10 10:39:50

将Xilinx SDK集成到现有的构建系统中?除了确保ARM工具链二进制文件是可访问的之外,还需要使用像gcc -'s -isystem选项这样的东西来确保交叉编译器的头文件文件在本机标头之前找到。我也

2020-05-20 10:06:37

我想用ip核心生成器实现DCM,但我无法实现设计。我有这个错误。我认为问题出在.ucf档案中。请帮帮我

2019-07-24 12:11:54

大家好!!! 我正在使用xilinx系统生成器实现ofdm。在发送器部分,对于星座映射,我使用的是16位QAM,这是一个matlab文件。通过使用“Mcode块”,我有点将matlab包含

2019-04-19 10:32:12

无线充方案:IP6806 5W过QI认证 全集成概述IP6806 是一款无线充电发射端控制SoC 芯片, 兼容WPC Qi v1.2.4 最新标准,支持 A11 或A11a 线圈,支持5W、苹果

2021-09-11 10:03:44

嗨,视频测试模式生成器IP模块需要一个免费许可证,我已从Xilinx下载,添加到我的许可证文件中,并加载到Vivado for Ubuntu。 TheLicense Manager看到它,但是当我

2019-01-02 14:34:16

5V输入双节串联锂电池升压充电IC——IP2325一、产品简介:IP2325是一款支持双节串联锂电池/锂离子电池的升压充电管理 IC。IP2325集成功率 MOS,采用同步开关架构,使其在应用时仅需

2022-11-18 19:58:20

你能告诉我用户逻辑是什么吗?我理解的是user_logic是vhdl模板的主/从ip实现的?我对吗?无论如何,如果你能详细说明一下,我会很高兴非常感谢您的帮助!!

2019-11-11 13:54:56

。(http://www.xilinx.com/support/answers/54025.html)但是我找不到与我正在使用的完全相同的内存。我尝试过使用xilinx mig(内存接口生成器)ip并创建

2020-04-23 08:44:28

亲爱的Xilinx:光纤通道IP核支持VII pro,V4 FX,它们都有ppc硬核,但自从V5 FXT宣布这么长时间以来,为什么V5 FXT不支持这个核心?V4 FX中的光纤通道IP核可以4Gbps运行,但V5 LXT只能运行2Gbps。谢谢

2020-06-02 12:30:33

IJF编码是什么原理?如何实现IJF编码?采用FPGA和集成器件来实现IJF编码

2021-04-13 06:56:04

使用的人太少了,xilinx就没有做这些加密IP的库,也不提供任何技术支持,除非你自己去折腾。。。除了仿真工具,另外也有一些第三方的EDA的工具可以用于XILINX的FPGA开发。下面是我自己从

2013-03-14 11:49:58

FPGACPLD设计工具——Xilinx ISE使用详解的主要内容:第1章 ISE系统简介第2章 工程管理器与设计输入工具第3章 ModelSim仿真工具第4章 ISE中集成的综合工具第5章 约束第6章

2009-07-24 16:06:58 197

197 Xilinx ISE Design Suite 12.4 现在将更好地帮助您全面提升和改进设计。

Spartan-6 FPGA 将静态功耗削减 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持现已开始投产,可满足即插即用

2010-12-23 21:55:07 1294

1294

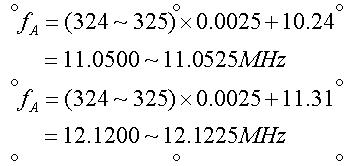

CMOS集成双环合成器

环路的输出频率

2008-04-21 14:32:57 748

748

什么是Application Logic

英文缩写: Application Logic

中文译名: 应用逻辑

分 类: IP与多媒体

解 释: 一个应

2010-02-22 10:17:18 904

904 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 770

770 MIPS和Virage Logic合作提供优化嵌入式内存IP

美普思科技公司(MIPS Technologies, Inc.)和备受半导体业界信赖的IP伙伴Virage Logic 共同宣布

2010-04-07 09:44:26 452

452 通过将第三方IP集成到NI LABVIEW软件中,您可以使用许多为XILINX现场可编程门阵列(FPGA)精调过的算法实现高性能,并且提高代码重用度。LABVIEW FPGA模块为导入外部IP提供了两个方法:组件级知识产权(CLIP)节点和结合XILINX核心生成器的IP集成节点。本技

2011-03-15 13:25:58 90

90 IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit-》Language Template-》C

2012-08-15 15:57:09 35

35 美国加州圣何塞,2014年9月30日 ─ 全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。

2014-10-08 19:24:35 907

907 Xilinx FPGA工程例子源码:Xilinx TCP_IP协议实现

2016-06-07 14:54:57 31

31 Xilinx FPGA工程例子源码:Xilinx 的IP:1024点FFT快速傅立叶变换

2016-06-07 15:07:45 51

51 Synopsys公司发布了新DesignWare 混合IP原型工具包,其集成了基于ARMv8基础平台的虚拟开发工具包(VDK)和DesignWare IP原型工具包。 混合IP原型工具包为软件工程

2017-02-09 03:56:21 295

295 Xilinx针对不同类型的调试IP核,提供了不同的核生成器。本节重点介绍Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro调试IP核ICON、ILA、VIO和ATC2及其属性

2017-02-11 07:14:11 761

761

当ISE调用ModelSim进行仿真的时候,如果在FPGA设计中使用了Xilinx提供的的IP core或者其他的原语语句,ModelSim不添加Xilinx相应的库文件的话,是无法仿真的。

2017-02-11 15:22:37 1274

1274

Express Logic 的 ThreadX RTOS 现已支持 MIPS 64 位 I6400 CPU 2017 年 3 月 14 日 ─ Imagination Technologies

2017-04-10 10:12:49 1573

1573 。 使用Xilinx内核生成器IP函数实现FPGA VI中不同的Xilinx内核生成器IP。LabVIEW使用IP集成节点实现上述函数。函数名称和说明来自于Xilinx数据表。单击Xilinx内核生成器配置对话框的数据表按钮,了解IP内核的详细信息。 选板随终端变化且仅显示FPGA设备系列支持的IP。

2017-11-18 05:54:05 1286

1286 仅支持FPGA设备支持的IP。并非全部FPGA设备系列均支持所有IP。关于FPGA设备支持的详细信息,见IP数据表。单击Xilinx内核生成器配置对话框的数据表按钮,了解IP内核的详细信息。 注: Xilinx提供并维护Xilinx内核生成器IP。由于Xilinx可能不再支持或更新早期版本的IP内核。

2017-11-18 05:55:51 4465

4465 LabVIEW使用IP集成节点方便的整合Xilinx内核生成IP至FPGA VI。按照下列步骤添加Xilinx内核生成器IP至FPGA VI。 1、在支持的FPGA终端下新建一个空白VI,并显示VI

2017-11-18 05:56:22 1746

1746 All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))宣布,将在2月7日- 10日欧洲最大规模系统集成展ISE 2018

2018-02-09 12:55:26 7389

7389 Xilinx是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。

2018-03-23 11:00:29 38729

38729 用户可以使用IP集成器连接IP模块创建复杂的系统设计。通过接口构建基于模块的设计,一般情况下接口包含多个总线和大量的信号线。因此,为了方便在硬件上调试那些包含大量接口的设计,就需要验证设计的接口连接。

2018-04-18 15:28:24 2978

2978

在xilinx下每种操作其实都对应着一种工具,逻辑综合,网表与constraint fie的合并,布局布线等等。下面就对各个工具做一个总结。 1、XST(Xilinx Synthesis

2018-05-28 11:42:14 8910

8910 Xilinx(赛灵思)是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual

2018-11-26 08:21:00 2022

2022

通过探索答案,文档或使用社区论坛与同行联系,在Xilinx支持站点上查找解决方案。

2019-01-16 07:40:00 2383

2383 了解Vivado中的Logic Debug功能,如何将逻辑调试IP添加到设计中,以及如何使用Vivado Logic Analyzer与逻辑调试IP进行交互。

2018-11-30 06:22:00 3107

3107 即将推出的Xilinx ST 2059 IP内核的早期技术演示展示了将时序和同步功能集成到ST 2022网络中,并将针对KC705Kintex®-7评估平台。

2018-11-28 06:19:00 2887

2887 Xilinx Logicore IP直接数字合成器(DDS)编译核心采用Axi4流兼容接口,实现高性能、优化的相位生成和相位-正弦电路。

2019-09-09 08:00:00 20

20 xilinx logicore™ip块内存生成器(bmg)核心是一个高级内存构造函数,它使用xilinx fpgas中的嵌入式块ram资源生成面积和性能优化的内存。用户可以快速创建优化的内存,以利

2019-10-30 08:00:00 5

5 苹果似乎正在为 Mac 用户准备新版 Logic Pro X 并让其支持 Live Loops 功能。事实证明该功能在 iPad 版的 Garageband 中很受欢迎,现在苹果希望将这种体验扩展到 Logic Pro 用户身上。

2020-03-30 14:58:47 1872

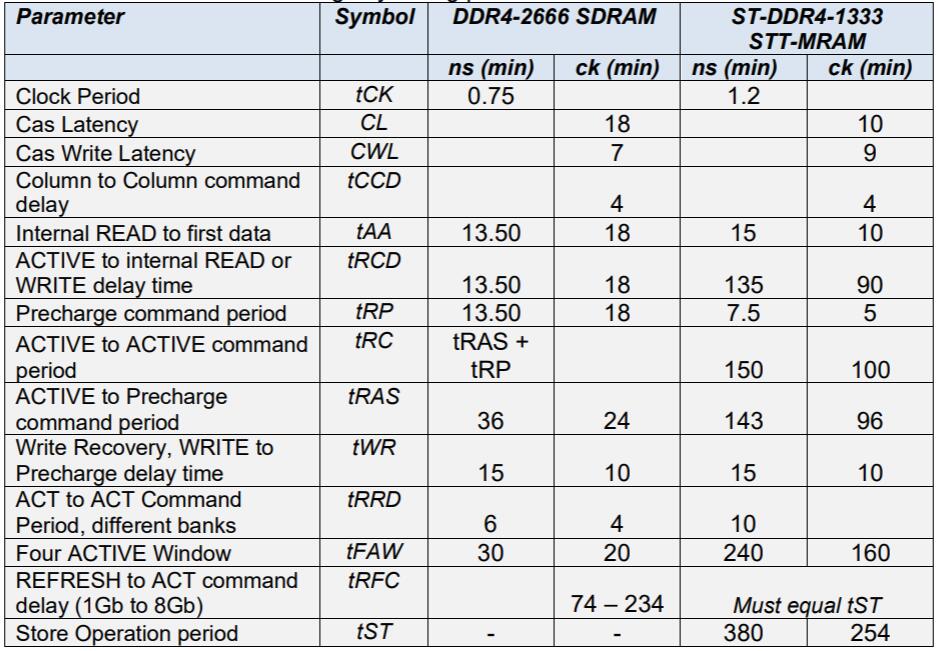

1872 DDR对于做项目来说,是必不可少的。一般用于数据缓存和平滑带宽。今天介绍下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 开发工具:Vivado

2020-11-26 15:02:11 7386

7386

Xilinx FIR IP的介绍与仿真 1 xilinx fir ip 简介 1)符合 AXI4-Stream 的接口 2)高性能有限脉冲响应(FIR),多相抽取器,多相内插器,半带,半带抽取

2020-10-30 12:29:01 511

511 Xilinx LogiCORE IP块内存生成器(BMG)内核是一种高级内存构造函数,它使用XilinxFPGAs中的嵌入式块RAM资源生成区域和性能优化的内存。

2020-12-09 15:31:00 22

22 本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2090

2090

没有加水印,被人捡了个便宜,吃一堑长一智,以后注意保护自己的劳动成果。没办法自己重新写一下吧。 目前vivado已成为Xilinx FPGA开发的主流工具,而ISE基本很少人在用了。vivado是一款优秀开发FPGA开发工具,虽然存在很多bug,但是集成了这么多功能以及能够

2021-03-29 14:09:52 16373

16373

为了使设计人员能够快速集成ST-DDR4支持,该过程从Xilinx Vivado开发环境中生成的现有8Gb DDR4 SDRAM-2666存储器接口生成器(MIG)开始。

2022-11-17 14:35:21 668

668

Xilinx LabTools工具是Xilinx FPGA单独的编程和调试工具,是从ISE或Vivado中独立出来的实验室工具,只能用来下载FPGA程序和进行ILA调试,支持所有的FPGA系列,无需

2023-03-28 10:46:56 4755

4755 DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2023-07-24 11:23:29 1728

1728

IP6822 全集成15W无线充方案soc 支持PD快充输入BPP认证ip6822规格书

IP6805U IP6806 IP6822 IP6808 附相关原理图/规格书/BOM等现ip

2023-08-24 10:37:47 907

907

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 529

529

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

Xilinx LogiCORE IP视频定时控制器内核是一款通用视频定时生成器和检测器。该内核可通过完整的寄存器集进行高度编程,从而控制各种定时生成参数。这种可编程性与一组全面的中断位相结合,可轻松集成到处理器系统中,实现对模块的实时系统控制。视频定时控制器提供一个可选的AXI4-Lite兼容接口。

2023-10-16 11:06:40 292

292

正在加载...

电子发烧友App

电子发烧友App

硬声App

硬声App

795

795 2887

2887

2883

2883

5528

5528

4004

4004

评论