Xilinx ISE Design Suite 12.3 – 现已面市!

2010-10-09 15:22:09 1235

1235 电子发烧友网核心提示 :Xilinx ISE 14.2安装指南,包括Xilinx ISE 14.2软件下载、Xilinx ISE 14.2软件安装、Xilinx ISE 14.2相关产品介绍、Xilinx ISE软件激活、Xilinx ISE14.2软件启动和Xilinx ISE 14.2新建工

2012-10-31 11:59:13 61264

61264

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

16500C逻辑分析系统的状态和时序分析器

2019-02-28 13:26:11

软件化广播接收机使用XILINX的xc7k325t,PLL出400MHZ时钟作为时分5个频道的clk;每个频道80MHZ采样;编译后slack为-2.702;DATAPATH DELAY (FF

2018-10-11 22:49:10

我是Xilinx和FPGA的新手。 我有一个Spartan3A入门套件。我的困惑在于ISE Project Navigator和Xilinx Platform Studio。有什么不同? 我知道

2019-01-14 12:39:27

“TS_ADC2_CLK_N”= PERIOD“ADC2_CLK_N”“TS_ADC1_CLK_N”PHASE +2 ns;在某一点上,一个时钟源的一些数据到达一个由另一个的+时钟计时的寄存器。时序分析器在这里报告

2019-07-29 12:51:47

有没有哪位大神对ISE的时序约束比较熟悉,尤其是多周期约束这一块。在Quartus中使用比较简单,而且相关资料也比较多,但是ISE中的资料好像不是那么多,而且也没有针对具体例子进行分析。官网上给出

2015-04-30 09:52:05

我使用ISE 13.4对设计的代码进行逻辑综合和布局布线等。写的测试文件调用了一个RAM IP核,见图1。其中test_HRV_top为测试文件,调用了RAM_fangzhen这个IP核和设计顶层

2015-08-29 16:55:16

XILINX ise打不开程序请问是什么原因?

2019-02-28 06:02:50

XILINX FPGA/CPLD ISE下载教程 第一章 XILINX FPGA/CPLD ISE下载教程——下载.bit文件第二章 XILINX FPGA/CPLD ISE下载教程——烧录Flash 图文详细资料!

2019-08-15 00:32:31

《FPGACPLD设计工具──Xilinx+ISE使用详解》

2018-01-12 15:04:43

Xilinx ISE 13.2 licenses 直接覆盖.

2011-09-30 16:08:01

我在实验室计算机上安装Xilinx 11.2版时遇到问题。我从Xilinx设计工具网站下载了用于32位Windows系统的11.2 ISE设计套件,我下载的名为

2018-11-21 14:31:55

这些输入外,还需要一个外部时钟来锁存此RGB数据。将此时钟信号运行到PMOD上的通用I / O引脚会在Xilinx ISE中产生Place:1018错误。将错误覆盖到Place:1019警告允许设计实现

2019-05-29 12:35:08

大家好,我正在使用Xilinx ISE 14.7(针对Virtex5,因此没有Vivado),并且遇到了工具的问题,因此更改设计中的信号名称会影响实现,从而影响时序,在某些情况下会略有变化比如说,一

2018-11-02 11:14:38

有人用Xilinx ISE的mig生成ddr2,然后进行调试的吗?如果选择了内含pll,顶层时钟怎么连接

2014-09-15 19:14:41

约束设计与时序分析6.1 概述6.2 时序约束6.3 约束编辑器6.4 时序分析器6.5 本章小结第7章 可编程逻辑器件的高级设计7.1 概述7.2 宏生成器7.3 增量设计7.4 模块化设计7.5

2012-02-27 14:43:30

喜我试图在Xilinx ISE 14.1中使用Xpower Analyzer分析我的设计的功能,以实现virtex6设计我的设计中有一个PLL,它提供20,80,100M o / p频率

2019-04-16 15:25:00

本帖最后由 jzc1610 于 2016-6-15 17:56 编辑

附:xilinx ise 14.7 安装包下载地址(直接打开迅雷,新建任务,复制粘贴链接即可):https

2016-06-15 09:13:23

xilinx ise 14.4套件在安装过程中出现select a MATLAB,,怎么解决啊?

2013-03-20 23:17:04

请问下 现在的 xilinx ise哪个版本好用?谢了!

2012-06-19 10:15:45

嗨,我安装xilinx ise online(网络安装客户端88.8MB)并使用正确的许可证注册。但是,项目显示为附件中的黄线列表。是因为我还是忘了安装一些软件吗?谢谢,Deritha以上来自于谷歌

2018-11-19 14:25:54

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

先生,我想产生一系列连续时间脉冲,将样品转化为冲动,如何在xilinx ise 13,.4中实现。

2020-04-17 07:23:48

分析器是否只假设中间数据是有规律的间隔?或者我该如何以不同的方式表达约束?以上来自于谷歌翻译以下为原文I'm using a deserialization factor of 4 (4 data

2019-06-06 11:49:21

专家好,

CCS调试程序过程中,需要分析下各函数的执行时间,CCS中提供了性能分析器profile

Q1:性能分析器profile是否只能在Simulator下才能使用,Emulator下没有这个功能?

Q2:性能分析器profile的使用方法是否有相应的教程参考?

谢谢

NanShan

2018-06-21 19:20:12

知道“时间分析器”和“planahead”可以帮助我,但我无法理解它的报告。我该怎么做才能解决时间问题。我找不到一些材料来帮助我理解“时序分析”,“代码风格”,“如何纠正时间问题” ','时序收敛'等等

2019-03-18 13:37:27

约束文件(XDC文件),它包含用于时序分析的“create_clock”和“set_input_jitter”约束。在ISE 14.7和Spartan-3 FPGA中,我可以使用称为“时钟向导”的IP来

2019-08-02 09:54:40

的。来获取关于原始的 ISE 设计套件以及 Xilinx 在 Vivado 中对这些开发工具做改进的理由的讨论。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的设备,但是

2021-01-08 17:07:20

1818.8.1 布局布线流程1818.8.2 布局布线的实现1828.8.3 布局布线验证1838.8.4 布局后时序评估1848.8.5 改变分区HDL1858.9 功耗分析1868.9.1 启动功耗分析器

2012-04-24 09:18:46

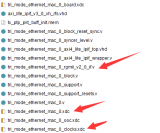

技术10.4.2 基于FPGA的千兆以太网MAC控制器实现方案10.4.3 Xilinx 千兆以太网MAC IP Core10.5 本章小结第11章时序分析原理以及时序分析器的使用11.1 时序分析的作用

2012-04-24 09:23:33

功能完整,使用方便外,它的设计性能也非常好,拿ISE 9.x来说,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟布局、更好的封装和时序收敛映射,从而

2009-11-23 16:13:52

IP核使用: 1、用ISE生成一个PCIE IP核 2、快速使用IP核让电脑识别 3、分析PCIE 接收数据时序,从无到有写一个接收模块 4、分析PCIE发送时序,从无到有写一个发送模块 学习目标

2022-02-14 09:50:22

刚刚接触antlr词法分析器只略看了些基本理论知识,关于做实例就完全不懂了,我想知道他需要什么样的环境和软件,以及软件的下载地址.多谢各位了

2014-11-12 16:29:39

嗨,我们正在尝试使用Vivado工具链手动路由FPGA,并想知道应该使用什么工具来手动路由Virtex 7 FPGA。还可以在Vivado时序分析器工具中指定温度和电压值来估算设计时序吗?我们将如

2018-10-25 15:20:50

描述图形音频分析器 16x32

2022-08-24 06:38:03

我正在研究一种适用于Vedic Maths算法的乘法器。我想对传统乘法器和vedic乘法器的时序延迟进行比较分析。我有spartan 3e和Xilinx 12.1时序分析器。请任何人都可以指导我

2019-07-04 06:36:45

新人请教如何从xilinx官网下载xilinx ise 10.1万分感谢

2013-03-29 16:23:41

我是7系列FPGA的新手。最近开始使用Xilinx VC707板。在此之前,我曾经在Virtex 5上工作。我有一个ISE项目,使用Xilinx ISE和Chipscope使用Vitex 5板进行

2020-07-28 10:18:04

嗨,是否有任何文档可以解释如何使用Xilinx PlanAhead合并EDK和ISE系统? (我阅读了Xilinx EDK概念,工具和技术指南......)关于Zynq-7000 SoC(在

2019-02-22 09:03:57

嗨,我是FPGA编程的新手。我在Xilinx ISE中使用VHDL进行设计。我的综合结果包括:FF,LUT,内存LUT,I / O,BRAM,DSP48,BUFG。我非常感谢能够帮助我解释每个资源

2020-03-24 10:14:15

嗨,我刚刚安装了ISE 14.7系统版本,并将System Generator链接到MATLAB(2014a)。但是当我尝试打开simulink以使用Xilinx System Generator

2018-12-12 10:54:08

我们目前在计算机上安装了Xilinx ISE 10.1,但我们需要CORDIC v4.0,它是新型Xilinx ISE 11.1的一部分。是否可以从Xilinx ISE 10.1升级到Xilinx

2018-11-16 11:48:15

嗨,我在级联模式下使用Xilinx DCM(数字时钟管理器),使用6.144 MHz时钟生成48 kHz时钟。但是,由于我的设计相当大(在区域内),这种配置无法满足时序约束并对整个设计产生影响。因此

2019-03-25 14:09:18

最近在学习FPGA,因为Xilinx家的芯片国内用的最多,故使用了XC6SLX16。但在安装Xilinx ISE时发现无法导入license,网络上寻找了下方法,实测可行,故在这分享给大家。以下

2021-05-17 08:00:00

的写法是一致的,后文将详细明。3.寄存器-寄存器的时序约束寄存器-寄存器的约束,在同步时序电路中,就是周期的约束。对于完全采用一个时钟的电路而言,对这一个clk指定周期约束即可。但是如果采用了多个时钟

2019-07-09 09:14:48

多道脉冲幅度分析器的结构是怎样设计的?多道脉冲幅度分析器的硬件是如何设计的?怎样去设计多道脉冲幅度分析器的相关软件?怎样对多道脉冲幅度分析器的硬件电路进行仿真测试?

2021-04-14 06:31:11

求赐xilinx ise软件!!!

2019-03-19 05:59:29

能,识别可靠的踪迹,检测建立和保持时间的配合,时序分析器不要求用户产生输入激励或测试矢量。虽然Xilinx与Altera在FPGA开发套件上拥有时序分析工具,但在拥有第三方专门时序分析工具的情况下,仅利用

2021-06-24 08:00:01

键盘扫描程序,xilinx提供,设计文件用ISE打开 设计文件

Project Navigator Auto-Make Log File

2009-06-14 09:26:28 37

37 FPGACPLD设计工具——Xilinx ISE使用详解的主要内容:第1章 ISE系统简介第2章 工程管理器与设计输入工具第3章 ModelSim仿真工具第4章 ISE中集成的综合工具第5章 约束第6章

2009-07-24 16:06:58 197

197 可编程逻辑器件cpld 和fpga 以及xilinx webpack 4.2 ISE 的介绍;用xilinxwebpack 4.2 ISE 设计七段译码器的显示.关键词 ASIC Xinlinx

2009-08-15 09:21:52 22

22 ISE时序约束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 转换到TimeQuest时序分析器教程(电子书)

2010-03-23 16:49:43 0

0 xilinx ISE设计套装10.1下载

2010-04-17 16:15:18 1915

1915 使用时钟PLL的源同步系统时序分析一)回顾源同步时序计算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2010-11-03 16:24:44 121

121 Xilinx ISE Design Suite 12.4 现在将更好地帮助您全面提升和改进设计。

Spartan-6 FPGA 将静态功耗削减 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持现已开始投产,可满足即插即用

2010-12-23 21:55:07 1294

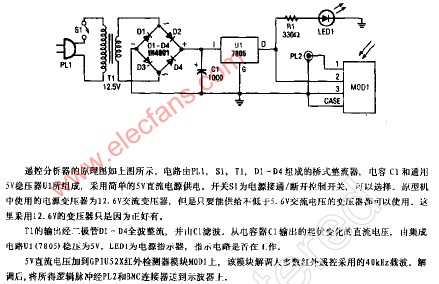

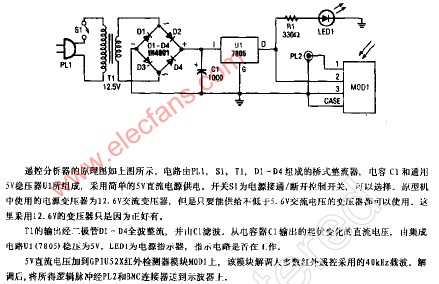

1294 遥控分析器

2009-09-18 14:14:38 456

456

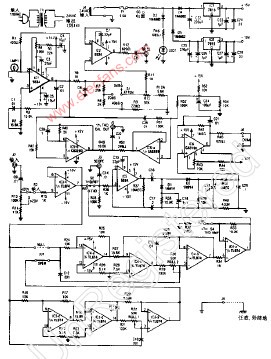

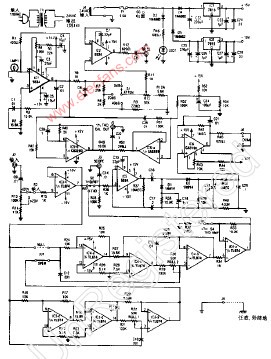

谐波失真分析器

电路包括一个1KHZ的低失真

2009-09-23 14:34:24 757

757

网络分析器,网络分析器原理是什么?

网络分析器

具有发现并解决各种故障特性的硬件或软件设备

2010-03-22 11:25:21 993

993 协议分析器在WLAN中的应用

协议分析器广泛应用于有线网络,成为一类极有用的测试和维护工具。然而,在WLAN领域,这个问题很有可

2010-03-29 17:11:30 483

483 为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时

2011-01-04 11:26:35 1991

1991 Fortify的静态代码分析器(Static Code Analyzer,SCA)是组成Fortify 360的三个分析器之一。SCA工作在开发阶段,以用于分析应用程序的源代码是否存在安全漏洞。这种类型的分析与程序跟踪分析

2011-04-07 20:32:46 22

22 XILINX推出ISE Design Suite 13.2最新版.

2011-07-11 18:22:11 3385

3385

本教程主要是向ISE的初学者描述和演示, 在XILINX的ISE集成软件环境中如何用VHDL和原理图的方式进行设计输入如何用 ModelSim 仿真工具对设计进行功能仿真和时序仿真如何实现设计.

2011-11-01 14:44:07 0

0 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 Xilinx ISE9.1使用全流程中文书

2016-01-18 15:30:43 0

0 xilinx_ise9.01中文教程 xilinx_ise9.01中文教程

2016-02-18 18:16:58 0

0 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 Xilinx-ISE9.x-FPGA-CPLD设计指南合集

2022-03-22 18:03:09 76

76 xilinx-ise 新手教程VHDL的,感兴趣的可以看看。

2016-09-27 15:19:03 77

77 谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

Xilinx ISE使用错误和警告汇总,具体的跟随小编一起来了解一下。

2018-07-13 06:10:00 5848

5848 目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-11-25 01:43:01 1411

1411 员带来了更高的设计生产力。 2)新版 ISE 设计套件与前版有什么区别? ISE设计套件首次提供了“智能”时钟门控技术,可将动态功耗降低多达 30%。针对加密、数据路径和计算密集型设计,甚至还能进一步降低功耗。新套件还提供了基于时序的高级设计保存功能、符合

2018-07-02 06:20:00 897

897 详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

xilinx的ise的使用流程,简单介绍

2018-06-06 13:46:00 3432

3432 了解有关作为英特尔®图形性能分析器一部分的资源历史记录功能的更多信息

2018-11-12 06:40:00 2241

2241 FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 1894

1894

本文档的主要内容详细介绍的是xilinx ISE的视频教程免费下载。

2020-03-23 08:00:00 8

8 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 这个命令指定clock之间是异步关系,时序分析时会完全ignore这些clock之间的path。

2022-12-12 09:49:11 1725

1725 时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息

2022-12-28 15:18:38 1893

1893 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 768

768 很多人询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间

2023-05-29 10:06:56 372

372

基于RGMII时序广泛应用于以太网通信中,基于Xilinx的三速以太网时序分析,不同的Xilinx系列方法不一样

2023-07-07 14:15:01 2952

2952

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析不通过的原因可能有以下几个方面: 1. 读地址同步在写时钟域时序分析未覆盖完全 在时序分析时,可能

2023-10-18 15:23:55 312

312

电子发烧友App

电子发烧友App

评论