1 UART原理

串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。数据在一根数据线上一位一位传输,每一位数

2010-08-02 09:37:50 2476

2476

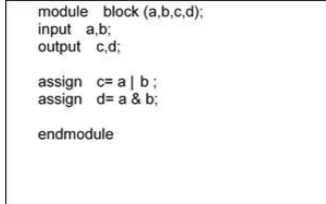

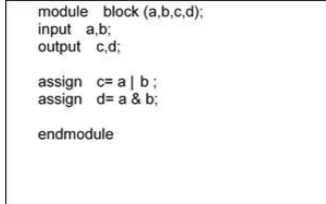

Verilog的基本设计单元是“模块”(block)。一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能,即定义输入是如何影响输出的。

2019-06-26 15:30:40 11375

11375

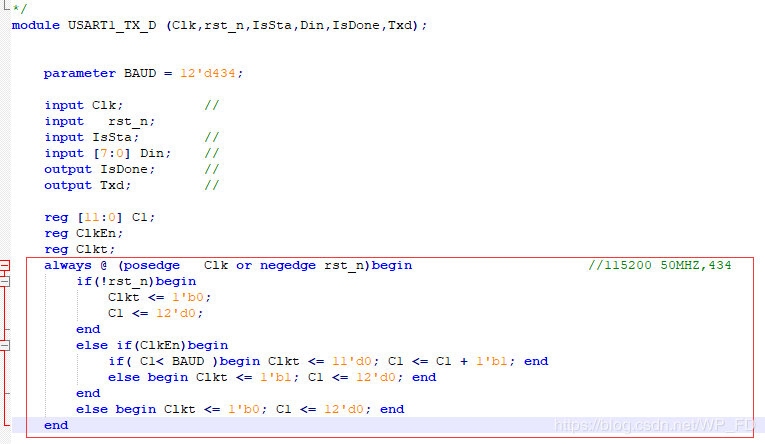

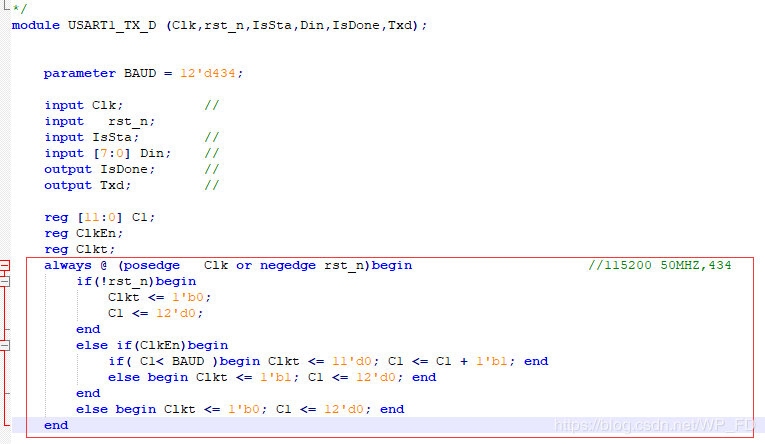

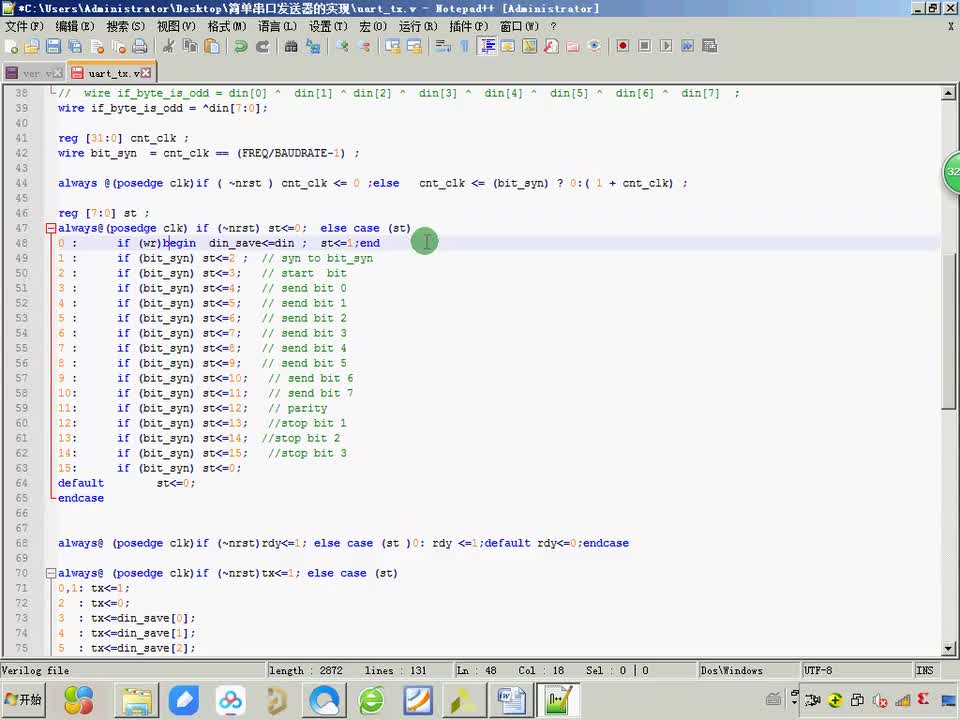

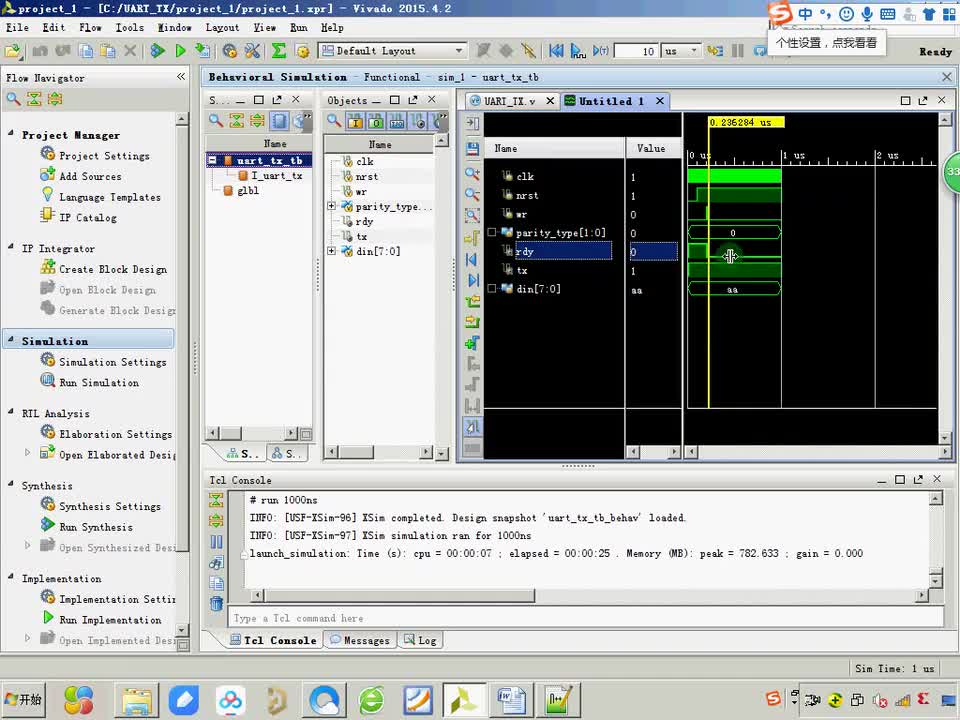

在 ZYNQ进阶之路2 中我们讲解了PL端PWM呼吸灯的设计,本节我们讲解PL端实现串口UART的发送设计; 首先新建一个串口发送的工程,工程建立在ZYNQ进阶之路1中已经讲述,这里不再累述; 下面

2020-11-25 17:26:21 3067

3067

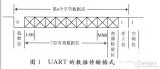

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UART。它将要传输的资料在串行通信与并行通信之间加以转换。作为把并行输入信号转成串行输出信号的芯片,UART通常被集成于其他通讯接口的连结上。

2023-01-05 09:48:46 2395

2395 特权同学的《FPGA/CPLD边学边练---快速入门Verilog/VHDL》中的UART串口收发实验发送数据和接收的数据不一致。在每个有效数据的后面都会多两个数据。比如发送的有效数据是:FF。则

2017-11-30 09:25:44

Verilog实现接收的数据进行发送。

2017-05-19 23:03:45

今天学习了UART的相关知识,完成了用上位机输入字符串然后在虚拟终端上进行显示。首先应该将设I|O口的功能设置为UART,具体有PINSEL来实现。然后是UART的初始化,主要要先是DLB=1,即另

2013-11-29 21:13:23

1.1 FPGA双沿发送之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿发送之Verilog HDL实现;5)结束语。1.1.2 本节

2021-07-26 06:20:59

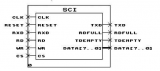

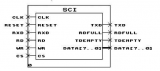

`UART 主要由 UART 内核、信号监测器、移位寄存器、波特率发生器、计数器、总线选择器和奇偶校验器总共 7 个模块组成,如图 5-5 所示。图 5-5 UART 实现原理图UART 各个模块

2018-10-18 09:51:47

实例通过IIC接口定时读取RTC中的时、分、秒寄存器,同时将时、分、秒数据通过UART发送到PC上的串口调试助手进行实时的显示。 2 模块划分本实例模块划分如图所示。●Iic_controller.v

2016-04-05 11:57:20

本帖最后由 mr.pengyongche 于 2013-4-30 03:27 编辑

dsp设计100问(之二)[url=www.7773.cc]

2011-10-30 22:10:12

UART 内核模块是整个设计的核心,所以它也是整个设计中最为复杂的模块。由于 UART 内核模块的整体结构比较复杂,下面的内容将从模块接口、状态机设计和实现代码 3 方面介绍UART 内核的实现方法

2018-10-24 09:58:36

做完相应修改即可实现单次将内存缓冲区数据以DMA方式通过UART0发送出去,效果如下。此外,如果想周期性触发或者条件性触发,则只需再相应位置添加“DMAMUX0_CHCFG0

2015-01-19 14:33:36

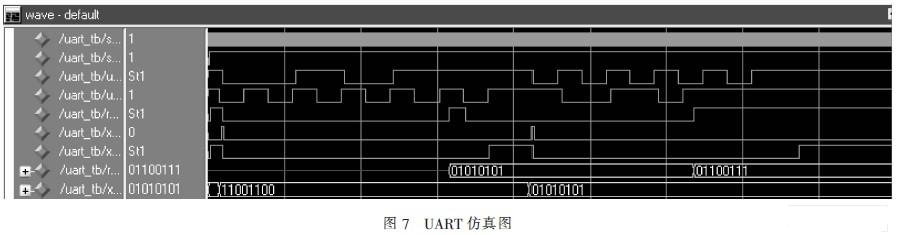

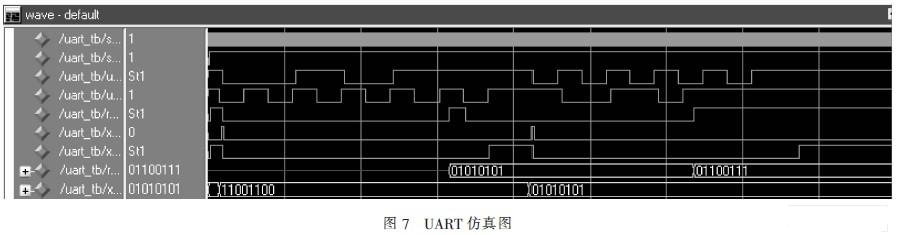

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA片上UART的设计,给出了仿真结果。关键词:通用异步收发器;串口通信;现场可编程逻辑器件;有限状态机

2019-06-21 07:17:24

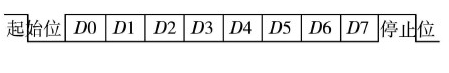

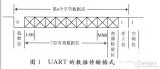

低电平)、8 位数据位、偶校验、停止位(1 b 高电平) , 波特率可调。 2 波特率发生模块 设计的UART 的接收和发送按照相同的波特率进行,波特率可以通过接口模块的总线接口进行设置

2015-02-05 15:33:30

从零开始学习Z-Stack之二欢迎研究ZigBee的朋友和我交流。。。

2012-08-12 22:02:22

本人对于uart串口通讯理解比较混乱,不知道设计的uart接收模块和发送模块应该怎么连接,串口通信是把串行数据接收,然后经过接收模块转换成并行数据,然后再经过发送模块一位一位发出去吗?还是说,串行

2017-12-18 10:47:28

如图所示在uart中怎么用verilog实现输出A转换到a

2019-10-16 16:26:11

//;=================================================================*//; 模块功能说明: UART Transmit

2014-07-08 23:08:28

跪求各位大神有没有基于verilog HDL的高速对数运算模块设计的CORD IC算法实现自然对数运算的代码

2016-03-10 12:39:28

串行通信的工作方式有哪些?如何实现Verilog串口发送及接收一个字节数据呢?

2021-11-11 06:48:39

怎么实现STM32 UART HAL数据发送?

2021-12-14 07:18:54

的按钮,电话应用程序将数据通过蓝牙发送到模块,模块将uart发送到目标。目标响应,模块从uart接收数据并将数据发送回电话。当然可以。

2020-04-20 10:07:50

大家好,我的问题是,我想发送一个完整的数组由250个整数元素(这意味着它的大小是1000),通过UART1端口在我的PIC32 MX795F512H。下面的代码显示了我的UART的初始配置

2019-03-12 15:12:37

发烧友们好,我正在开始学习fpga的知识,现在寻求一个基于verilog的uart程序,要求是初始位一位,终止位一位,数据位8位,实现回环功能。大家能帮助一下我吗?

2020-05-10 22:53:19

请问Verilog怎么实现UART/RS232/RS485收发自动校调功能,降低接收误码率?

2021-06-21 07:27:16

UART 4 UART参考设计,Xilinx提供Verilog代码 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 本文介绍了I2C总线规范,并根据该规范对I2C进行模块化设计,用Verilog HDL 语言对每个模块进行具体描述,并通过模块之间的调用,基本实现了I2C的主机从机的发送和接收功能。

2009-06-15 10:44:03 144

144 文章介绍了一种采基于FPGA 实现UART电路的方法,并对系统结构进行了模块化分解以适应自顶向下的设计方法。采用有限状态机对接收器模块和发送器模块进行了设计,所有功能的

2009-08-15 09:27:55 46

46 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。UART 的波特率可设置调整,工作状态可读取。系统结构进行了模块化分解,使之适应自顶向下(Top-Down)的设计

2009-08-21 11:35:03 52

52 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 简述了I2C总线的特点;介绍了开发FPGA时I2C总线模块的设计思想;给出并解释了用Verilog HDL实现部分I2C总线功能的程序,以及I2C总线主从模式下的仿真时序图。

2009-10-19 10:49:16 104

104 本文设计了一种基于 FPGA 的UART 核,该核符合串行通信协议,具有模块化、兼容性和可配置性,适合于SoC 应用。设计中使用Verilog HDL 硬件描述语言在Xilinx ISE 环境下进行设计、仿真,

2009-11-27 15:48:51 17

17 IO模拟UART实现

本应用用于扩展UART端口,在单片机自带的UART口不够用的情况下,使用GPIO和定时器实现模拟UART通信。可增加两个模拟的UART模块。

2010-03-26 09:20:40 68

68 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。首先阐述了UART 异步串行通信原理,然后介绍了实现UART异步串行通信的硬件接口电路及各部分硬件模块,以及用硬件

2010-08-06 16:24:13 55

55 用Verilog实现8255芯片功能

2010-11-03 17:06:09 144

144 摘 要 :UART是广泛使用的串行数据通讯电路。本设计包含UART发送器、接收器和波特率发生器。设计应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2009-06-20 13:14:52 982

982

C8051F310设计的UART扩展实现

UART数据发送协议作为一种简单的数据发送协议,被大量的使用在当前各种数字外设的数据传输上。但是现在的PC机存在无UART接口或接口较

2010-05-27 10:15:41 2452

2452

Name : uart // File Name : uart.v// Function : Simp

2010-06-05 12:12:03 6236

6236 MAX3109先进的双通用异步接收发送器(UART)的有128字的接收和发送先进先出(FIFO),它一个高速SPI™或I ² C控制接口

2011-04-15 10:17:32 1768

1768

本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47:37 3479

3479

在xo640上实现一个简单的Uart,能够解析串口数据,并在寄存器中存储,用FIFO实现数据的传递。那么后期可以通过开发板上的串口经CPLD访问各种数据。比如PC=CPLD=EEPROM等等,极大方便后期

2011-08-05 16:54:46 1741

1741 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 57

57 数字系统设计:VERILOG实现 (第2版)

2015-11-30 10:21:33 0

0 STM32 UART 发送数据丢失最后一个字节

2015-12-04 15:10:46 0

0 verilog语言开发的串口模块程序,测试可用。

2015-12-25 10:25:19 5

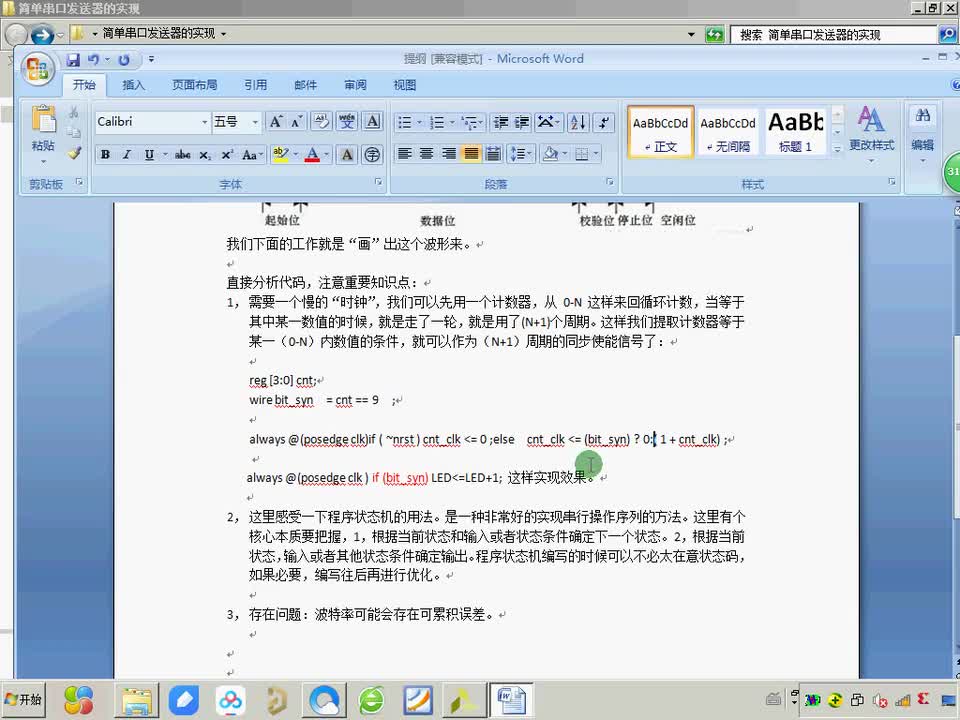

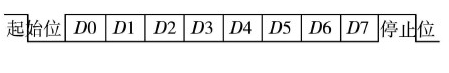

5 异步串行数据的一般格式是:起始位+数据位+停止位,其中起始位1位,8位数据位,奇校验、偶校验或无校验位;停止位可以是1、2位,LSB first: 2.接收原理: 由于UART是异步传输,没有传输

2017-02-09 09:41:11 778

778

将AD采集的结果发送到串口,Verilog程序

2017-04-05 11:20:37 0

0 NiosⅡ的UART设计与实现

2017-10-31 15:09:03 17

17 Verilog是描述复杂的硬件电路,设计人员总是将复杂的功能划分为简单的功能,模块是提供每个简单功能的基本结构。

2017-11-20 16:49:36 5370

5370

使用Verilog描述硬件的基本设计单元是模块(module)。构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。模块被包含在关键字module、endmodule之内。实际的电路元件。Verilog中的模块类似C语言中的函数

2017-12-08 17:20:57 9710

9710 和UART优缺点的基础,提出了一种基于FPGA采用硬件设计HCI-UART的实现方式。本设计在Quartus II 9.0集成设计环境下,采用硬件描述语言Verilog分模块设计完成,设计经过Modelsim 6.4a仿真与验证。

2017-12-11 13:22:51 10881

10881

STM32 UART_发送数据丢失最后一个字节

2018-04-10 11:23:41 3

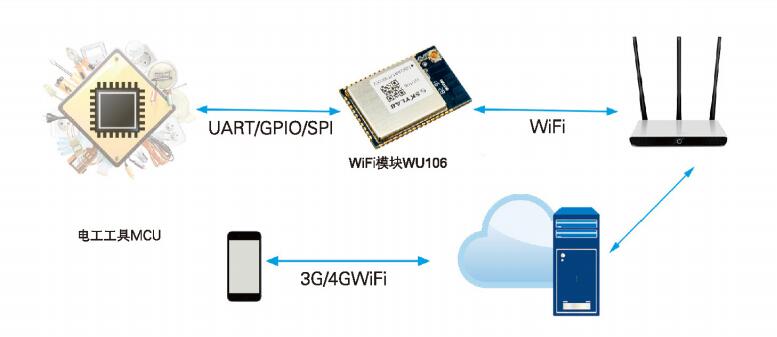

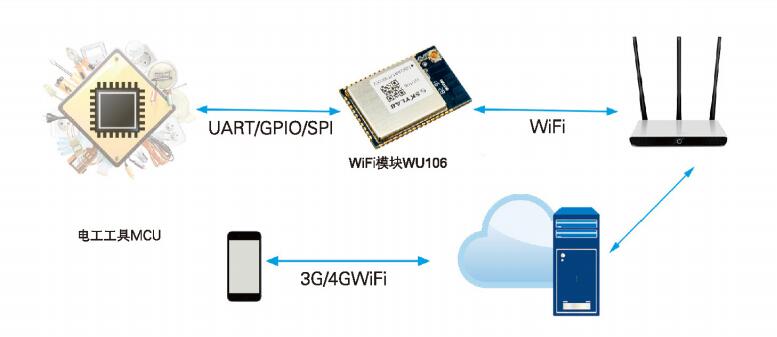

3 栈和IEEE802.11协议栈,能够实现用户串口到无线网络之间的转换。UART接口WiFi模块UART接口WiFi模块是基于UART接口的符合WiFi无线网络标准的嵌入式模块,内置无线网络协议IEEE802.11

2018-08-09 19:01:00 6699

6699 实现RS-232电平和TTL/CMOS电平转换可以用接口芯片来实现,实现数据的串行到并行转换用的是UART,它们是实现串行通信必不可少的两个部分。虽然目前大部分处理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

本文档的主要内容详细介绍的是常用模块的Verilog HDL设计详细资料免费下载。

2018-10-16 11:12:54 20

20 字符发送的过程描述:在UART的发送过程中先将数据输入到发送数据寄存器中(TDR)此时(TXE)被硬件置1,之后TDR寄存器将数据串行移入到发送移位寄存器中,将数据在TX端口发送,此时(TC)被硬件置1。发送与接收是逆过程。

2018-11-08 16:59:25 8795

8795 TCP/IP协议栈,能够实现用户串口或TTL电平数据到无线网络之间的转换。串口WiFi模块工作方式分别是透传模式和命令模式,透传模式下,不管发送什么数据给模块,模块都不会进行处理(退出透传模式的相关指令

2019-01-14 09:27:02 9728

9728

接收控制模块与发送控制模块内部都有一个波特率时钟产生模块(BuadRate_set),用于将电路输入时钟(clk)进行分频产生波特率时钟,用于接收和发送数据控制。

2019-02-04 11:21:00 3596

3596

UART(UniversalAnynchrONousReceiverTransmitter,通用异步接收发送器)是广泛应用的串行数据传输协议之一,其应用范围遍及计算机外设、工控自动化等场合。虽然

2019-08-30 15:05:04 1410

1410

UART(UniversalAnynchrONousReceiverTransmitter,通用异步接收发送器)是广泛应用的串行数据传输协议之一,其应用范围遍及计算机外设、工控自动化等场合。虽然

2019-09-03 09:01:10 2011

2011

UART需要使用DMA发送吗?

2020-03-07 16:57:28 6537

6537 HDL和VHDL的使用比率大概是80%和20%,在中国,大多数电子行业企业都采用Verilog。而模块化的设计让Verilog HDL语言具有思路清晰、逻辑关系明确、可读性强等特点,模块化的设计在 Verilog HDL语法设计中也成为主流。

2020-03-25 08:00:00 4

4 的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 15:51:05 7

7 的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

10 本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

2022-02-08 15:04:08 1966

1966

本教程解释了如何在基于Verilog的设计中包含Altera的库模块,这些设计是使用Quartus R:II软件实现的。

2021-01-22 15:34:12 4

4 FPGA逻辑设计中通常是一个大的模块中包含了一个或多个功能子模块,verilog通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接,有利于简化每一个模块的代码,易于维护和修改。

2021-04-30 09:30:45 25

25 1、 关于如何在VHDL模块调用一个Verilog模块 在VHDL模块声明一个要与调用的Verilog模块相同名称的元件(component),元件的名称和端口模式应与Verilog模块的名称和输入

2021-04-30 14:06:04 8673

8673

选的是一个周期高电平,也可两个)(无校验位) 1、prescale是完成一个bit需要主时钟计数的次数(其和主时钟以及波特率之间的关系参考网上文章) 2、进入uart模块的异步信号,最好使用提供的同步器同步 3、异步复位信号最好使用提供的同步器同步 4、波特率任

2021-05-27 18:05:00 2174

2174 基于FPGA的UART模块设计与实现介绍说明。

2021-06-01 09:43:30 19

19 FPGA设计中DAC控制的Verilog实现(单片机电源维修)-该文档为FPGA设计中DAC控制的Verilog实现资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-26 12:18:48 18

18 MCU-串口发送实现例程仓库:https://gitee.com/ll0_0ll/MCU-UART1.串口发送寄存器为空中断+RingBuff初始化一段内存空间作循环队列发送数据时,先将数据放到循环

2021-10-28 12:21:01 10

10 功耗,并且集成了丰富的外设模块,可以满足工业和消费等多种应用。MSP430FR2311中的eUSCI_A0支持UART通讯,本文对此UART模块的寄存器配置进行了详细的分析和计算,以帮助工程师对此

2022-01-11 10:43:11 1727

1727 单片机pic24GPIO模拟uart发送我们经常遇到那种uart资源不够的情况,这时就需要使用gpio来模拟uart资源。下面就是使用两个定时器和两个gpio来完成模拟。‘’’void

2021-11-16 13:51:02 5

5 TMC2225模块UART调试TMC2225模块UART调试硬件连线串口调测TMC2225模块UART调试TMC2225可以通过UART配置相关参数。比较简便的是通过PC的串口进行调测。硬件连线硬件

2021-12-04 16:36:09 34

34 Uart比较简单,所以仅对tx作比较详细的注释,但里面一些内容还是值得新手学习的

2022-07-01 17:08:50 1304

1304 电子发烧友网站提供《USB转UART转换器模块.zip》资料免费下载

2022-07-19 10:46:50 4

4 有人使用STM32H743做产品开发, DMA 传输待发送的数据到 UART 发送寄存器做后续UART通信。在开启D-Cache的情况下,发现UART没法发送更新过的数据。

2022-11-23 09:02:19 951

951 UART协议由三根线组成,Tx,Rx,Gnd即发送、接收与地,不包含时钟线,属于全双工异步串行通信协议。

2022-12-15 12:10:46 590

590 实现一个在ARM中通过APB总线连接的UART模块(Universal Asynchronous Receiver/Transmitter),包括设计与验证两部分。

2023-06-05 11:48:38 954

954

和接收部分相反,UART发送数据部分是CPU将需要发送的数据写到发送数据寄存器(TX_DATA),发送模块进行数据的发送。

2023-06-05 15:59:52 1695

1695

433模块是一种常用的无线通信模块,用于实现短距离无线通信。在433模块中,一般有发送和接收两种模式。

2023-06-12 17:41:01 7277

7277 电子发烧友网站提供《UART发送数据丢失最后一个字节.pdf》资料免费下载

2023-08-01 17:57:48 1

1 在芯片设计中,UART(Universal Asynchronous Receiver/Transmitter,通用异步接收/发送器)模块是一个非常重要的外设模块。

2023-10-09 14:10:59 642

642 时,它保持在高电压电平。为了开始数据传输,发送 UART 将数据线从高电平拉到低电平(从 1 到 0)。接收 UART 在数据线上检测到这种从高到低的变化,并开始读取实际数据。通常,只有一个起始位。 数据位:数据位是从发送方传输到接收方的

2023-11-09 17:42:21 263

263 以用来实现与其他外设或者外部设备的数据交互。 然而,在一些情况下,用户可能会遇到UART3无法发送数据的问题。在接下来的文章中,我们将深入探讨这个问题,并提供一些解决方案。 首先,我们需要确定问题出现的具体情况。当UART3无法发送数据时,我们可以逐步排除可能的原因。首先,我们

2024-01-09 10:57:21 344

344 众所周知,序列发送模块可以不需要脚本代码实现测试中特定控制报文序列的发送,该模块多用于循环顺序控制的测试案例中。序列发送模块的常用场景,主要是针对一些新开发的产品需要通过该模块来验证产品功能等等

2024-02-19 14:00:11 114

114

第一部分:简介 1.1 什么是Verilog模块? 在Verilog中,模块是其设计层次结构的基本单元。模块是一个用于实现特定功能的单独的硬件单元。它可以是一个组合逻辑电路,也可以是一个时序逻辑电路

2024-02-22 15:56:25 325

325 Verilog是一种硬件描述语言(HDL),广泛应用于数字电路设计和硬件验证。在Verilog中,模块是构建电路的基本单元,而模块端口对应方式则用于描述模块之间信号传递的方式。本文将介绍

2024-02-23 10:20:32 190

190

电子发烧友App

电子发烧友App

评论