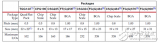

Critical Link公司的某客户需要针对多个应用开发一个扩频无线电收发器。该客户已经开发出一套算法,准备用于对信号进行调制和解调,但他们却缺少构建完整系统的资源和专业知识。客户希望利用软件定义无线电(SDR)系统的灵活性优势。本文将探讨如何基于德州仪器(TI)的OMAP-L138 DSP+ARM处理器与FPGA来实现该系统。平台Critical Link选择其MityDSP-L138F嵌入式系统模块作为SDR的基础,因为该模块不仅具有很强的处理能力,而且可以为客户节省大量的预先设计成本。MityDSP-L138F模块具有一个TI的OMAP-L138DSP+ARM处理器,该处理器集成了一个456MHz ARM9处理内核和一个456MHz TMS320C674x DSP内核。此外,该模块还包含了Xilinx公司的Spartan-6 LX16 FPGA、NAND和NOR闪存以及DDR2存储器。出于原型考虑,该设计使用了TI针对无线电的高速ADC与DAC评估套件。此外,它还需要能够在60MHz采样频率转换的数据转换器。针对A/D转换器,该设计选用了TI的ADS5562。该转换器具有16位精度,可以以80Msps采样速率进行转换。因为扩频无线电需要将信号从背景噪声中抽离,所以高动态范围对于这种无线电来说非常重要。对于DAC,该平台选用了TI的THS5671。这是一款14位125Msps差分电流输出DAC。负责本项目的客户为该系统提供的前端设计如图所示。 [[wysiwyg_imageupload:454:]]图:客户提供的前端设计。数据传送问题许多基于DSP的应用要求具有高速数据传输功能,以使系统能够采集和处理数据,或者将数据传送到外设。通常,数字信号处理器都包含了异步地址/数据总线,以使处理器能够读写外设。这些接口可以满足低速传送数据的要求,但是在高速情况下却会成为瓶颈。OMAP-L138 DSP+ARM处理器具有一个称为外部存储器接口A(EMIFA)的地址/数据总线。EMIFA允许对外部存储器或设备进行异步寻址,并含有若干控制引脚,以满足不同等待状态和传输宽度等等要求。因为该接口具有很强的通用性,所以每次事务处理都可以利用多个时钟周期来完成。例如,最小的读取周期需要每16位3个周期。在100MHz下运行EMIFA,假设总线上没有其他数据,可得到的数据传输速率最大为66MB/s。在总线上进行交错读写会显著地降低传输速率,因为这必须增加额外的转换周期。OMAP-L138处理器还包括了一个更为专用的接口,即通用并行端口(uPP)。该接口专门用来将大量数据连续送入处理器内存或从其中读出。uPP的传输速率为每时钟周期1个数据字(8位或16位);或者针对双数据速率为每时钟周期2个数据字,但是时钟速率必须减半。uPP时钟速率可以高达处理器时钟速率的一半。对于在300MHz下运行的OMAP-L138处理器,uPP时钟可以达到75MHz。这使吞吐量可以达到150MB/s。OMAP-L138处理器实际包括2个uPP接口,每个都可以单独配置。这允许我们为应用建立一个传输端口和一个接收端口,从而消除单一总线上的资源争用问题。从硬件角度看,uPP接口是一种非常简单的同步数据接口。它包含一个时钟引脚、数据引脚和若干控制引脚,用于指明有效数据和起始/等待条件。事实上,该接口可以与一些并行ADC和DAC实现无缝连接。架构因为我们的SDR需要与DSP之间进行高速数据传送,所以我们选择使用uPP端口来实现FPGA接口。我们使用一个端口作为接口的发送端,使用另一端口作为接收端。事实上,该处理系统可以同时进行发送和接收,尽管这并非系统要求。这个功能的优势在于,它允许我们在发送器和接收器之间建立循环,以进行大量的测试和调试工作。对于一个10MHz载波来说,这种调制所需的处理特性,使系统过多地将全部处理任务在OMAP-L138处理器的DSP中完成。在速度较慢的应用中,DSP可以单独满足数据速率的要求,但由于客户要求以更高的速率发送数据,所以我们需要使用FPGA来执行部分处理任务。FPGA尤其擅长以非常高的频率执行重复任务,因此,我们选择在FPGA中执行初始解调和基带处理。这样,我们就可以大量减少DSP中的数据并降低DSP的数据速率。在发送侧,DSP可以预先计算最终的射频信号,以便将有效负载数据的编码时间降至最短。因此,FPGA仅仅将发送波形数据从uPP端口发送到DAC。事实上,不使用FPGA也可以完成这项工作,但是我们在设计系统时仍将FPGA加入,以便在需要时使用。FPGA的双端口RAM中包含一个正弦或余弦查找表,用于合成接收机的本机振荡器信号。FPGA中的乘法器/累加器用于根据要求解调信号。发送处理链当ARM微处理器上的软件向DSP发出传输消息包时,发送过程将会启动。DSP对数据进行编码,使其成为扩频调制序列,并将其编入一个预先计算的已调制正弦波查找表。然后,DSP使用uPP的内置DMA引擎建立一个DMA传输,用以将数据从DSP存储器传送到DAC。FPGA则起到中间调解作用,负责向DAC和uPP提供可编程时钟,用于设置发送采样率。接收处理链接收流程连续运行。ADC样本被同步送入FPGA——通过将输入样本与正交正弦和余弦波形相乘并积分,对数据进行基带处理,从而以较低的数据速率向DSP提供同相和正交样本。这些样本被uPP DMA引擎以DMA方式送入DSP存储器,再由DSP处理剩余的扩频解调处理步骤。一旦信号被解调,得到的数据包将使用TI的DSPLink处理器之间通信库传送回ARM处理器。ARM软件接收解码数据,并通过命令接口将数据呈现给用户。使用FPGA执行接收器初始基带处理能够释放足够的DSP处理能力,从而轻松完成剩余的解调和解码工作。如果系统中的输入信号采样率显著低于60MHz,则DSP可不借助FPGA的力量,独自执行基带处理任务。该系统的初始工作使用了一个低频段(几十或几百kHz)的载频。在初始实施过程中,FPGA仅负责将数据发送至DSP,由DSP执行所有的解调功能。这种方式很奏效,但是无法达到更高采样率应用的要求。通过在FPGA中实施基带处理,我们可以在全采样率下进行数字基带处理和滤波,从而改善系统的噪声性能:这在欠采样下是无法做到的。本文小结该项目实现的原型系统已经为多个应用实施过概念验证。与理想扩频无线电的理论性能相比,该系统的性能非常优异。TI OMAP-L138 DSP+ARM处理器与FPGA的结合,实现了具有出色性能的高性价比解决方案。将DSP的部分处理负载分配给FPGA,使系统可以使用低成本、低功耗的处理器来构建,而不是由GHz级的DSP处理所有工作。uPP接口支持简单的FPGA接口功能,并且与其他可用的DSP接口相比,具有明显的性能优势。使用uPP中的DMA进行数据传送,可以进一步释放DSP资源,将DSP周期用于更加重要的工作。在OMAP-L1x平台中加入ARM处理器后,便可使用嵌入式Linux提供通信基础设施,来管理系统中的用户界面和所有的内务处理功能。此外,使用SD卡、USB驱动器或者以太网连接,可以对系统软件(ARM、DSP和FPGA)进行现场升级。因此,SDR系统的灵活性可以充分满足处理算法的发展要求。David A. Rice技术总监Critical LinkJoseph Coombs应用工程师德州仪器

基于DSP和赛灵思Spartan-6的SDR系统设计与实现

- dsp(343841)

- SDR(50129)

相关推荐

Spartan-6 FPGA是否需要设计中的上电复位电路

您好Xilinx社区,有人能否就Spartan-6 FPGA是否需要设计中的上电复位电路给出明确的答案?在附图中,我们的设计中有这个上电复位电路。然而,我们遇到了电路问题,并决定在我们的设计中将

2019-04-18 10:15:45

Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B的差异是什么

嗨,我想知道是否有关于它们之间[fly]的差异的[/fly]技术文档Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B看起来,差异是芯片修订版

2019-07-02 10:45:31

Spartan-6器件的可用性

有谁知道更多关于Spartan-6 XC6SLX150的可用性?我知道周围有工程样品,但我无法获得最终商业版的任何交货时间。谢谢,罗伯特以上来自于谷歌翻译以下为原文Anyone knows more

2019-05-24 13:15:09

Spartan-6的QDR接口能连接到MCB引脚吗

亲爱的论坛,我正在处理将** II SRAM连接到Spartan-6 FPGA的问题。我不是斯巴达IP核的专家,但我意识到Spartan-6没有预见到的QDR接口。但是我确信它可以做到。我遇到的唯一

2019-05-22 07:16:30

Spartan 6是否支持SDR SDRAM?

嗨,Spartan 6是否支持SDR SDRAM(单数据辐射SDRAM)?在ISE存储器接口生成器中,没有选择SDR SDRAM的选项。有没有办法在斯巴达6中使用SDR SDRAM

2019-04-16 09:33:03

Spartan-3A与Spartan-3AN 低成本谁更有优势?

设计的CCD线阵相机,基于FPGA的,现在选用一款低成本的赛灵思的FPGA芯片,Spartan-3A与Spartan-3AN到底用哪款好呢?

2014-04-02 11:23:40

赛灵思7系列采用FPGA电源模块

。ROHM与安富利公司共同开发赛灵思7系列FPGA及Zynq®–7000 All Programmable SoC的评估套件Mini-Module Plus 用的电源模块。安富利公司已经开发出多款赛灵思

2018-12-04 10:02:08

赛灵思Spartan开发板使用困境记录 精选资料分享

赛灵思Spartan开发板使用困境记录原理图和接口主要是对照核心板的原理图,一般的接法就是赛灵思系列的单片机,连接好电源和下载器,记得预先安好驱动,驱动安装成功与否能够在设备管理器处查看。作者困境

2021-07-13 08:42:10

赛灵思FPGA原理图例子之s3astarter

`赛灵思FPGA原理图例子之s3astarter 赛灵思一向是FPGA领域里的领先者,运用FPGA需要深入的理解它的工作原理,小编亲子整理了s3astarter 的经典fpga原理图分享给电子工程师们。赛灵思FPGA原理图例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

赛灵思FPGA对DLP数字影院投影仪产生了哪些影响?

赛灵思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP数字影院投影仪产品,均采用了赛灵思Virtex®-5 FPGA系列产品。

2019-08-19 07:12:03

赛灵思FPGA该怎么应对内窥镜系统架构的挑战?

什么是赛灵思FPGA?如何帮助内窥镜制造商克服复杂的设计约束,生产出极具竞争优势的产品?如何帮助他们成功构建外形小巧的低功耗内窥镜摄像头、高性价比的摄像机控制单元(CCU),以及多功能、低成本的图像管理设备?

2019-09-17 06:31:55

电子发烧友App

电子发烧友App

评论