电阻,因为物质对电流产生的阻碍作用,所以称其该作用下的电阻物质。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。没有电阻或电阻很小的物质称其为电

2012-03-12 16:46:08 11967

11967 利用FPGA实现双口RAM的设计及应用

概述:为了在高速采集时不丢失数据,在数据采集系统和

2010-04-16 14:08:36 11323

11323

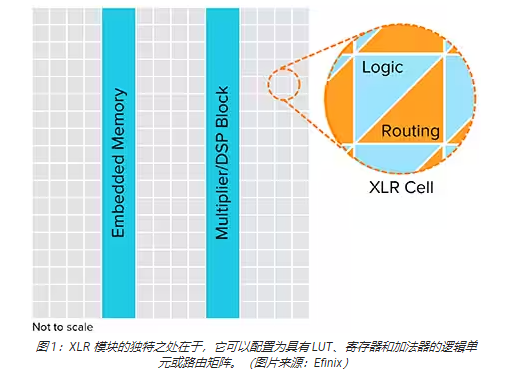

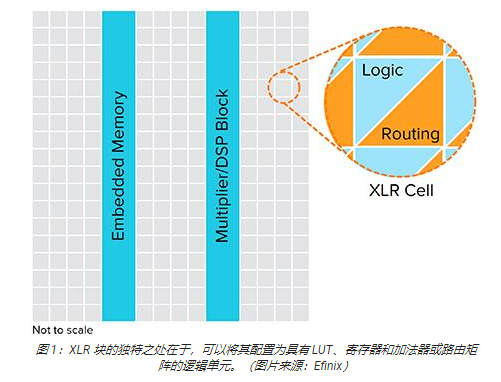

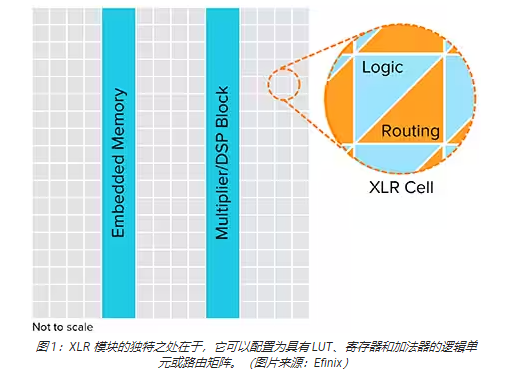

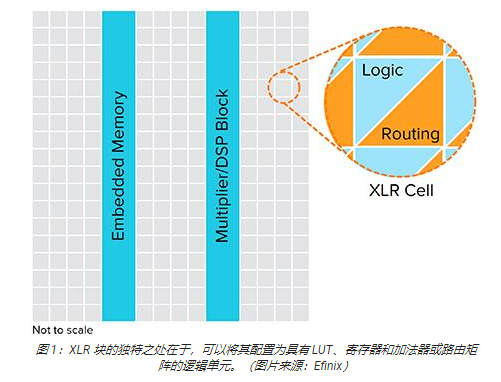

编者按:FPGA 架构的新方法带来了更细粒度的控制和更大的灵活性,以满足机器学习 (ML) 和人工智能 (AI) 的需求。这个由两部分组成的系列的第 1 部分介绍了 Efinix 的一个这样的架构

2023-04-24 14:49:11 8577

8577

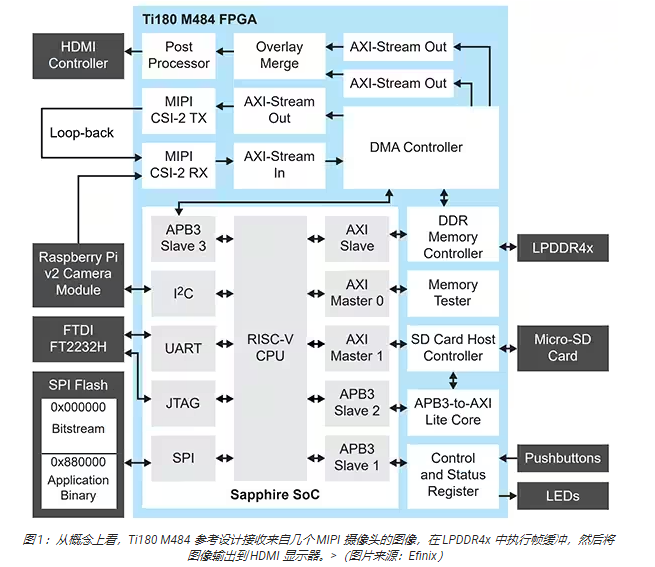

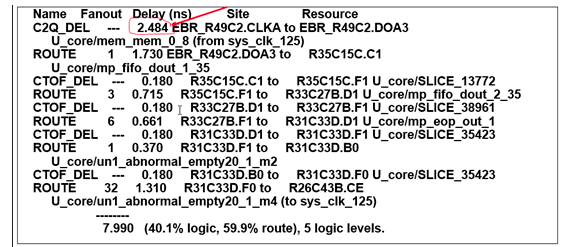

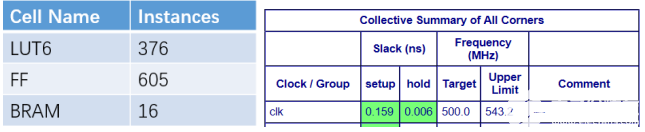

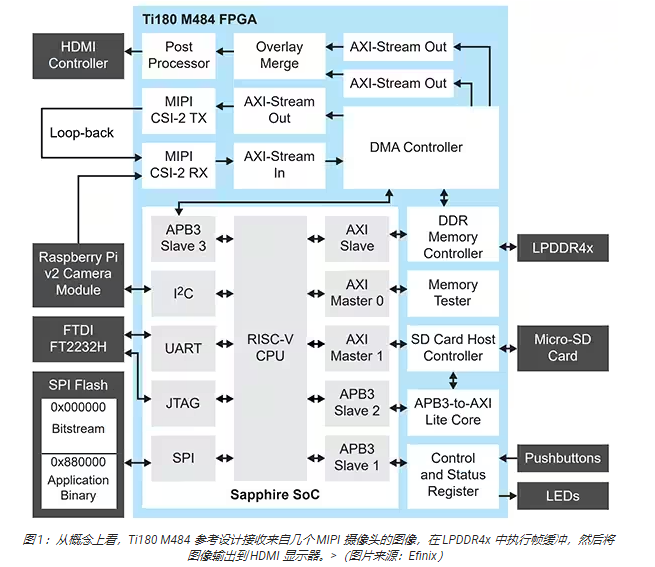

作者:Adam Taylor 编者按:全新的 FPGA 架构方法带来了更精细的控制和更大的灵活性,以满足机器学习 (ML) 和人工智能 (AI) 的需求。本系列文章包括两部分,第 1部分介绍

2023-10-03 14:45:00 318

318

作者:Adam Taylor 编者按:全新的 FPGA 架构方法带来了更精细的控制和更大的灵活性,以满足机器学习 (ML) 和人工智能 (AI) 的需求。本系列文章包括两部分,第 1部分介绍

2023-10-03 14:45:00 430

430

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

【导读】为了满足人工智能、机器学习、无人驾驶、ADAS等应用提出的越来越高的特殊计算需求,Achronix宣布为其eFPGA IP解决方案推出Speedcore定制单元块,这是一种可以将功耗和面积降至最低、同时将数据流通量最大化的解决方案。

2017-10-19 11:28:32 988

988 大打折扣,那么如何突破呢? 与指令集架构不同,数据流架构的显著特点就是依托数据流的流动次序控制计算执行次序,而非指令执行次序,因此把它用在AI上可以让芯片利用率大幅提升,芯片利用率直至逼近 100%。 数据流架构如何提升芯片利

2021-11-26 07:27:00 3965

3965 大家好。我设计并模拟了简单的RTL with Block RAMin Kintex 7。在合成和实现之后,vivado用于功率估计。当我使用分布式RAM时,会正确报告每个RAM的功耗。但是

2019-03-13 14:21:13

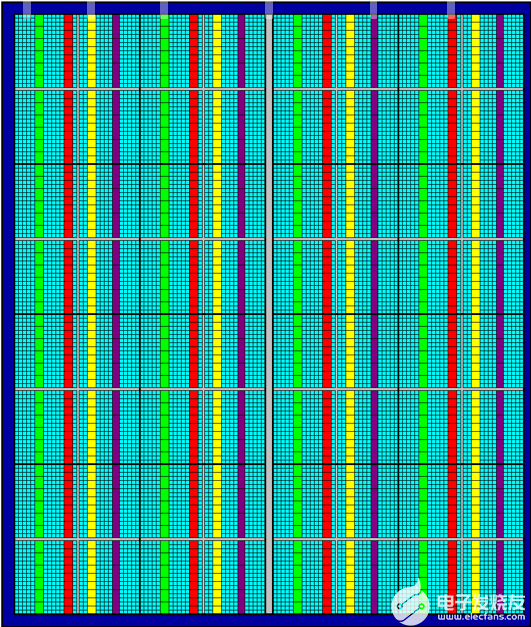

互连线资源(Interconnect)4.嵌入式块 RAM(BRAM)(Block RAM)5.底层内嵌功能单元6.内嵌专用硬核7.致谢FPGA 芯片整体架构FPGA 芯片整体架构如下所示,大体按照...

2021-07-30 08:10:06

各位大神,我最近在做FPGA项目遇到一个问题,我想实现这样的功能:向RAM里写一次数据,再多次读出来,可是我发现IP核里的RAM读第二次的时候RAM数据就清零了,根本读不我写的数据,请问有什么好的解决办法吗?谢谢啦!

2015-06-07 20:31:57

这个接口。核心板电路架构框图如图3.10所示。(特权同学,版权所有)图3.10 核心板电路架构框图另外,有两颗存储器,SPIFLASH用于FPGA器件的上电配置数据存储,我们都知道FPGA是基于RAM

2015-04-20 11:25:47

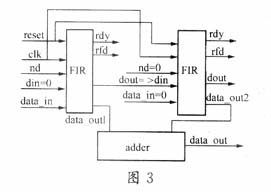

操作的处理流程为:输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM)、单口RAM(SPRAM)、FIFO等

2010-11-01 13:17:36

桥接器和一些简单的UART VHDL代码通过HyperTerm从FPGA到PC获取数据?我在ML605上看到,Xilinx表示需要实现UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

的6个原型中运行良好。当我连接到FPGA上的参考电压IO时,其中2个变为不同的电阻值,因此RAM数据流不起作用。我手动手动测试参考电压引脚以排除出售的问题。在我的工作板上,我在参考电压电阻12k上测量

2019-06-20 15:21:24

。无需CPU直接控制,通过硬件为RAM和IO设备开辟一条直接数据传输通道,将数据直接从一个地址空间复制到另一个地址空间,传输动作本身由DMA控制器实现。作用:为CPU减负,提升CPU效率STM32F4/F7: 2个DMA控制器,16个数据流。每个DMA控制器都用于管理一个或者多个外设

2021-11-03 06:32:58

我今天正在实现FIFO,我想知道FIFOPrimitive和Block RAM实现之间的区别是什么。根据我的理解,它们使用相同的底层RAM原语,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

实现超高效率的传质及传热,安全稳定地实现研发及小试的化工工艺过程。 技术参数:尺寸:70×70×20mm接头尺寸:MUNF 1/4”-28螺丝尺寸:M3温度:-25-230℃压力:0-100bar建议流通量:50-500mL/min用途:用于工业化小试及中试生产中的两相混合,可配合减压阀一起使用。

2018-06-29 10:45:50

NanoEdge™ AI Studio(NanoEdgeAIStudio)是一种新的机器学习(ML)技术,可轻松为最终用户带来真正的创新。只需几个步骤,开发人员就可以基于最少量的数据为其项目创建最佳的 ML 库。

2022-11-29 07:37:53

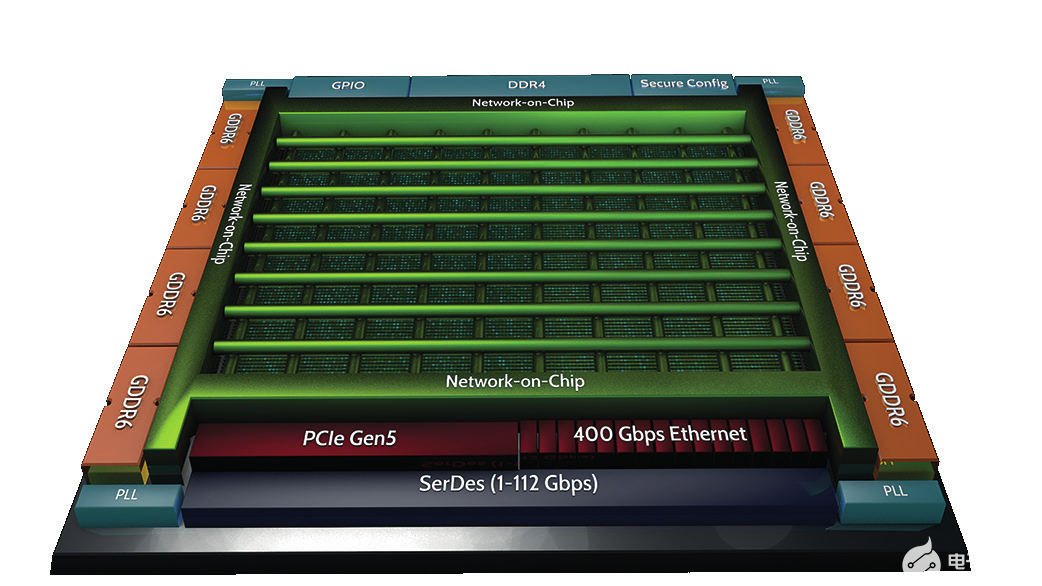

NoC在高端FPGA的应用是什么?NoC给Speedster 7t FPGA带来的优势有哪些?

2021-06-17 11:12:26

嗨,为了调试系统,我需要在系统运行时动态读取Block-RAM内容....我只有JTAG线,我不能在FPGA中制作一个特定的块用于读取内容并通过JTAG等发送它们。我可以使用ISMP 13.2作为

2019-06-11 07:36:08

为“YES”时,我在位源摘要中得到以下信息:信息:Bitgen:341- 此设计使用一个或多个9K Block RAM(RAMB8BWER)。用户定义和默认的9K Block RAM初始化数据需要特殊

2018-10-26 15:06:01

我想知道 X-CUBE-AI 和 NanoEdge AI Studio 在 ML 和 AI 开发环境中的区别。我可以在任何一个开发环境中做同样的事情吗?使用的设备有什么限制吗?

2022-12-05 06:03:15

RAMB16_S18_S18。我使用一个端口进行读取和写入(使用写入启用),第二个端口仅用于读取(通过将WEB设置为0)。两个端口共享相同的时钟。 Block RAM设置为18位宽,但我忽略了奇偶校验数据(即,不使用其输出值

2019-04-24 07:35:02

首先感谢电子发烧友论坛提供的书籍和阅读评测的机会。

拿到书,先看一下封面介绍。这本书的中文名是《AI加速器架构设计与实现》,英文名是Accelerator Based on CNN Design

2023-09-17 16:39:45

CC3200AI实验教程——疯壳·开发板系列AI语音系统架构AI语音识别系统的系统架构如图1.0.1所示。图1.0.1 AI语音系统结构 用户通过语音采集板卡采集到在驻极体端的语音,通过I2S接口

2022-08-30 14:54:38

CC3200AI实验教程——疯壳·开发板系列AI人脸系统架构AI人脸识别系统由7大块组成,分别是摄像头、CC3200、串口调试助手、路由器、公网、服务器、数据库以及百度AI组成。AI人脸识别系统

2022-08-31 16:35:59

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。OV5640提供了一个DVP接口用来输出采集到的图像数据流,本文提供了一个将DVP接口的图像

2020-02-18 19:56:10

充分利用了微软遍布全球数据中心的FPGA基础架构,使用FPGA解决了AI应用中“低延时”和“高带宽”两大痛点,并成功构建了基于软核NPU和自定义指令集的实时AI系统。脑波项目的成功实践,再一次为业界

2019-08-11 04:00:00

设计)。如果不考虑维护性和可测性,调试成本和压力就非常之大。通常,FPGA的大部分架构设计可以采用数据流驱动的方式来实现,例子1,假设一个实现视频解压缩FPGA的设计,输入是无线接口,输出为显示屏。那么输入输出

2019-08-02 08:30:00

我正在运行Spartan 6 block ram的模拟。时钟速度为100Mhz。块ram的写作运作良好。我可以在内存中看到数据。但是当我读取数据时,输出有2个时钟的延迟。在块ram用户guidt中

2019-07-25 08:15:27

上面的基本逻辑单元还不够,多个基本逻辑怎么级联?级联的连接部分怎么可编程?下图是FPGA内逻辑块之间互联的结构图。逻辑块的输入输出通过连接块Connection Block CB和交换块结合级联到其他

2018-08-21 09:50:44

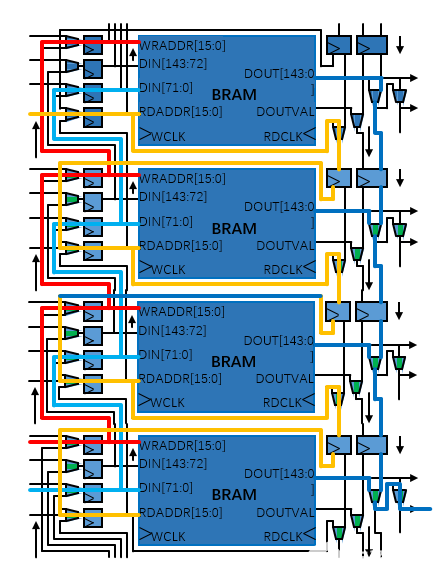

的CDMA加载权重,输入到PL区的Block Ram。原理框图首先,我们创建了整个系统的示意图。有两个 Block RAW 分别用于存储输入特征和权重数据。每个Block RAM 都连接到一个 CDMA

2023-02-21 15:01:58

您好!分布式RAM和Block RAM之间究竟有什么区别?两者都只是芯片内存,对吧?但我不知道两者之间的区别。和..下一个问题.. isaboutMUX ..根据7系列概述,7系列FPGA支持全范围

2020-07-19 06:37:51

在我的一个FPGA类中,我被要求使用coregen创建一个blcok ram(8dx16w),单端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

系统结构与功能: lpc3131外接8k*8双口ram与8G Flash,从双口ram读取数据(来自FPGA),并存至Flash中。问题: 丢数据,系统速度远低于ram的读速与Flash的写速度。双

2011-08-04 11:05:31

一、查找表LUT就是查找表,对于4输入的LUT而言,实际上就是4位地址位,一位数据位的存储器,能够存储16位数据,所以我们在FPGA设计中可以用LUT组建分布式的RAM。这样也可以解释我们在设计中

2021-07-28 08:42:17

问题没有解决。由于是第一次使用双口RAM还不是很了解,其中左侧的数据和地址线以及控制接口全部接到FPGA的I/O口,如果右侧的所有信号线也全部接到USB控制芯片的话会出现管脚不够用的情况。希望各位大神给只只招,谢谢!

2014-04-16 21:14:56

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

的注意,如果能有意识地利用这些原则指导日后的设计工作,将取得事半功倍的效果乒乓操作“乒乓操作”是一个常常应用于数据流控制的处理技巧.乒乓操作的处理流程为:输入数据流通过“输入数据选择单元”将数据流等时分

2020-05-01 07:00:00

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。1.实验原理Xilinx

2021-01-07 16:05:28

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我们如何使用Virtex-4 FPGA的Block-RAM来存储矩阵/ Vector的内容。例如,如何在BRAM中存储矢量A = [1 2 4 5 6 7 9 3]?OR矩阵B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我对在 STM32 上使用 ML 和 AI 很感兴趣,在花了一些时间查看 ST 文档后,我认为使用 NanoEdge AI Studio + ST 板是帮助我理解事物的最快方法。据我所知,ST

2022-12-06 07:35:35

大家好,我有FPGA virtext -5 ML510板,我想将图像存储在DD RAM中,我声明一个数组,并希望存储在DD RAM的基地址中,如果有人可以帮助我,那么使用Xilinx SDK 11从RAM写入和读取图像数据的过程是什么。

2020-06-03 12:03:38

是否可以通过USB将数据从我的Spartan 3E FPGA Block RAM发送到我的计算机?我试图通过串行RS232发送数据,但那不起作用,所以想找到一个发送数据的备用路径。如果可能的话,那是什么锻炼?

2019-08-09 09:23:59

,sensAITM提供了供开发人员评估、开发和部署基于FPGA的机器学习/人工智能解决方案所需的全部资源,包括模块化硬件平台、演示示例、参考设计、神经网络IP核、软件开发工具和定制化设计服务。图1:sensAI架构

2020-10-23 11:43:04

我正在尝试使用virtex 5上的Block RAM来实现延迟线。延迟线需要将数据延迟一个时钟周期。这可能使用Block RAM吗?我尝试使用简单的双端口RAM,“先读”作为操作模式。我正在写一个

2020-06-18 15:40:33

AI芯片产品的设计和开发;技巧提升:课程剖析AI芯片开发流程及技巧,学员可熟悉AI芯片架构设计的各种处理技巧、芯片架构在FPGA上执行的方法,掌握AI芯片的工程应用和部署;配套开发板:配备与课程配套

2019-07-19 11:54:01

使用AI解决问题提供了第1次经验,但它导致了分散的跨组织的ML算法。不幸的是,这种分散的ML算法不能完全释放数据中隐藏的价值,也不能充分利用组织所拥有的宝贵业务知识。此外,它们还会给公司带来潜在风险。分散

2019-05-06 16:46:05

你好,我正在开发一个在VC709开发板上使用Virtex7 FPGA的系统。该应用程序使用32Mb的板载Block RAM作为设计中的存储元件。 FPGA配置序列完成后,有没有一种方法可以使用PC上的JTAG / USB接口直接写入和读取Block RAM的内容?谢谢,

2019-09-29 14:00:01

嗨,我正在使用“RAMB16_S36”原始实现一个512内存宽度的Block Ram。我通读了XAPP463用户指南,但我显然不了解初始化属性。INIT_00是否对应于[255:0] Block

2019-07-22 08:10:27

] .ram.r / s3a_noinit.ram / dpram.ram有一个有效信号,但没有连接数据输入引脚。无效数据可能会写入BlockRAM如何更正此错误并在bitgen退出之前重复3次警告

2019-06-04 09:08:32

嗨,我想为我的设计使用比特流加密,我遇到了一个关于9K Block RAM的问题,在答案记录39999中描述了r然后我决定在我的设计中删除所有9k Block RAM并将它们更改为16k Block

2019-06-06 07:23:18

Vertex 7 FPGA的最大DSP级联限制是多少? Vivado有没有办法提取这些数据?谢谢!

2020-07-19 16:26:03

嗨!我有一个关于分布式RAM和Block RAM的问题。芯片中有menexternalmemory或内存吗?请详细告诉我。谢谢!

2019-11-07 09:07:16

赛灵思Virtex-6 HXT FPGA ML630评估套件采用SiTime电子发烧友振具体型号为:SIT9102AI-243N25E200.0000,而目前针对这一型号sitime推出了抖动更低

2014-11-17 15:07:35

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包软件。提供了一些基础的函数库以及常用的控制函数模块,配合

2022-05-19 09:16:05

分析了西藏的湍流通量数据和地表温度数据,提出了表征地表温度变化特征的地表温度特征量。运用时间序列分析的方法,得到地表温度特征量和湍流通量之间的传递函数模型,

2009-03-02 22:00:19 22

22 为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集系

2010-02-11 11:20:27 69

69 本文提出了一种概率关联规则算法,通过使用概率的方法估算任意数据项集在事务数据库中出现的概率来求候选频繁项集,并给出了相关算法描述及其算法实现。将本算法与Apriori算法

2010-02-25 14:58:44 15

15 基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM 最大

2010-11-15 17:44:19 82

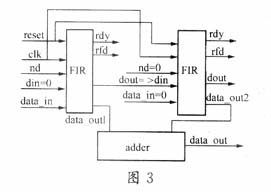

82 【摘 要】 提出了一种基于分布式算法的,采用基于RAM之移位寄存器来设计可级联FIR滤波器的设计方法。 &

2009-05-11 19:45:52 983

983

数字级联非压缩视频、数据光端机级联

2016-12-30 14:50:56 0

0 FPGA内部的RAM M9K

2017-04-07 11:40:04 4

4 Virtex 型FPGA 芯片是Xilinx 公司芯片系列中的一种,Virtex 系列的数据流及配置逻辑与XC4000 的数据流及配置逻辑有显著不同,但却与Xilinx 的FPGA 家族保持了很大

2017-11-18 11:37:38 2027

2027 FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

2018-03-28 17:07:28 9726

9726

本文介绍了如何在FPGA 中利用Block RAM 的特殊结构实现HDTV视频增强算法中灰度直方图统计。

2019-07-10 08:10:00 2578

2578 了解新的Block RAM级联功能,如何使用它,以及如何利用其功能和性能优势。

2018-11-23 06:56:00 4470

4470 电阻(Resistance,通常用“R”表示),是一个物理量,在物理学中表示导体对电流阻碍作用的大小。导体的电阻越大,表示导体对电流的阻碍作用越大。不同的导体,电阻一般不同,电阻是导体本身的一种特性。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。而超导体则没有电阻。

2019-03-28 14:36:09 4266

4266 电阻,因为物质对电流产生的阻碍作用,所以称其该作用下的电阻物质。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。没有电阻或电阻很小的物质称其为电导体,简称导体。不能形成电流传输的物质称为电绝缘,称绝缘体。

2019-04-20 09:55:31 54282

54282 电阻,因为物质对电流产生的阻碍作用,所以称其该作用下的电阻物质。电阻将会导致电子流通量的变化,电阻越小,电子流通量越大,反之亦然。没有电阻或电阻很小的物质称其为电导体,简称导体。不能形成电流传输的物质称为电绝缘体,简称绝缘体。

2020-06-08 16:00:14 3331

3331 些大材小用,因此xilinx公司在其FPGA内部专门集成了很多存储器模块,称作Block RAM,其犹如slice海洋当中的一颗颗明珠,专门实现数据暂存功能,且每个时钟区域都布置了若干个Block

2020-11-23 14:08:43 7379

7379

的寄存器输出,你要同时检查数据流的时序关系是否正确。在修改了时序关系后,可以按照我们之前的介绍,在GUI里使能Block RAM的输出

2021-03-26 15:50:27 1570

1570

本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 在FPGA中block ram是很常见的硬核资源,合理的利用这些硬件资源一定程度上可以优化整个设计,节约资源利用率,充分开发FPGA芯片中的潜在价值,本文结合安路科技FPGA做简单总结,说明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

2022-02-08 15:50:49 12183

12183

外围IP超高带宽需求。本文首先谈谈Speedster7t FPGA的片上SRAM,也就是Block RAM针对传统的结构所做出的一些优化。

2022-07-05 15:37:41 925

925 (人工智能)和ML(机器学习)的日益普及开辟了一个充满可能性的新世界,PC厂商和生态系统巨头都在寻求将这些先进的新功能添加到其产品功能集中。 在本篇博文中,莱迪思将讨论PC中AI/ML功能的增长趋势,为什么FPGA非常适合实现这些新

2022-09-08 17:19:25 931

931 在 FPGA 上实施 AI/ML 的选项

2022-12-28 09:51:08 525

525 本文主要讲述了Speedster7t FPGA的片上SRAM,也就是Block RAM针对传统的结构所做出的一些优化。

2023-07-13 17:24:15 302

302

ai芯片技术可以分为不同的体系架构。下面将对ai芯片技术架构做详细介绍。 首先,ai芯片技术架构可以分为显卡、TPU和FPGA三类。显卡是目前ai应用中使用最为广泛的一种芯片。nvidia公司推出的GTX和tesla系列显卡拥有超高的并行运算能力,

2023-08-09 14:28:47 807

807 设计都涉及到对RAM的读写操作。在FPGA芯片中,RAM也叫做存储块(Block RAM),可以存储大量的数据。 FPGA中的RAM可以一次读取多个数据,这是因为RAM的结构是一个多列的数据表格,其中每一列都是一个包含多个存储单元的块。通过在时钟的一次上升沿来读取RAM中的数据,这个操作必须在一个

2023-10-18 15:28:20 598

598 二是明晰 TDN 的可信数据流通关键技术范畴。从保障数据隐私安全、流通过程可控可信、跨节点跨平台跨技术互联互通等角度归纳、分析实现数据可信流通的关键技术方法。

2023-11-06 16:50:24 504

504

2024年2月29日,是德科技(Keysight Technologies,Inc.)宣布,针对人工智能(AI)和机器学习(ML)基础设施生态系统,推出了 AI数据中心测试平台,旨在加速AI / ML网络验证和优化的创新。

2024-02-29 09:32:49 207

207

FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 81

81

电子发烧友App

电子发烧友App

评论