本帖最后由 lee_st 于 2017-10-31 08:46 编辑

Verilog HDL代码书写规范

2017-10-21 20:53:14

1. 目的本规范的目的是提高书写代码的可读性、可修改性、可重用性,优化代码综合和仿真的结果,指导设计工程师使用VerilogHDL规范代码和优化电路,规范化可编程技术部的FPGA设计输入,从而做到

2017-12-08 14:36:30

Verilog HDL代码书写规范

2017-09-30 08:55:28

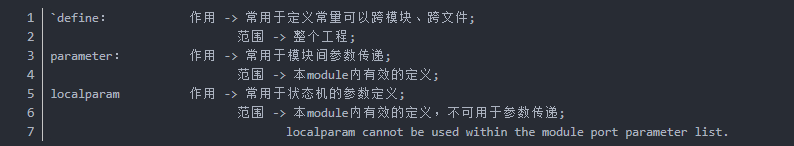

Verilog 预编译Verilog 语言支持宏定义(`define),参数 parameter,局域参数(localparam)以及`include等内容。这些数据常量的支持极大方便数字系统

2021-08-11 09:31:48

就可以了。3、作用parameter可以用作例化时的参数传递。具体方法参见《Verilog例化时的参数传递》一文在使用状态机时候区别挺大的状态机的定义可以用parameter 定义,但是不

2013-04-25 14:32:24

在Verilog定义函数的时候,有位宽的定义,我想问下诸位大侠,这个定义可以不要吗?这个位宽是不是该函数处理数据的能力的一种?还是有其他用途。请诸位大神赐教

2013-07-20 10:00:56

本帖最后由 lee_st 于 2017-10-31 08:46 编辑

Verilog语法基础讲解之参数化设计

2017-10-21 20:56:17

1.1 parameter与localparam使用区别1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)parameter与localparam使用区别;5)结束语。1.1.2

2021-07-26 07:55:51

PARAMETERS//*****************************parameter//函数名、宏定义、参数定义用大写//*****************************// DEFINE

2015-03-09 20:22:13

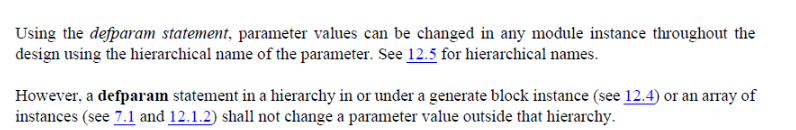

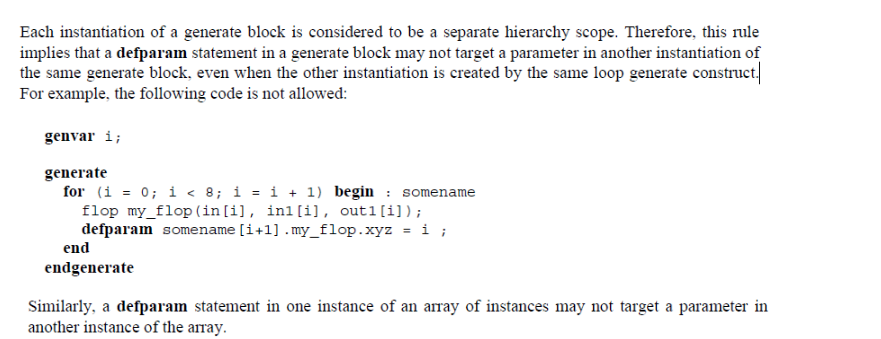

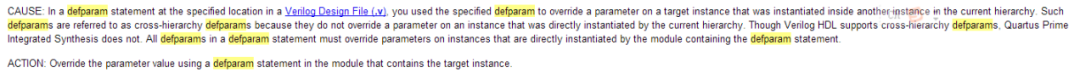

generate为verilog中的生成语句,当对矢量中的多个位进行重复操作时,或者当进行多个模块的实例引用的重复操作时,或者根据参数的定义来确定程序中是否应该包含某段Verilog代码的时候

2020-12-23 16:59:15

verilog中初值定义 -----initial是否可以被综合。

2018-09-14 11:49:40

明德扬设计规范对电路设计做了较高的要求,其目就在于用最简单的代码、最简洁的方式,设计出最易读、最健壮、最高效的Verilog代码。按照明德扬设计规范进行代码设计的具体要求如下。下面是初学者学习时定

2015-05-22 17:01:04

1.1 FPGA双沿发送之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿发送之Verilog HDL实现;5)结束语。1.1.2 本节

2021-07-26 06:20:59

1.1 FPGA双沿采样之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿采样之Verilog HDL实现;5)结束语。1.1.2 本节

2021-07-26 07:44:03

`FPGA宝贵实战经验及Verilog编程规范`

2013-06-10 12:03:11

此篇将围绕设计操作规程中的建元件库、做元件这一步骤展开,在此您不但可以学到PCB元件制作的标准、了解PCB设计的操作规程,让您的设计工作规范化;同时还可以学会使用PowerPCB软件做元件的相关操作方法,最终掌握并达到通过PowerPCB来实现设计标准化的目的。点击下载

2019-04-29 13:49:28

STM32野火平衡小车之如何搭建之PID与MPU6050初始化

2021-10-13 06:04:02

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-11 07:19:58

本文讨论了一些System Verilog问题以及相关的SystemVerilog 语言参考手册规范。正确理解这些规格将有助于System Verilog用户避免意外的模拟结果。

2020-12-24 07:07:04

PYCPLD的IP 设计规范本文讨论建立一种Python的模块脚本,将verilog语言变成python的程序块,方便以python的方式来组织IP,方便应用工程师更快的使用IP. 1. 如何将IP

2016-12-12 22:27:39

时钟频率是中代码计时计数器的重要参数,为提高代码的可读性及移植性,可通过一个参数定义时钟频率参数,请用parameter定义CLK_FRE为50MHz的时钟频率参数

2023-08-29 09:30:19

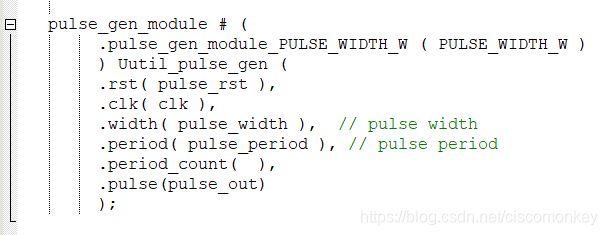

基于上一题目模块中定义的parameter参数,在例化该模块时实现参数传递

2023-08-30 11:23:51

这几天一直忙着办理离职手续,整理以前做的工作,方便交接,小钢炮的使用就暂时搁浅了。前面看到 小钢炮的源码时,觉得分类不规范,看的蛋疼。接合原子的例子,特意重新建了一个工程。下面是分类:典型的原子风格

2016-02-24 15:32:59

);//输入输出信号列表//说明reg //寄存器wire//线网parameter//参数input//输入信号output//输出信号inout//输入输出信号function//函数task//任务

2018-09-18 09:37:40

FPGA verilog代码书写规范,很好的借鉴

2015-05-21 11:36:27

,参数定义建议大写,另外信号命名最好体现信号的含义。规范建议以下是一些书写规范的要求:1、用有意义的有效的名字如sum、cpu_addr等。2、用下划线区分词语组合,如cpu_addr。3、采用一些前缀

2020-09-21 16:48:48

/jishu_524793_1_1.html29【芯航线FPGA学习平台众筹进度帖】Verilog语法基础讲解之参数化设计:https://bbs.elecfans.com/jishu_528770_1_1.html30【连载视频教程

2015-11-26 10:50:51

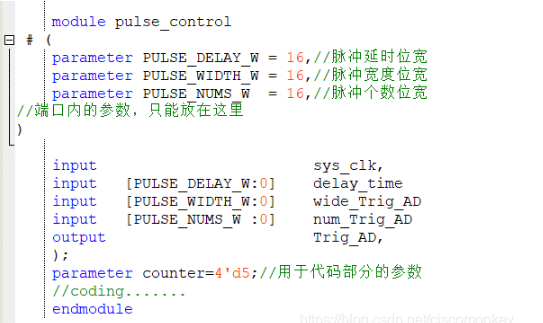

的定义和使用,参数型常数经常用于定义延迟时间和变量宽度。

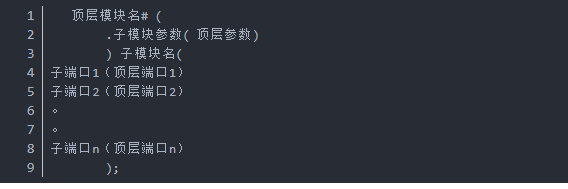

parameter可用作在顶层模块中例化底层模块时传递参数的接口,localparam的作用域仅仅限于当前module,不能作为参数传递的接口

2023-05-17 16:26:53

代码规范化如何学习,单片机也要求规范化么?

2023-10-12 07:19:17

关于发帖标题规范化管理公告由于论坛管理事物繁重,很多时候由不得我们几个管理员的眼睛和手指去处理,为了大家的问题能够更好,更直接的让各位大大们过目,让大家的问题都能得到解决,管理员团队特出发帖标题规范

2014-11-04 17:11:07

] b; //定义一个八位的wire数据reg [7:0] b; //定义一个八位的reg数据其中。[7:0]表示位宽,只要是整数就好,当然分号左边的数要大于右边的。4、参数定义:parameter

2016-03-16 10:45:02

`勇敢的芯伴你玩转Altera FPGA连载34:Verilog代码书写规范特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 虽然没有

2017-12-27 09:41:12

求大神给下我单片机C语言模块化程序,让我好好学习,规范化我的代码编写

2013-07-23 14:57:44

单片机开发之C语言编程基本规范为了提高源程序的质量和可维护性,从而最终提高软件产品生产力,特编写此规范。本标准规定了程序设计人员进行程序设计时必须遵循的规范。本规范主要针对单片机编程语言和08编译器

2017-10-07 11:53:15

本规范主要针对单片机编程语言和08编译器而言,包括排版、注释、命名、变量使用、代码可测性、程序效率、质量保证等内容。 1.基本规则 格式清晰、注释简明扼要、命名规范易懂、函数模块化、程序易读易维护

2017-08-06 09:46:54

很反感很反感很反感很反感

2016-06-27 14:14:17

方式:some.where.else.theSignal.pull()在生成RTL代码时,会讲该信号声明一个端口链接偷穿到我们这一级的Component。Component参数化设计与我们编写Verilog时相同,在SpinalHDL里

2022-07-21 14:20:23

有没有人对如何用参数化加法器树编写Verilog有任何建议,输入参数是操作数的数量?加布里埃尔以上来自于谷歌翻译以下为原文Does anyone have any suggestions

2019-04-25 13:28:42

本文档为作者 在嵌入式和嵌入式 linux C语言的学习和工作中所总结的代码规范 ,是作者从 STM32单片机开发向 Linux C开发的时候为了摆脱遗留的编码规范陋习而编写的 。因此,本文档 主要

2020-01-14 10:25:08

电力企业安全工器具规范化操作指导系统 一、系统概述 对电力生产人员来说,了解各种安全工器具的性能和用途,正确掌握它们

2010-11-18 14:02:42

》踩到的坑在很早之前,曾写过如何在SpinalHDL中例化之前用Verilog/SystemVerilog所写的代码,可参照文章《[SpinalHDL——集成你的RTL代码]》一文。在

2022-08-31 14:58:31

时对ddr初始化,但是在6678数据手册Table 2-23 DDR3 Boot Parameter Table 中并未找到与之相关的配置参数。谢谢

2018-08-06 08:34:24

贴片知识课堂九,PCB设计规范化第一节PCB设计和生产的关系到底有多大?这一直是许多工程师怀疑,甚至想弄明白的问题!今天麦斯艾姆(massembly)贴片知识课堂,为广大工程师朋友直观地讲解一些

2012-09-14 09:24:42

本帖最后由 eehome 于 2013-1-5 10:04 编辑

麦斯艾姆(massembly)贴片知识课堂十一,PCB设计规范化第三节麦斯艾姆(massembly)贴片知识课堂继续上次的话

2012-10-31 14:16:16

麦斯艾姆(massembly)贴片知识课堂十,PCB设计规范化第二节麦斯艾姆(massembly)贴片知识课堂继续上次的话题“PCB设计规范化”。1, 散热焊盘,对于某些功率器件,包括功放,电源

2012-10-31 14:12:59

麦斯艾姆(massembly)贴片知识课堂十,PCB设计规范化第二节麦斯艾姆(massembly)贴片知识课堂继续上次的话题“PCB设计规范化”。1, 散热焊盘,对于某些功率器件,包括功放,电源

2012-09-18 09:43:27

s-parameter calculator:S参数计算工具.input S11,S22,S12,S21等参数,就可以进行参数计算。

2008-10-23 15:24:23 31

31 Verilog代码书写规范

本规范的目的是提高书写代码的可读性、可修改性、可重用性,优化代码综合和仿真的结果,指导设计工程师使用

2010-04-15 09:47:00 106

106 云计算作为物联网快速增长的重要部分,市场规模年均复合增长达到91.5%。为更好地完善和建立云计算服务市场准入制度,加快云计算服务质量、资源整合,云计算产业发展拟定五项规范化要求。

2013-06-13 17:00:27 561

561 verilog代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:43:38 24

24 verilog代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:42:02 145

145 verilog代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:36:05 34

34 verilog代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:28:34 35

35 verilog代码规范,学会写代码还不行,我们需要更加的规范。

2016-03-25 14:26:26 24

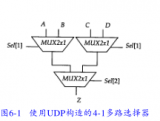

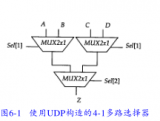

24 本章讲述Verilog HDL指定用户定义原语UDP的能力。UDP的实例语句与基本门的实例语句完全相同,即U D P实例语句的语法与基本门的实例语句语法一致。verilog相关教程材料,有兴趣的同学可以下载学习。

2016-04-25 16:09:32 12

12 在C语言中我们不遵循编译器就会报错的规定叫规则;约定成俗但不遵守也不会出错的规定叫规范。比如变量必须先定义后使用,如果我们不定义就直接使用就会出错。

2016-07-26 15:44:42 5

5 cordic算法verilog实现(简单版)(转载)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0]

2017-02-11 03:06:11 3044

3044

华为的verilog编码规范

2017-11-01 08:41:26 40

40 推特文本中包含着大量的非标准词,这些非标准词是由人们有意或无意而创造的。对很多自然语言处理的任务而言,预先对推特文本进行规范化处理是很有必要的。针对已有的规范化系统性能较差的问题,提出一种创新

2017-12-15 14:12:59 0

0 在该工程中,国网河北省电力公司严格落实规范化开工要求,占地协调、林木清理、三线迁改等工程通道补偿协议签订及合规性手续办理已全面满足连续施工条件。 3月22日,北京西—石家庄1000千伏交流 特高压

2018-04-07 19:35:00 3918

3918 对关系的规范化是改造关系模式过程,首先,根据一组不同级别的范式判定关系的规范化程度,确定不正常的数据依赖关系,通过模式分解将一个低一级范式的关系模式,转换为若干个高一级的范式的关系模式的集合,消除其中不合适的数据依赖,以解决插入异常、删除异常、更新异常和数据冗余问题。

2018-09-05 14:26:00 5

5 设计规范化与自由创作之间没有任何矛盾。它只是制约了那些可能出错或者低效的行为,令设计思路更加明朗、设计效率得到提高、设计质量充分保证。

2018-10-09 11:10:23 2987

2987 很多人认为,IC/FPGA属于设计范畴。设计是一个需要设计师自由创作的过程,怎么可能被一些条条框框所局限呢?其实,设计规范化与自由创作之间没有任何矛盾。

2018-10-11 09:59:31 3140

3140 ,如receive_clk_b; ③ 由parameter定义的常量要求全部字母大写,自己定义的参数、类型用大写标识,推荐使用parameter来定义有实际意义的常数,包括单位延时、版本号、板类型、单板在位信息、LED

2020-11-24 12:12:08 2989

2989 ADPA1105 S-Parameter

2021-01-27 19:48:15 0

0 AD9650 S-Parameter

2021-01-28 09:56:09 1

1 ADRF5046 - S-Parameter

2021-01-28 14:33:26 1

1 ADRF504 7 - S-Parameter

2021-01-28 14:35:27 0

0 ADL6012 S-Parameter

2021-01-30 09:17:06 0

0 LTC5597 S-Parameter

2021-01-30 09:36:07 0

0 ADRF5043 S-Parameter

2021-01-30 09:38:07 0

0 ADRF5042 s-parameter

2021-01-30 09:40:07 0

0 HMC798A S-parameter

2021-01-30 12:23:18 0

0 HMC966 S-Parameter

2021-02-01 11:31:16 0

0 ADPA7005 S-Parameter

2021-02-02 10:14:13 1

1 ADPA7005 S-Parameter

2021-03-05 10:47:16 0

0 用户定义的原语 在前一章中,我们介绍了Verilog HDL提供的内置基本门。本章讲述Verilog HDL指定用户定义原语U D P的能力。 U D P的实例语句与基本门的实例语句完全相同

2021-03-05 15:30:36 1426

1426

ADL5725 S-Parameter

2021-03-11 13:11:30 0

0 ADRF6780 S-Parameter

2021-03-11 13:55:32 0

0 时的检测效果不理想。因此,提出一种基于规范化函欻的深度金字塔模型(Norm-DP)算法,使用规范化函数融合可变形部件模型和卷积神经网络模型,直接从金字塔特征中提取正负样本,使用隐变量攴持向量杋进行模型训练,结合柔性非

2021-03-30 14:09:02 14

14 作者 | 涛姐涛哥 链接 | cnblogs.com/taojietaoge/p/11575376.html 如何更规范化编写Java 代码 Many of the happiest people

2021-08-27 09:31:30 3415

3415 钢网开孔设计规范定义

2021-10-18 11:27:31 9

9 parameter关键字定义模块特定的参数,该参数在特定模块实例的范围生效。参数用于为模块实例提供不同的自定义,例如,输入或输出端口的宽度。以下是使用parameter关键字的示例:

2022-06-26 10:46:20 1037

1037 在前一章中,我们介绍了Verilog HDL提供的内置基本门。本章讲述Verilog HDL指定用户定义原语U D P的能力。

2022-08-08 11:46:46 733

733 在实际工作中,许多公司对Verilog程序编写规范都有要求。在公司内部统一Verilog程序编写规范不仅可以增强程序的可读性、可移植性,而且也有助于逻辑工程师之间交流、沟通,提升逻辑组成员之间的团队协作能力。本文就大部分公司常见的Verilog程序编写规范作一个介绍。

2022-09-15 09:35:58 3412

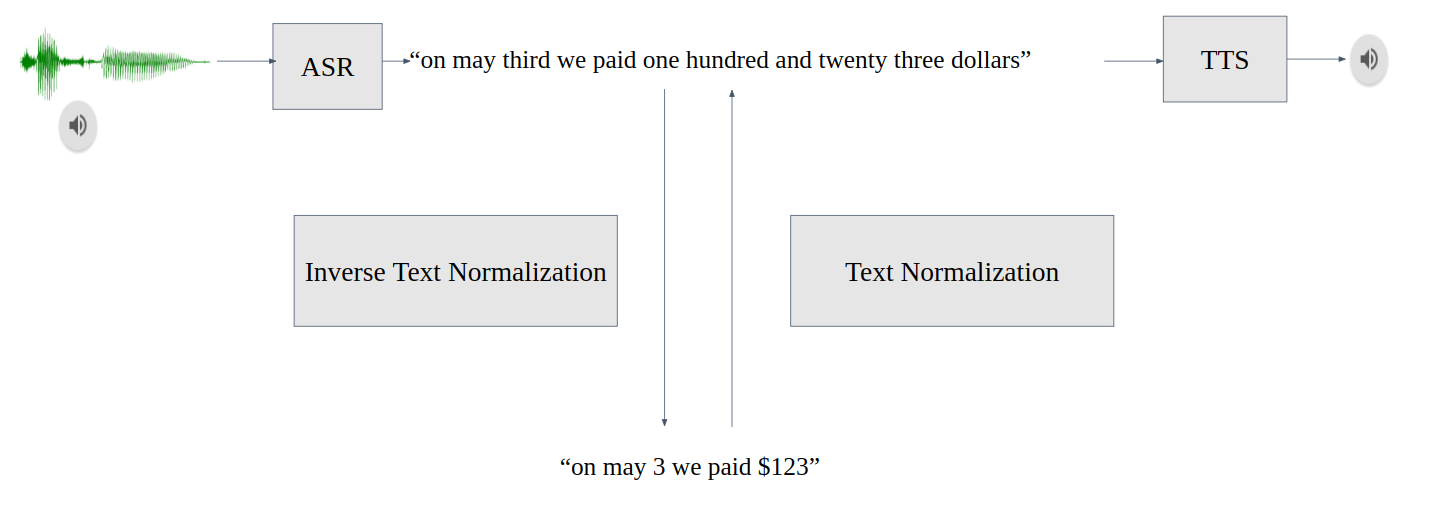

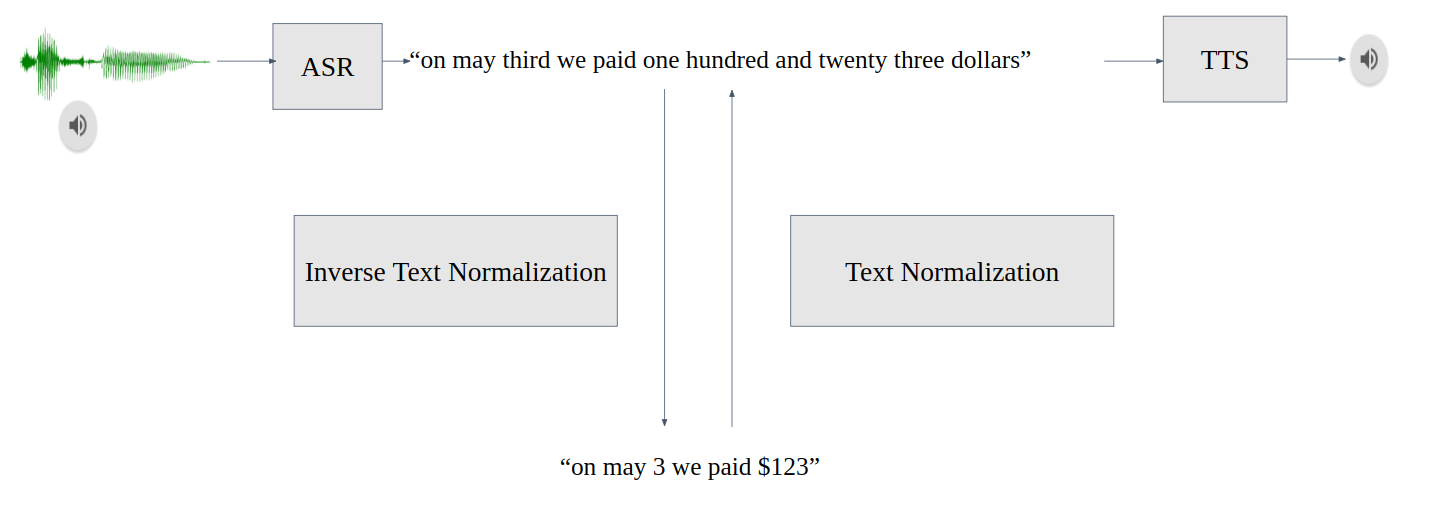

3412 文本规范化( TN )将文本从书面形式转换为口头形式,是文本到语音( TTS )之前的一个重要预处理步骤。 TN 确保 TTS 可以处理所有输入文本,而不会跳过未知符号。例如,“ 123 美元”转换为“一百二十三美元”

2022-10-11 11:41:12 1411

1411

本规范的目的是提高书写代码的可读性 可修改性 可重用性 优化代码综合和仿真的结 果 指导设计工程师使用VerilogHDL规范代码和优化电路 规范化公司的ASIC设计输入从而做到。

2022-11-23 17:28:18 791

791 在testbench中避免使用绝对的时间,如#20,#15或#(CYC+15)等,应该在文件前面使用parameter定义一些常量,使得时间的定义象#(CYC+OFF0)的形式,便于修改。

2022-11-25 09:26:41 788

788 FPGA 设计的硬件语言Verilog中的参数化有两种关键词:define 和 paramerter,参数化的主要目的是代码易维护、易移植和可读性好。

2022-12-26 09:53:10 676

676 我们将介绍如何使用verilog参数和generate语句来编写可重用的verilog 代码。

与大多数编程语言一样,我们应该尝试使尽可能多的代码可重用。这使我们能够减少未来项目的开发时间

2023-05-11 15:59:21 647

647 注:以R起头的是对编写Verilog代码的IP设计者所做的强制性规定,以G起头的条款是建议采用的规范。每个设计者遵守本规范可锻炼命名规范性。

2023-08-15 16:23:41 1089

1089 Verilog规范对于一个好的IC设计至关重要。

2023-08-17 10:14:07 580

580

c语言带参数的宏定义 C语言宏定义是一种宏替换机制,它可以将一个标识符替换为一个代码片段。宏定义通常在程序中用来方便地进行常量定义或函数模板定义。在C语言中,宏定义有以下几种类型: 1. 简单

2023-09-04 17:45:18 1515

1515

正在加载...

电子发烧友App

电子发烧友App

评论