远创智控的YC-EIP-RS485/232通讯网关,自主研发的ETHERNET/IP从站功能,完美解决了这个难题。这款网关不仅可以将ETHERNET/IP网络和RS485/RS232总线连接起来

2023-07-22 09:20:52 1210

1210

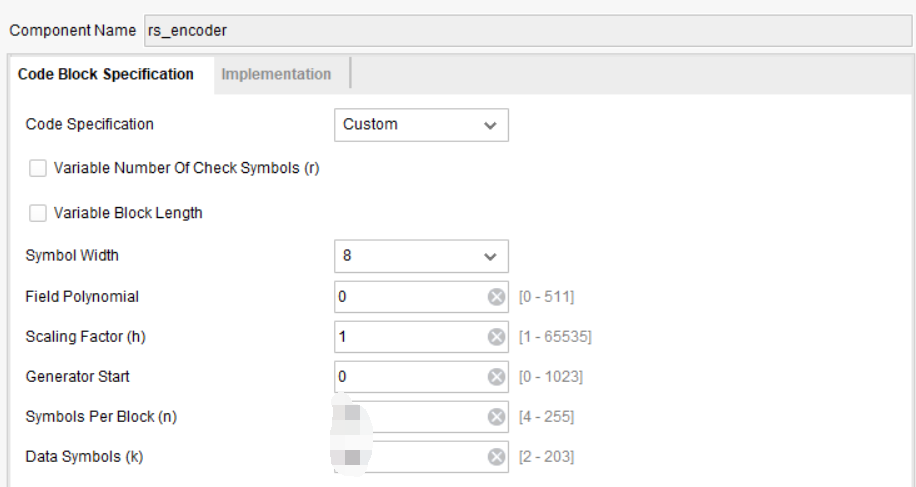

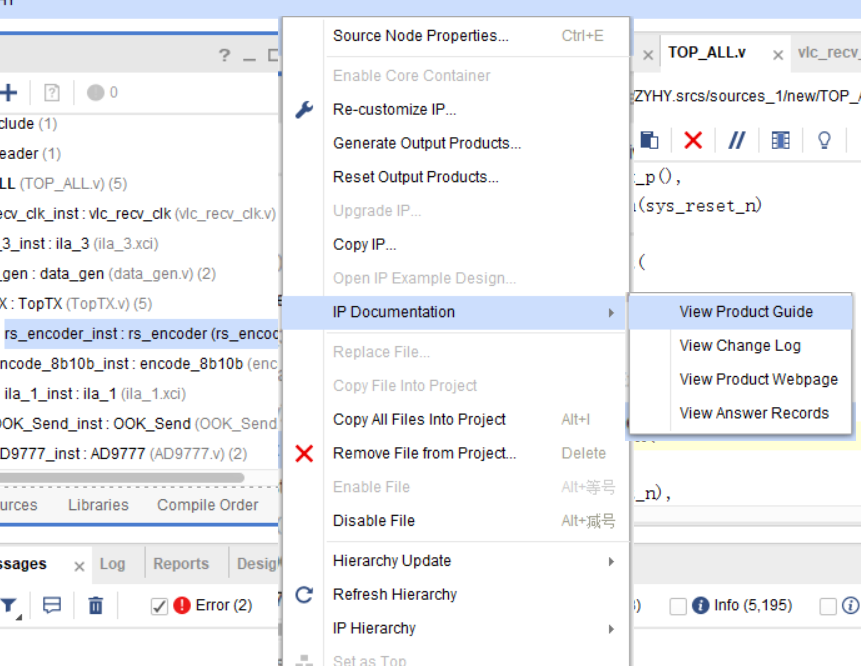

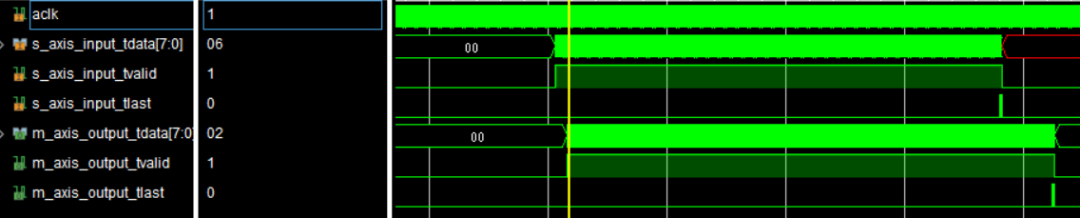

本人使用RS IP核进行编码时出现IP核后面带有美元符号,不能正常使用。求大神给予破解帮助。

2019-08-20 11:34:00

,C表示修改次数。RS-232-C总线标准设有25条信号线,包括一个主通道和一个辅助通道。 在多数情况下主要使用主通道,对于一般双工通信,仅需几条信号线就可实现,如一条发送线、一条接收线及一条地线

2013-06-19 19:29:00

TXE发送空中断和TC发送完成中断的区别是什么? RS485电气特性是什么?怎么实现RS485硬件设计?

2021-11-30 06:36:23

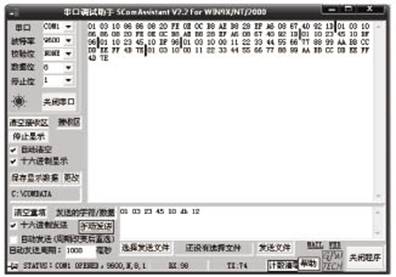

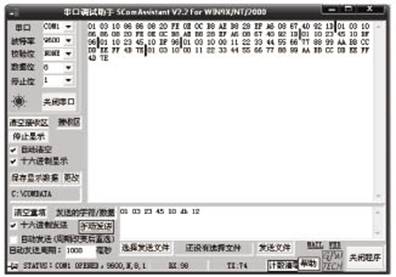

阅读目录1、RS485简介 2、RS485特性3、RS485通信硬件实现4、RS485通信软件实现OS:Windows 64Developmentkit:MDK5.14IDE:UV4MCU

2021-08-19 08:20:09

本文以战术军用通信系统的首选码RS(31,15)码为例,对生成多项式进行了优化,并采用查表法的原理极大地提高了编码器运算数据的能力,缩短了运算周期,最终利用VHDL语言编译,在FPGA中实现,得到了正确的RS编译码。

2021-05-06 09:27:33

利用FPGA自带的IP核实现双口RAM用于2片MCU进行数据交换时多次读数据后RAM中数据变为了0,是什么意思,打什么帮帮忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

论坛里面的大神们,有没有已经完成LDPC码编译码算法的FPGA实现,本人目前在做这方面的项目,时间比较紧,紧急求购IP核。。

2012-04-16 23:43:28

本帖最后由 allan***c 于 2018-3-16 10:48 编辑

Labview基于VISA实现RS232、RS485 Modbus的通讯,刚在网上查了写资料,做了这么个程序,亲

2018-03-14 10:28:45

Verilog中用*实现乘法和用乘法器ip核实现乘法综合结果有哪些不同?

2016-03-18 09:35:13

的不足,同时也方便在现场可编程门阵列(FPGA)中增加一些其他相关的应用功能,因此在FPGA中实现CVSD语音编译码调制功能的前景将是非常广阔的。这里将详细介绍什么是CVSD?其算法分析如何在FPGA中实现?

2019-08-07 07:04:27

什么是Turbo码的迭代译码算法?Turbo 码获得优异性能的第二个重要因素是应用了基于最大后验概率准则 (MAP) 的迭代译码算法。当前Turbo译码算法有哪些?(1) 标准算法(MAP)它对

2008-05-30 16:24:49

请问各路大神有没有基于multisim的线性分组码 循环码 卷积码的编译码电路图啊,在这里谢过你们了

2015-04-23 17:56:37

【摘要】:Viterbi译码器在通信系统中应用非常普遍,针对采用DSP只能进行相对较低速率的Vit-erbi译码的问题,人们开始采用FPGA实现高速率Viterbi译码。本文首先简单描述了

2010-04-26 16:08:39

技术可以使误码率进一步的降低。RS码属于分组码,是BCH码的一个子类,是最大距离可分码,它是由Reed和Solomon于1960年构造出来。由于它具有很强的纠正随机错误和突发错误的能力,以及极低的不可探测的差错率,所以RS码已经广泛应用于深空通信、卫星通信、存储介质、数字视频广播和扩频数字通信中。

2019-09-26 07:11:07

对不同的设计方法进行分析和比较,选择优化的设计方法,利用VHDL分别设计(15,7)BCH码的编码器和译码器,并能够对两部分进行单独仿真调试,实现其相应的功能。

2012-05-10 11:36:06

本文介绍如何在 vivado 开发教程,创建新工程 的基础上, 使用IP集成器, 创建块设计。

2021-02-23 07:02:27

RS485线在F103环境下进行UART通信实验和RS232通信实验在F407环境下进行RS485实验(1.我的103板子没有485口,2.正好看下开发板环境不同的差异)UART通信实验(通用异步收发器)UART串口通信原理:什么是串行通信?什么是异步通信?什么是全双工?什么是串行.

2022-02-17 07:17:45

如何利用VHDL实现线性分组码编译码器的设计?

2021-04-28 06:41:40

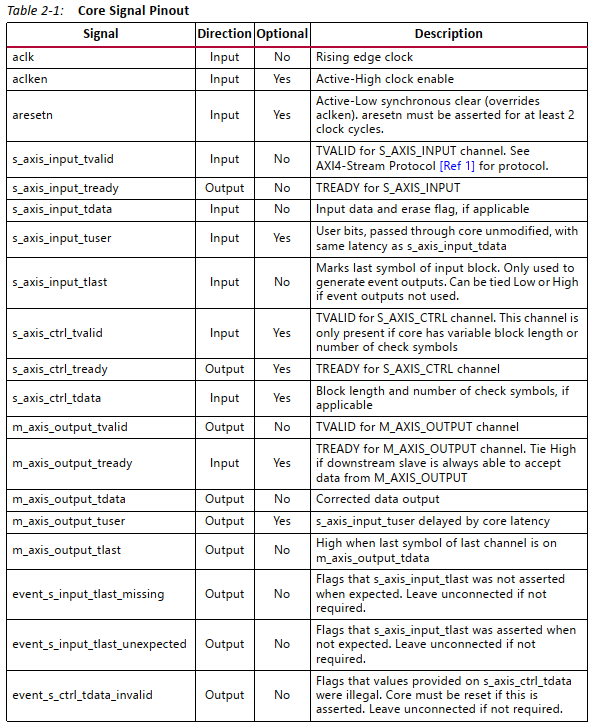

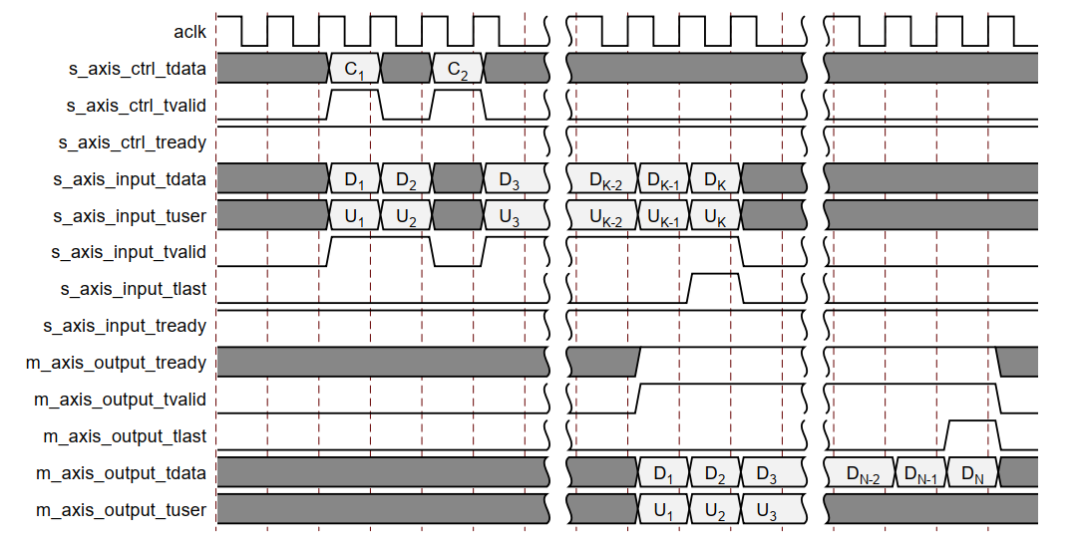

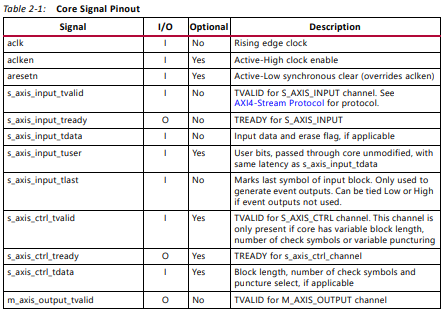

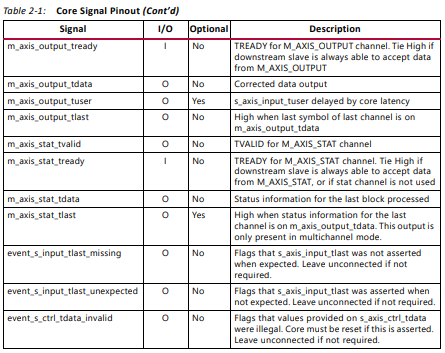

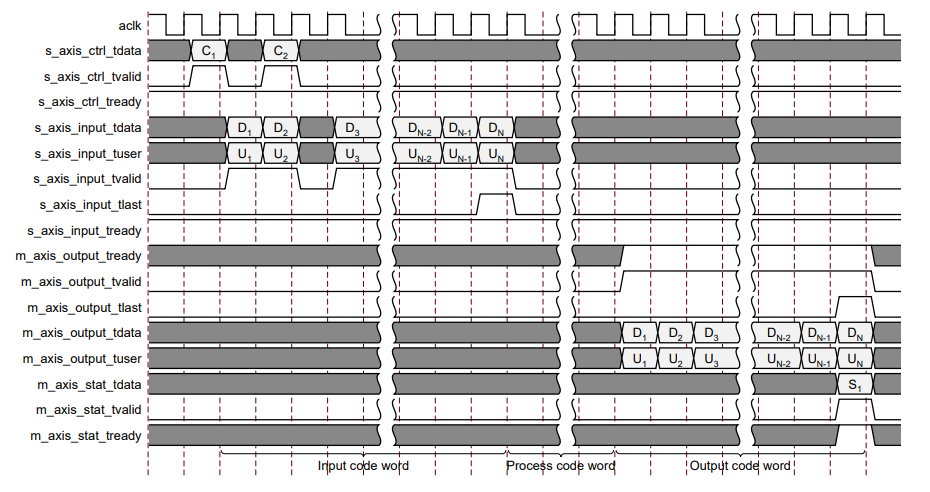

本文研究了RS码的实现方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS编译码器的设计,同时对其进行了仿真和在线调试,并给出了功能仿真图和测试结果。时序仿真结果表明,该编译码器能实现预期功能。

2021-06-21 06:23:53

RS纠错编码是目前最有效、应用最广泛的差错控制编码之一,是一种纠错能力很强的多进制BCH码,也是一类典型的代数几何码。它是由里德(Reed)和索洛蒙(Solomon)应用MS多项式于1960年首先构造出来的。

2019-08-20 08:16:26

基于FPGA的Turbo码编译码器各模块实现的 VHDL或verilog HDL程序。急求啊谢谢大神啦!!

2015-06-08 22:45:24

截短Reed-Solomon码译码器的FPGA实现提出了一种改进的BM算法,并在此基础上提出了一种大量采用并行结构的截短RS码译码器的实现方式。验证表明,该算法能显著提高基于FPGA的RS译码

2009-09-19 09:39:43

等优点。在高次脉冲编码调制终端设备中广泛应用做接口码型,在速率低于8448kb/sd的光纤数字传输系统中也被建议作为线路传输码型。本文针对光纤通信传输码型的要求和CMI码的编译码原理,设计了CMI码

2009-03-25 13:19:20

Turbo码编码器的FPGA实现Turbo码译码器的FPGA实现Turbo码编译码器的性能有哪些?

2021-05-07 06:06:23

请教一下大神如何在STM32中实现LIN协议和RS485协议呢?

2022-12-13 07:17:37

上图中的RS485的方向切换怎么能实现呢?R2in和R1in一样的是接收TTL电平,那R2out岂不是也是正负压来回变化吗?怎么实现切换的呢?请大家指点下!谢谢啦!

2019-09-17 08:20:43

前言 随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息的处理变得日益重要,如基于PC的软复用器的实现,使得通过PC接收DVB(数字视频广播)码流

2019-05-05 09:29:32

【作者】:杨一波;李广军;【来源】:《信息与电子工程》2010年01期【摘要】:根据RS编码器的特点,提出了一种可以实现任意编码多项式、任意并行倍数的并行RS编码器IP的自动生成方法。该方法

2010-04-22 11:46:09

采用数字化技术, 在测控系统中用IP 核实现D/A 转换,并且在1 片可编程逻辑器件中实现。它不受温度的影响, 既可保持高分辨率, 又可降低对电路精度和稳定度的要求,并减少元

2009-04-16 08:51:44 11

11 本文介绍的是利用多路转换开关实现准多点RS-232通信。

2009-04-20 11:30:51 39

39 详细介绍了嵌入式L inux 编译环境的架构, 讨论了如何在L inux2. 4 环境下实现IP 安全协议, 实现数据安全传输, 通过利用L inux 实现防火墙所提供的5 个钩子函数挂载点, 将安全模块嵌入到

2009-04-21 23:30:01 28

28 本文主要讲述的是如何利用多路转换开关实现准多点RS-232通信。

2009-04-23 08:58:40 27

27 针对LDPC码与RS码的串行级联结构,提出了一种基于Chase的联合迭代译码方法。软入软出的RS译码器与LDPC译码器之间经过多次信息传递,性能可以逼近最大似然译码。模拟结果显示:

2009-05-12 21:47:25 22

22 采用数字化技术, 在测控系统中用IP 核实现D/A 转换,并且在1 片可编程逻辑器件中实现。它不受温度的影响, 既可保持高分辨率, 又可降低对电路精度和稳定度的要求, 并减少元

2009-05-15 15:09:58 12

12 简易编译码电路图

2009-05-19 10:47:26 9

9 本文利用Altera 公司开发的RS、NCO 和FIR IP core 以及Simulink、DSP_Builder中的模块快速搭建了一个RS(204,188) +DQPSK 的低中频调制解调系统。分别在Simulink、Modelsim 中验证了系统的功能,

2009-08-10 11:09:07 10

10 RS 码以其强大的纠正随机错误和突发错误的能力,被广泛地应用于各种数字通信系统中,本文首先叙述了RS 码译码的基本原理,给出了实现RS 码软判决译码的方法和用DSP 实现译码的

2009-08-19 10:26:07 22

22 本文利用可编程逻辑的灵活性和Nios 的强大处理能力,将多种编译码模块和微处理器模块集成到一片FPGA 内部,方便地实现了通用编译码器的设计。由于采用了VHDL 语言,使系统具有可移

2009-11-30 14:27:56 22

22 RS-232C、RS-422与RS-485的由来

RS-232、RS-422 与RS-485 都是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的,RS-232 在1962 年发布,命名为EIA-232-E,作为

2010-06-07 16:15:18 24

24 针对固定码长Turbo码适应性差的缺点,以LTE为应用背景,提出了一种帧长可配置的Turbo编译码器的FPGA实现方案。该设计可以依据具体的信道环境和速率要求调节信息帧长,平衡译码性

2010-11-11 16:07:59 26

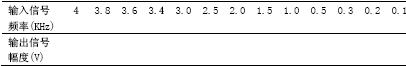

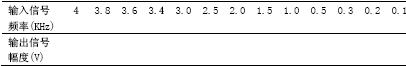

26 PCM编译码实验

一、实验目的1. 掌握PCM编译码

2008-10-21 13:35:45 8339

8339

基于BIST的编译码器IP核测

随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合

2008-12-27 09:25:39 794

794

差错控制编码技术对改善误码率、提高通信的可靠性具重要作用。RS码既可以纠正随机错误,又可以纠正突发错误,具有很强的纠错能力,在通信系统中应用广

2009-03-28 16:38:42 636

636

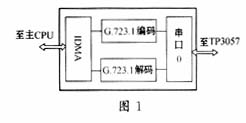

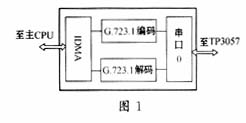

【摘 要】 介绍了ITU-TG.723.1标准语音编译码器的算法及其在ADSP-2181芯片上的实现 。软硬件结合实现了语音信号的采样和实时编译码,完全符合ITU-TG.723.1标准的定点算法

2009-05-10 19:54:11 1283

1283

摘要:提出了基于欧氏算法和频谱分析相结合的RS码硬件编译码方法;利用FPGA芯片实现了GF(2 8)上最高速率为50Mbps、最大延时为640ns的流式译码方案,满足了高速

2009-06-20 14:19:33 856

856

摘要:采用数字化技术、在测控系统中用IP核实现D/A转换,并且在1片可编程逻辑器件中实现。它不受温度的影响,既可保持高分辨率,又可降低对电路精度和稳

2009-06-20 15:04:15 910

910

RS232,RS422,RS485的区别

1、RS-232-C

RS-232-C是美国电子工业协会EIA(Electronic Industry Association)制定的一种串行物理接口标准。RS是英文

2009-10-17 08:33:44 2954

2954 利用STC11F02E的RS232/RS485转换器设计方案

为了便于对分布式的各个现场测控设备实现集中控制,现场总线技术得到了广泛的应用。RS485总线因其硬件设

2010-03-17 10:49:00 7514

7514

介绍了ITU-TG.723.1标准语音编译码器的算法及其在ADSP-2181芯片上的实现 。软硬件结合实现了语音信号的采样和实时编译码,完全符合ITU-TG.723.1标准的定点算法,通过了ITU-T的所

2011-07-06 09:49:07 1295

1295

从赫夫曼树定义及算法出发,介绍了一个赫夫曼编译码系统的设计与实现过程。这对于深入理解数据结构、程序设计有益。

2011-10-19 14:44:01 31

31 利用ME算法实现结构设计了一种低资源占用率、低成本的高速RS译码器。逻辑综合及仿真结果表明,基于Altera公司CycloneII系列FPGA的RS(255,239)译码器,工作时钟达210 MHz,可满足数据速率1.68 Gb

2011-12-15 17:23:28 28

28 本文介绍了 RS[ 255, 223 ]编译码器的 FPGA设计和基于线形反馈移位寄存器的编码器设计 , 以及由伴随式计算、关键方程求解、钱氏搜索、Forney算法等功能模块组成的译码器。为了实现简单

2012-05-22 10:43:40 45

45 介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构实现

2013-01-25 16:43:46 68

68 基于FPGA的RS码电路设计,编码译码原理。

2016-03-30 16:32:42 2

2 RS编解码的FPGA实现-说明RS编解码的FPGA实现-说明。

2016-05-04 15:59:44 21

21 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

在Vivado下完之前,先把Zynq的软件编译环境安装好,可以用来重新编译基于Zynq的Linux系统,同时能写基于Zynq的C程序(其实Vivado中的SDK也能实现)。

2017-02-10 15:54:12 4487

4487

RS232,RS422,RS485的区别

2017-03-04 17:53:55 36

36 本文从研究应用于AOS系统的RS(255,223)编译码接口卡出发,深入地分析和研究了纠错码原理、RS编译码算法与设计、PCI总线标准与设计和FPGA技术。 随着科技的发展,纠错码技术在通信领域

2017-08-31 14:50:39 4

4 。但是工业设备的使用环境经常比较恶劣,可能会存在噪声或者电源谐波的干扰,RS-232在如此环境下抗干扰的能力远不及RS-485,除此之外,RS-232只能是一对一控制,而RS-485则可以实现一对多控制;RS-232一般是9针公头,而RS-485则是两根线就可以控制。因此工业环境下的串行通信

2017-09-29 17:10:28 6

6 RS(ReedSolomon)编码是一种具有较强纠错能力的多进制BCH编码,其既可纠正随机错误,又可纠正突发错误。RS编译码器广泛应用于通信和存储系统,为解决高速存储器中数据可靠性的问题,文中

2017-10-17 11:21:32 46

46 (;A平台,利用Xilinx lSE软件和Verilog硬件描述语言,对译码器中各个子模块进行了设计和仿真。整个译码器设计过程采用流水线处理方式。时序仿真结果表明在保证错误符号不大于8个的情况下,经过295个固有延迟之后,每个时钟周期均可连续输出经校正的码字,该RS译码器的纠错能

2017-11-07 15:27:06 15

15 在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动添加到当前工程中;另一种是利用Manage IP,创建独立

2017-11-18 04:22:58 5473

5473 面向云存储容错系统提出了一种RS再生纠删码,该编码继承了RS编码容多错的可靠性,又能实现容三错的高效性。对RS再生码中单节点故障混合修复方法进行了介绍,并求出了混合修复时磁盘读取数的理论下界

2018-02-07 15:53:48 0

0 资源。为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。

2019-08-02 08:08:00 3816

3816 此视频概述了Vivado Design Suite中的IP加密。

它涵盖了IP加密工具流程,如何准备加密IP以及如何在Vivado中运行加密工具。

2018-11-20 06:34:00 5948

5948 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-29 06:32:00 3340

3340 了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

2018-11-30 19:24:00 4251

4251 光电隔离型RS232/485到RS485集线器。 有效隔离从口RS485之间、从口RS485和主口RS485之间干扰。 RS485主口和从口支持256个从站,超强信号放大能力。 可实现RS485网络

2020-04-04 16:22:00 1715

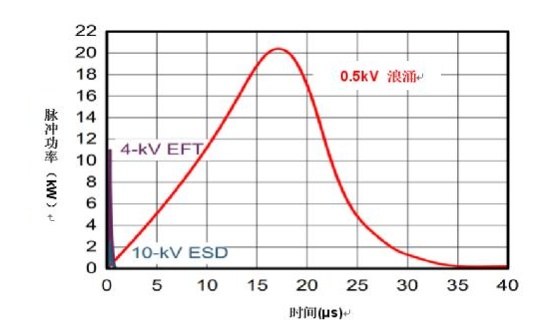

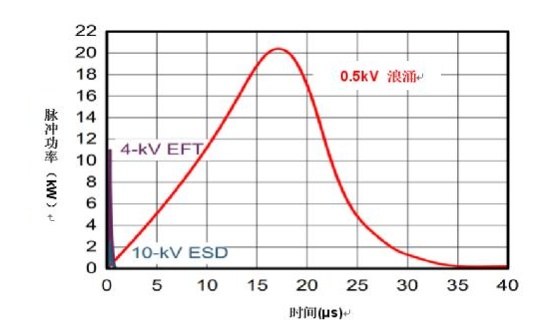

1715 RS-485收发器设计旨在应对恶劣的工作环境。除了能够适应嘈杂的工厂环境外,RS-485收发器还可以在户外环境中稳定运行,抵御雷击等导致的电压浪涌对通信的干扰。

2019-04-18 11:32:32 1013

1013

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP

2020-12-29 15:59:39 9496

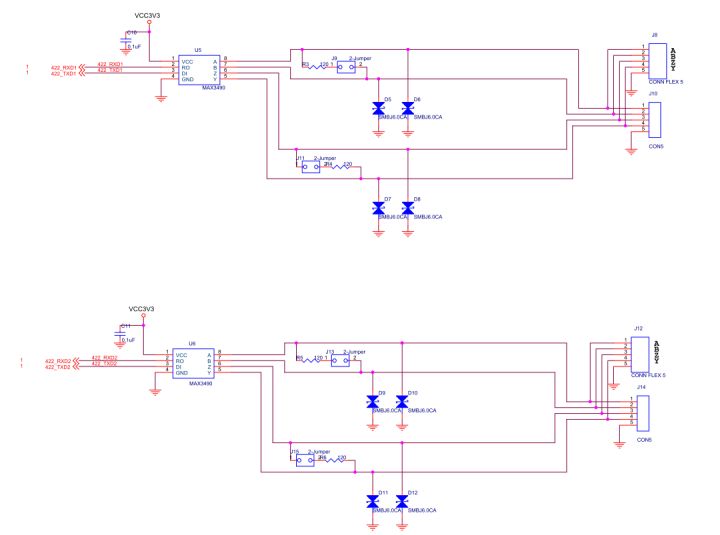

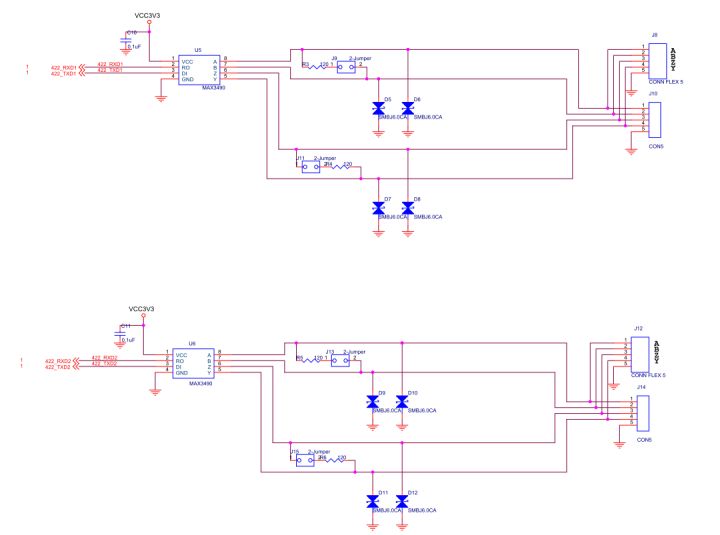

9496 本章利用AN3485模块实现RS422接口数据传输。关于模块,在前面的RS232实验中已经介绍过,本实验不再赘述。RS422与RS232在与FPGA的连接的接口上是一样的,都是TXD和RXD,因此,本实验在RS232实验的基础上,例化出两路连接到RS422接口芯片MAX3490上

2022-02-09 09:49:07 2406

2406

本文介绍如何在 vivado 开发教程(一) 创建新工程 的基础上, 使用IP集成器, 创建块设计。

2022-02-08 10:47:39 2090

2090

了在不增加译码复杂度的情况下实现有效而可靠的通信.通过将各级编解码模块化,利用FPGA技术实现了整个级联纠错编译码系统.实验结果表明,模块化的FPGA嵌入式设计不仅提高了系统的稳定性,还大大缩短了开发周期.

2021-02-01 14:26:42 5

5 RS码在通信领域有着广泛的应用,其中最重要的是关键方程的求解.传统欧几里德算法在求解关键方程时需要进行多项式次数的判断,从而造成硬件电路复杂,译码速度下降.通过对综合除法进行推广,提出了一种改进型

2021-02-01 14:25:00 10

10 结构化LDPC码可进行相应扩展通过对编译码算法,优化编译码结构进行调整,降低了编译码嚣硬件实现中的关键路径迟延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片实现了一个码长10 240,码率1/2的非正则结构化LDPC码编码器和译码器。实现结果表明:该编码器信息吞吐量为1.878 Gb/

2021-03-26 15:58:00 12

12 基于软件无线电的NRLDPC编译码设计与实现。

2021-05-28 10:07:04 5

5 的,特别是在短的中等码长下,性能接近香农限。本文是基于课题的要求,在Quartus II软件中通过调用IP核的方式实现RS编译码过程,并通过Modelsim进行仿真验证。

2022-09-28 10:02:21 2

2 随着工业自动化技术的不断发展,越来越多的工业设备在使用时需要进行数据通信。其中,RS485通信协议是一种常见的工业通信协议,而TCP/IP协议则是互联网通信的标准协议。为了实现RS485协议与TCP

2023-05-05 15:50:44 1687

1687

RS-422/RS-485与RS-232相比有哪些优势?由于RS-422/RS-485使用差分信号,它对噪声的抵抗力更强,可以使用更长的电缆和/或高数据速率,尤其是在嘈杂的环境中。此外,RS

2022-03-22 10:07:59 890

890

那么,它是如何实现这一功能的呢?YC-EIP-RS485/232是一款自主研发的通讯网关,可以在ETHERNET/IP网络中做从站,同时在RS485/RS232网络中做主站或从站,实现数据互通。这款

2023-07-11 09:19:58 601

601

你是否曾经遇到过这样的问题:如何将ETHERNET/IP网络和RS485/RS232总线连接起来呢?

2023-07-30 16:58:23 896

896

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1628

1628

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 1060

1060

主要介绍如何在本地搭建编译环境来编译rockchipBBuildrootllinuxSDK的源代码。d当前sdk只支持在linux环境下编译,并提供linux的交叉编译工具。

2021-12-13 11:23:13 18

18 文章是基于Vivado的 2017.1的版本,其他版本都大同小异。 首先在Vivado界面的右侧选择IP Catalog 选项。

2023-12-05 15:05:02 317

317 多个RS485设备如何实现防水连接 RS485是一种常见的串行通信协议,被广泛应用于工业自动化设备以及各类传感器、仪表等设备之间的通信。然而,在特殊工作环境下,如户外、潮湿或湿润的环境中,防水连接

2024-01-05 14:03:56 215

215 (1769),使用Ethernet/Ip通信接口。为了实现PLC与Ethercat主站单元稳定、可靠通信,客户选择了北京小疆智控的Ethernet转RS232

2024-01-09 16:05:10 142

142

正在加载...

电子发烧友App

电子发烧友App

评论