基于USB2.0与FPGA技术的高速数据采集系统的设计

近年来笔记本电脑迅速普及和更新,其中大部分已经不配置RS232接口,而USB接口已成为今后一段时间PC机与外设接口的主流。本采集系统的设计构建了一个基于USB接口的多功能通用数据采集、传输平台,将嵌入式系统的实时性、灵活性和PC机强大的数据存储、处理、显示功能结合起来。该采集系统在智能仪器仪表、测控系统、工控系统等领域有广阔的应用前景。

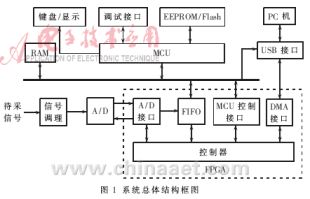

1 系统总体结构设计

1.1 系统总体结构

系统总体结构框图如图1所示,系统包括:单片机与USB接口模块、FPGA模块、信号调理及A/D模块。其中,单片机外围电路相对简单,整个系统主要通过PC机的程序界面控制操作;USB接口负责与PC机通信;FPGA模块负责完成数据的采集与缓存。

1.2 单片机与USB接口模块

本设计的目的是构建以PC机为平台的数据采集系统,单片机的功能仅限于接收PC机的命令、控制FPGA工作。PC机作为整个系统的人机界面,控制整个数据采集系统进行采集、存储和处理。由此单片机可以选择低成本的8XC51系列。为了提高系统的灵活性,采用单片机与USB接口芯片分离的方案,选择Philip公司的ISP1581 USB2.0接口芯片。该芯片与8XC51系列单片机的接口非常简单,可以极大地降低系统成本。

1.3 FPGA模块

采用FPGA进行采样控制的最大特点是系统具有重构性和通用性。设计中采用了Altera公司的低成本FPGA的Cyclone系列(实际试验时,在更便宜的Acex1k器件上也可以实现),控制高速A/D芯片以20MSPS的速度采样。FPGA模块的设计具体包括FIFO、单片机接口、A/D控制接口、DMA控制模块和主控制器等子模块的设计。

1.4 PC机端软件平台

PC机采集程序使用VC++实现,直接调用Philips公司提供的驱动程序进行数据读写,大大降低了开发难度与风险。本设计中,PC机端软件设计包括应用程序的界面设计、多线程数据采集、存储与处理模块的设计,以及与USB底层驱动程序的通信动态链接库的设计。

2 USB接口模块设计

2.1 USB接口芯片

USB接口芯片ISP1581具有体积小、高速、与单片机的接口相对简单等特点。除了控制端点外,ISP1581还有7个输入(IN)端点和7个输出(OUT)端点。每个端点可以灵活配置数据传输方式以及数据缓存区(FIFO)的大小,端点FIFO最大容量可以达到2KB。ISP1581芯片在配置枚举时需要单片机固件的支持,一旦正确完成了配置和驱动加载,单片机对于ISP1581芯片就如同普通存储器一样可以进行读写操作,以发送或接收数据。

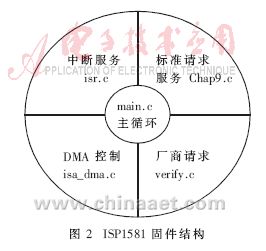

2.2 固件编程

USB通信完全由PC主机发起。在这种结构下,固件总是一直在等待主机命令,再根据命令去执行相应的程序。固件的基本思想是采用模块化设计,分成 main.c等7个模块。ISP1581固件结构如图2所示。图中,main.c为主循环,isr.c主要负责中断处理,Chap9.c主要负责响应主机的请求。用户的应用程序将来也可以包括在main.c循环中。

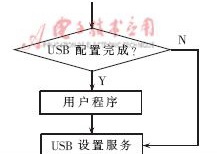

2.3 单片机端程序设计

单片机端程序主要包括初始化模块,外围Flash、EEPROM、RAM、液晶显示器、按键等的读写控制模块,USB接口芯片固件模块,A/D采样工作模式、速度以及采样数据的读写的FPGA硬件控制模块等。本设计的指导思想是:充分利用PC机和嵌入式系统的优点,对MCU端的要求尽量简化。具体软件流程示意图如图3所示。

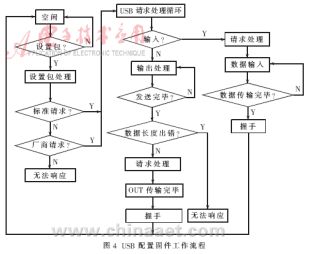

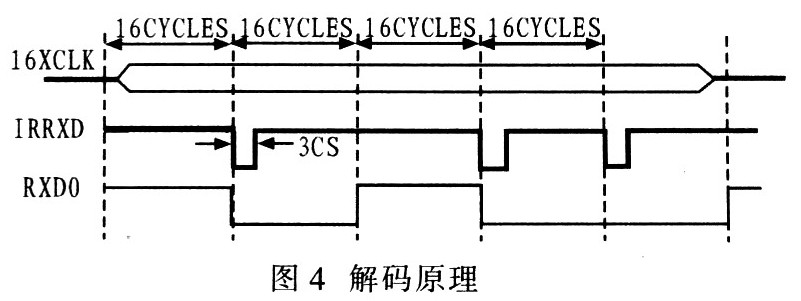

USB作为一个通信接口,首先必须完成配置,然后才能进行用户数据的发送/接收,在循环中必须随时检查是否有主机的配置命令。配置枚举过程是USB固件编程当中较为复杂的部分,其流程如图4所示。USB设备接入到主机并被主机识别后,主机首先以默认的地址(00H)发送一个设置(SETUP)包,新接入的设备必须接收此包并响应请求。然后主机会发送输入包读取设备描述符,初步判断设备的属性后,再设置设备的地址,随后再用这个地址读取设备的各种描述符以识别并且配置设备。可见,在设备配置过程中,主机读取的数据较多,设备一旦接收到一个SETUP包之后便会判断主机的请求类型,然后进入请求处理循环等待主机的进一步命令,如果再次收到一个IN令牌便会向控制端点中写入数据,并且根据数据长度再次写端点直到数据发送完毕。USB的标准请求包括读取设备描述符、配置描述符、端点描述符、设置地址、配置设备等,厂商请求由用户自行定义。

ISP1581接收到主机的数据后,将根据相应的情况设置片内的中断寄存器标志中断源,然后向单片机申请中断,中断服务程序流程如图5所示。单片机响应中断后,首先读取中断标志寄存器并判断中断源,然后设置相应的标志。在用户的发送/接收程序中,将根据相应的标志产生相应的动作。例如,主机发送一段数据给ISP1581,ISP1581接收、握手完毕后,设置中断标志并申请中断。在用户的任务中发现有数据接收的标志,就可以读出ISP1581中的数据。而ISP1581向主机发送数据时,首先是主机发送一个IN类型的令牌发起一次传输,如果此时ISP1581相应端点的FIFO非空,则立即发送数据,然后向单片机申请中断,响应中断以后如果还有数据要发送,则应该向ISP1581的FIFO中写入数据,否则直接清空中断标志即可。主机和数据采集器之间的握手配合要事先设计好。

根据输入传输要求,在具体的设计中,除了主数据传输端点外,还配置了一个数据缓冲区为64字节的、工作于中断传输方式的端点作为命令端口,负责与主机进行通信握手。如果主机想从设备读取数据,则首先发送一个读取命令,单片机接收到该命令后,就向主数据端点的FIFO中写入数据,随后主机发出读数据令牌,正好有数据可以发送。通过命令端口还可以发送各种命令,控制数据采集器动作。

3 FPGA数据采集模块设计

3.1 模块划分

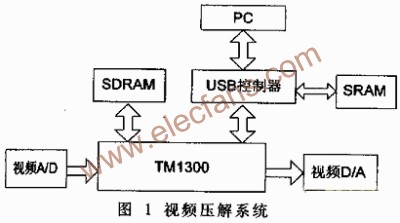

FPGA模块划分为A/D接口、FIFO、单片机接口、DMA接口控制、主控制器等模块,其中设置了一些可以单片机写入的寄存器。A/D的采集速度,FIFO的空、满、数据写入、读出速度都可以灵活配置。整个模块以Verilog语言写成,稍加修改可以同各种A/D芯片接口。整个设计在Altera公司的Cyclone系列的EP1C12中完成。在ACEX1K系列EC1K100器件上也可以实现,工作时钟频率为50MHz。

为了提高系统的灵活性,在信号的调理、滤波模块中使用了Lattice公司的ispPAC80可编程滤波器作为输入滤波器,可以灵活地设定抗混叠滤波器的截止频率,最大截至频率可以达到750kHz,完全可以满足一般中、高频信号的滤波。FPGA作为A/D控制器可以同多种A/D芯片接口,本设计中使用了TI公司的10位高速A/D芯片TLC876。芯片工作于流水线方式,最高采样速率为20MSPS。

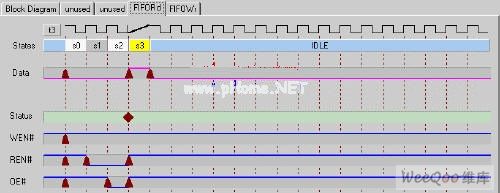

3.2 与单片机及ISP1581的接口

FPGA在与单片机信号的接口过程中,使用了同步设计的方法。即首先对单片机的I/O信号进行采样同步化,获得各信号上升、下降沿的时刻,输出同步脉冲,然后在这些时刻点处根据同步脉冲的出现与否来控制系统进行动作。这种设计的优点是可以在设计中采用同步状态机,以获得较高的运行速度和稳定的工作性能。这也是ALTERA、XILINX等公司的FPGA数字系统设计中所推荐使用的方法。

为了提高FPGA中的FIFO与ISP1581中的数据存储器的数据交换速度,FPGA与ISP1581之间采用DMA方式进行数据交换。

ISP1581有两种工作方式,由BUS_CONF、MODE0、MODE1三根引脚控制:

(1)如果上电时检测到BUS_CONF引脚为低电平,则工作于分裂总线方式(Split Bus Mode)。ISP1581具有8-bit地址/数据复用总线和16-bit的DMA专用数据线。此时MODE1引脚如果为低电平,则可以将芯片的ALE/A0引脚与89X51的ALE脚直接相连,进行地址/数据总线复用;而如果MODE1为高电平,则ALE/A0脚要接其他的89X51引脚,由用户编程将ALE/A0脚拉高/低进行地址/数据复用,而MODE0脚在这种方式下没有使用或作为其他用途。

(2)如果上电时检测到BUS_CONF引脚为高电平,则工作于通用处理器方式(Generic Processor Mode)。此时MODE1脚没有使用(可接Vcc),MODE0引脚则可接低/高电平,这样可以使芯片的读/写引脚分别符合Motorola/89X51微处理器的读写规范。所以让ISP1581芯片工作于分裂总线方式可以方便地与8051系列单片机接口,其AD[7:0]作为数据/地址总线复用,RD、WE、ALE分别为读、写、地址锁存线,DATA[15:0]作为DMA数据总线使用。

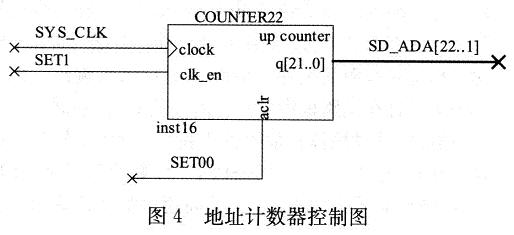

ISP1581芯片中与DMA相关的引脚有DREQ、DACK、DIOR、DIOW。DMA传输前必须设定工作模式、初始化DMA相关寄存器,然后对DMA命令寄存器写入一个命令便可以启动DMA传输。传输模式有主、从、IDE、ATA等方式。通用数据采集系统比较适合采用从模式,在这种模式下,单片机接收到主机发来的开始采集命令后,立即命令FPGA启动采样,然后命令ISP1581启动DMA传输,ISP1581将DREQ引脚拉高,表示请求数据,此时FPGA将数据准备好后,拉低DACK引脚,待准备好数据后,在DIOR线上产生读脉冲,供ISP1581将数据读入内部FIFO。DMA也可以使用主模式,此时读脉冲DIOR由ISP1581产生。DMA工作时序图如图6所示。

4 PC机多线程数据采集程序设计

USB的数据传输使用了虚拟管道的概念,可以同时接入127个设备。每个设备可以拥有若干个端点,每个端点可以跟主机组成一个连接,构成一个通信的最小实体。在数据传输过程中,只要带宽允许,主机可以同时跟几个端点通信,因此要求在主机的应用程序中开启多个线程进行通信。在本设计中,采用了命令端点和数据端点分开的方式。命令端点配置成中断或批量传输方式,在主机应用程序中专门开启一个线程同该端点进行通信,开启另外一个线程进行采样数据传输,而两个传输之间互相不影响。用户界面使用另外的线程,这样在传输过程中,应用程序可以随时响应用户的命令。在具体的设计中,点击数据采集开始命令即建立并且启动一个采集线程。在这个无限循环的线程函数中设置了一个标志变量,如果该变量为真,则线程函数继续运行;否则线程终止,停止采集。这样用户界面线程可以通过修改线程运行标志变量来控制线程的运行。采用多线程采集程序的一个问题是线程函数必须是一个全局函数,不属于任何一个类,这样它就无法访问类的私有成员或保护成员,解决这个问题的方法是:因为线程函数在创建时允许传送一个指针参数给它,于是可以构造一个结构数据类型,数据成员中包含一个指向类的指针。在创建线程时将想要访问的类的指针包含在一个按前述定义的结构变量中,并将该结构的指针作为参数传给线程函数。这样就可以在线程函数中定义一个类对象,并把前述的类指针赋给它,通过类指针就可以访问该对象中的所有成员了。在本设计中采用多线程程序设计后,系统工作非常稳定。

目前,国内外的数据采集系统常用的接口方式有多种,如 RS232 串行口、并行口,ISA 总线、PCI总线等。这些总线接口虽各具优点,但也都有其难以克服的缺点而被逐渐淘汰。USB接口具有连接方便、无需外接电源、即插即用、支持热插拔、动态加载驱动程序等特有优点,在主机和数据采集系统之间可以实现简单、快捷、可靠的连接和通信。本设计应用ISP1581USB接口芯片与FPGA技术,构建了一个使用灵活的通用数据采集系统。该系统充分利用了PC机的大存储量,强大的数据处理能力,高清晰的大屏幕显示(相对于嵌入式系统而言),以及嵌入式系统的实时与灵活性。目前正在使用此平台构建一个在消声室环境中针对机械振动噪声的采集与分析系统。此系统在智能仪器以及工业自动化等众多领域中必将有广泛的应用前景。

参考文献

[1] 萧世文. USB2.0硬件设计[M].北京:清华大学出版社,2002.

[2] 周立功.PDIUSBD12USB固件编程与驱动开发[M].北京:北京航空航天大学出版社,2003.

[3] 张念淮. USB总线接口开发指南[M].北京:国防工业出版社,2001.

[4] Philips Semiconductors. ISP1581 programming guide[Z].2004.

[5] USB.org. Universal serial bus specification rev.2.0[Z].2006. http://www.usb.org/developers/docs/.

[6] 倪明辉. USB在FPGA控制的高速数据采集系统中的应用[J]. 计算机测量与控制,2006,14(2).

电子发烧友App

电子发烧友App

评论