随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2204

2204

最近准备采用Xilinx FPGA进行多机通信,即主FPGA芯片将采集到的不同层的图像数据流分别输出给对应的4块从FPGA芯片中,主从FPGA之间的连接机制采用星形拓扑结构。经计算,图像数据流接口速率需要数百兆比特/秒,因此需要调研FPGA支持的常见IO接口标准,及每种接口的应用场合。

2022-10-17 09:14:18 1626

1626 比特流是一个常用词汇,用于描述包含FPGA完整内部配置状态的文件,包括布线、逻辑资源和IO设置。大多数现代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

733 24合1视频桥接芯片RK628D有哪些优势呢?24合1视频桥接芯片RK628D有哪些应用呢?

2022-03-02 09:40:31

6678的pcie和fpga的pcie TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

2018-06-21 15:49:12

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA I/O结构中没有包含均衡功能,那么它与DDR3

2019-04-22 07:00:08

大家好,FPGA在媒体流处理方面有哪些优势,有哪些成熟案例,谢谢!

2009-02-09 20:19:28

,FPGA必须提供符合成本效益的非常小的外形尺寸,以适应现代摄像机对于紧凑外形的要求。 具有完备子LVDS文档支持的LatticeXP2非易失FPGA系列已被证实解决了图像传感器桥接的电气需求。集成

2011-05-24 14:17:00

对更高密度和更快速度配置存储器的需求。现代FPGA在配置期间需要加载多达128MB的数据。这些高密度配置比特流需要更长的时间才能从NOR闪存器件传输到FPGA。配置接口不仅针对读取吞吐量进行了优化,还

2021-09-03 07:00:00

嗨,大家好,只是一个简单的问题。 FPGA编辑器是否有限制为包含嵌入式处理器(如PowerPC)的设计生成比特流?我问的原因是因为我在Project Navigator中创建了一个设计并运行了PAR

2018-10-18 14:44:29

顾名思义,桥接T衰减器具有一个额外的电阻元件,该电阻在标准T焊盘的两个串联电阻之间形成了桥接网络。这种附加的电阻性元件使电路能够通过所需的衰减来降低信号电平,而无需改变电路的特性阻抗,因为信号似乎

2020-11-18 09:30:08

这几年有点背,逐渐远离主流话题,所以有人就有了这样的问题:DSP会被FPGA取代吗?小编总结了各个网友的回答: 网友一:独立的DSP不会被FPGA替代,但是会被增强了信号处理功能的ARM处理器替代

2021-07-16 08:12:03

领域。本文基于雷达实时信号处理的需要,用FPGA实现了多DSP信号处理模板局部总线和基于标准VME总线的计算机进行通信的接口设计。 2 VME总线的功能特点VME总线系统的功能结构可以分为4类:数据传输

2019-04-22 07:00:07

问一下你们A40i硬件手册上核心板的mipi管脚GPIO跟电压都划了横线,是没有接出来吗?你们自己的mipi屏幕是接mipi dsi接口还是接lcd的接口的,我看到硬件手册里面标明Mipi接口写了TBD,但是你们自己又又mipi屏幕,是怎么回事?

2022-01-05 06:53:42

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

[2018-08-26]-[CentOS]CentOS静态IP配置(桥接模式)

2020-05-12 08:27:02

在DisplayPort之前,数字多媒体接口标准经历了多次纷争,逐渐形成了外部连接(Box-to-Box)与内部连接(Chip-to-Chip)两块相互独立的阵地。在外部连接方面,PC已有DVI;而

2019-04-09 07:00:08

在过去的几十年的硬件设计里,这个词对国人来说非常陌生,特别是我们50HZ、60HZ系统。何谓桥接?维基百科中的解释是关于通讯网络协议的。桥接是指连接两个不同系统之间的桥梁,英文简称“bridged

2022-02-20 07:00:00

哪位大侠实现过用FPGA实现GPIB接口的 麻烦给小弟些指导,我用的SPARTN2的XILINX的芯片

2013-11-21 17:04:08

LVDS的多媒体特性是什么?LVDS多媒体接口在汽车电子领域的应用前景如何?

2021-05-12 06:51:50

IEEE 802.3 规范提出媒体无关接口(Media Independent Interface,MII)就是为了能够实现 MAC 层和不同的物理层(PHY)之间的逻辑连接,如图 10-5 所示

2018-12-27 11:23:20

信息:下载使用24 VAC电源的UART至Wi-Fi桥接 (TIDA-00375) 参考设计,获得设计指南、电路原理图、测试数据、设计文件、物料清单等。对于使用RS-485接口的设计,请参见针对24

2019-08-06 04:45:01

富士通微电子(上海)有限公司日前宣布推出业界领先的USB 3.0 - SATA (*1) 桥接(*2)芯片。该芯片支持超速USB和USB 3.0规范(*3),并能在外置存储器件(如磁盘驱动器HDD)和PC之间进行高达5Gbps的数据传输。

2019-08-26 08:28:21

TUSB9261 -- USB3.0转SATA接口桥接芯片 烧录指南

2021-01-07 06:26:20

我用的wifi安装14.04的ubuntu,用桥接可以无线上网。想用桥接有线上网,但是找不到可以桥接到有线网卡的选项。希望大家帮帮,谢谢。

2016-10-13 22:08:48

描述桥接 T 鼓合成器振荡器这是一个双桥接 T 振荡器,可用于使用外部触发器创建模拟鼓和其他打击乐合成器声音。当用脉冲触发时,输出将产生一个消散的瞬时正弦波振荡,通过调整每个振荡器上的电位器,可以将音高调整为听起来像低音鼓、木块等。PCB

2022-07-26 07:56:32

大家好,我在设计中使用了Artix 7。更确切地说,我使用的是XC7A35T-2FTG256I,但是我的资源不足。我想用aXC7A75T-2FTG256I替换它。我有两个问题:1)它是否真的是替代品,我已检查数据表,它似乎是。2)如果我用两个FPGA编译完全相同的代码,结果比特流会不同?谢谢,保罗

2020-08-17 06:15:11

低功耗FPGA的开发板,以及LatticeXP公司的高级开发板(见图2)等。 QuickLogic MAB售价999美元,可以连接到英特尔PXA27x处理器开发套件。这款MAB基于QuickLogic

2012-04-27 14:40:21

嗨,我正在尝试部分自我重新配置。想法是通过介质将部分比特流发送到FPGA。FPGA接收它(在多个块中)并将比特流写入ICAP。当连接发生时,我的FPGA的行为会发生什么发送部分比特流中途消失了?我

2019-02-14 09:40:06

为什么会出现eth3没有eth0的?我用桥接方式为什么都ping不通用NAT方式 就可以ping通但虚拟机还是和开发板PING不通。

2019-10-24 03:28:16

二三层桥接为何是LTE承载的关键技术?

2021-05-24 07:17:37

(Automated Imaging AsSoCiaTIon)开发的相机接口标准。这是一项开放性的标准,它能让来自不同厂家的摄像机与应用软件通过吉比特以太网实现相互间的无间合作。Gige Vision

2019-05-05 08:30:00

案例中,这样的平台需要进行一定的调整以满足汽车制造商的需求。而使用FPGA可以快速实现低成本桥接解决方案,使得现有平台能够完美应用于汽车领域。

2019-07-23 07:57:39

MAX9286吉比特多媒体串行链路(GMSL)解串器接收多达四个GMSL串行器的数据,采用50Ω同轴电缆或100Ω屏蔽双绞线(STP)电缆,通过四个CSI-2通道输出数据。每条串行链路具有嵌入式控制

2018-02-02 15:10:14

VMware使用桥接模式,已经手动设置ip地址和主机ip同一网段,但是ifconfig显示的ip地址却和vmnet8(NAT)同一网段?怎么解决?

2014-10-16 15:06:02

的处理器,优化了性能和成本通过不同的电压和各种接口,如SPI、I2C、SDIO、PCI和LPC之间的桥接,最大化组件选择的灵活性莱迪思FPGALCMXO2-640HC-4TG100C可编程逻辑器件FPGA

2019-09-20 15:13:30

本文介绍了一种基于 FPGA 技术的IDE 硬盘接口的设计。该卡提供两个符合ATA-6 规范的接口,采用FPGA 实现了两套IDE 接口功能,设计支持PIO和Ultra DMA 传输模式,文章侧重于介绍用FPGA 实现IDE 接口协议的具体方法。

2011-01-12 14:38:42

`1 背景知识像素是由比特组成的数字。例如,在256级灰度图像中,每个像素的灰度是由8比特(也就是1个字节)组成。一幅8比特图像可以认为由8个1比特平面组成,如图1所示,其中平面1包含图像中所有像素

2018-08-14 09:07:22

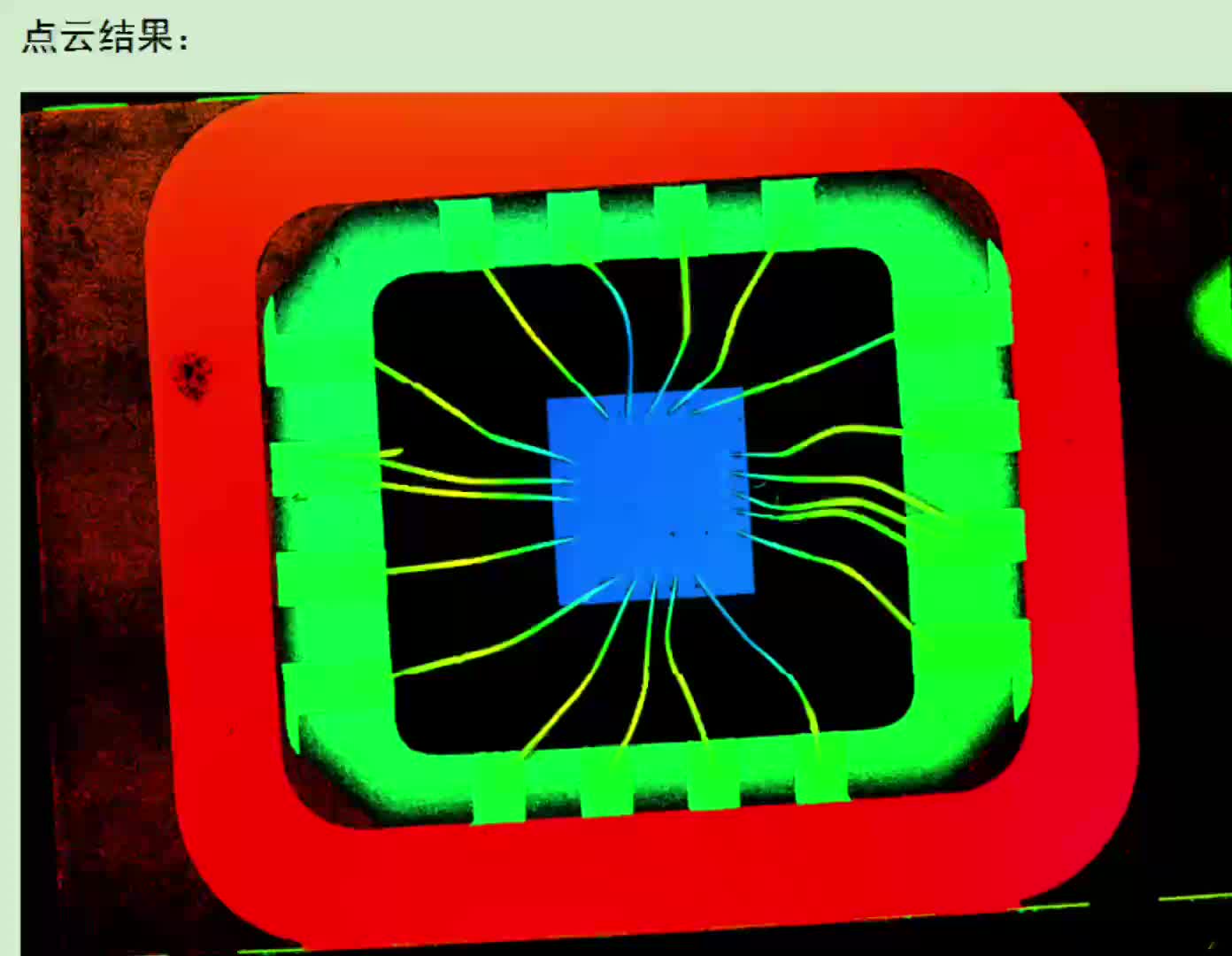

Imaging的HiSPi串行接口至TI DSP并行接口的桥接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解决方案,如图4所示。该参考设计在输入端用HiSPi串行接口,在输出端用TI

2019-06-04 05:00:19

Imaging的HiSPi串行接口至TI DSP并行接口的桥接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解决方案,如图4所示。该参考设计在输入端用HiSPi串行接口,在输出端用TI

2019-06-06 05:00:37

TI DSP并行接口的桥接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解决方案,如图4所示。图4 基于FPGA的串行传感器桥接参考设计示例 该参考设计在输入端用HiSPi串行

2018-11-05 11:08:31

是一种由AIA(Automated Imaging AsSoCiation)开发的相机接口标准。这是一项开放性的标准,它能让来自不同厂家的摄像机与应用软件通过吉比特以太网实现相互间的无间合作。Gige

2013-09-04 12:14:55

移动应用程序设计的图像传感器,则需要转换桥接逻辑。例如,针对嵌入式或数字静态相机市场的图像传感器通常具有子LVDS或不是CSI-2(相机串行接口)的其他专有接口。与CSI-2发送参考设计并行,使设计人

2020-05-01 11:56:40

、100Mb/s和1Gb/s三种不同速度的以太网协议接口控制。本文将主要讨论如何使用这两个TSEC实现吉比特以太网接口。吉比特以太网物理层协议及接口参考文献上对于网络协议的介绍往往局限于对协议分层的理论分析

2018-11-30 11:27:55

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

多媒体的FPGA实现PDF

2015-10-26 21:14:05

你好,请有人解释我如何使用IMPACT在FPGA xilinx中下载比特流先谢谢你以上来自于谷歌翻译以下为原文hello,please can someone explain me how

2019-01-15 10:08:59

大家好,我想使用USR_ACCESS_VIRTEX4原语来访问存储在配置闪存中的其他比特流。情况如下:我有一个主FPGA(Virtex-4FX)和一个从FPGA(Spartan-3A)。从属FPGA

2020-05-29 10:14:55

如何利用FPGA实现低成本汽车多总线桥接?

2021-04-29 06:51:23

请问如何利用FPGA嵌入式实现多比特自相关器的设计?

2021-05-06 09:47:25

基础的多路复用器/解复用器应用,现成的标准模拟开关可能就能满足需求。 但随着设计人员执行一些更加复杂的桥接任务,如转换不兼容的接口、组合多个视频流、或将视频流拆分至多个接口,基于 FPGA 的可编程桥接

2017-04-06 13:48:17

如何采用RS232总线实现计算机和桥接卡之间的通讯?使用FPGA实现I2C总线时需要建立那几个模块?

2021-05-07 06:01:08

你好我有一个在MIcroBlaze上运行linux的设计要求。我能够在我的Virtex-7 FPGA上下载比特流(在Vivado 2014.4中生成)。我使用Impact来编程我的FPGA。我因此

2020-04-02 10:05:40

我在使用EDK 10.1中的微填充处理器在FPGA中下载比特流文件时遇到问题。我只是将Microblaze processsor比特串文件下载到FPGA中(斯巴达3a dsp)...连接的要求是什么?我有JTAG和一个串口....什么是stepi必须遵循。

2020-03-30 10:07:31

对MOS管的驱动电路形式,常用推挽式电路,增强驱动能力而功率放大的电路形式,常使用全桥或者半桥的电路形式,放大功率同样是要接外接供电电源,为什么驱动用推挽,功放用全桥半桥?如果交换电路形式呢?谢谢

2020-07-15 01:34:51

对MOS管的驱动电路形式,常用推挽式电路,增强驱动能力而功率放大的电路形式,常使用全桥或者半桥的电路形式,放大功率同样是要接外接供电电源,为什么驱动用推挽,功放用全桥半桥?如果交换电路形式呢?谢谢

2017-02-16 14:02:13

的时候,一个全新的无线吉比特联盟(Wireless Gigabit Alliance)悄然成立了,这一无线联盟仅用不到一年的时间就完成了新千兆无线网络标准的制定工作,并于2010年5月颁布了

2019-07-03 07:02:27

嗨专家, 我正在使用spartan-6 FPGA进行多重启动实验。我发现位文件位于ug380上,如下图所示。黄金比特流位于闪存的下部块上,多重引导比特流位于闪存的较高块上。 因此,如果我想使用保护区

2020-06-09 17:43:26

求解整流桥接法,图中的这种整流桥怎么接?

2016-10-24 16:40:18

瑞芯微发布24合1视频桥接芯片RK628D RK628D支持三种输入接口,九种输出接口,仅一颗芯片即可实现多达24种视频传输转换接口的组合。RK628D可应用于六大场景包括多屏商显、4K大屏转接

2022-05-31 09:13:25

MIPI CSI-2接收桥参考设计。灵活的MIPI(移动行业处理器接口)CSI-2接收桥 - 允许移动CSI-2(摄像机串行接口)图像传感器连接到嵌入式图像信号处理器ISP。经过测试,在HDR-60

2020-04-29 09:39:43

索尼Sub-LVDS到MIPI CSI-2传感器桥参考设计。索尼图像传感器的桥接解决方案 - 它创建了一个参考设计,将串行Sub-LVDS接口与MIPI CSI-2连接起来,从而使设计人员能够将

2020-04-30 06:13:19

方案,完成了十接口千兆线路接口卡的设计与实现,研制的千兆线路接口卡完全满足了T比特路由器项目对十接口千兆线路接口卡设计的功能与性能要求。采用FPGA设计并实现了十接口千兆以太网线路接口卡设计与实现中

2019-04-29 07:00:07

1.产品概述WK2124是SPITM接口的4通道UART器件,WK2124实现SPI桥接/扩展4个增强功能串口(UART)的功能。扩展的子通道的UART具备如下功能特点:每个子通道UART的波特率

2023-11-24 00:17:37

Altera Stratix IV FPGA继续广受全球媒体好评

Altera公司今天宣布,40-nm Stratix® IV FPGA系列最近荣获电子编辑媒体的多个奖项。Stratix IV系列因其在密度、性能和功耗上的优

2010-02-24 09:44:20 1198

1198 MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统接口

概述

MAX9249串行器带有LVDS系统接口,采用Maxim吉比特多媒体串行链路(GMSL)技术。MAX9249串行器与GMSL解

2010-03-28 09:17:58 1067

1067 MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统接口

概述

MAX9249串行器带有LVDS系统接口,采用Maxim吉比特多媒体串行链路(GMSL)

2010-05-20 08:51:48 787

787 本文介绍了LatticeXP2系列主要特性,LatticeXP2-17器件简化方框图,LatticeXP2标准评估板主要特性和LatticeXP2标准评估板电路图。

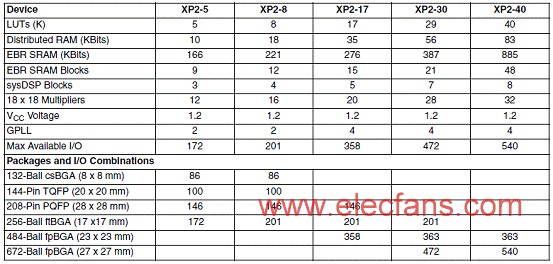

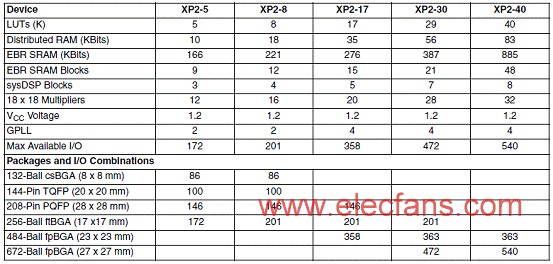

Lattice 公司的LatticeXP2器件包括基于查找表(LUT)的

2010-08-25 15:06:34 1279

1279

LatticeXP2器件将基于FPGA结构的查找表(LUT)与闪存非易失单元组合在一个被称为flexiFLASH的架构中。 flexiFLASH方式提供了许多优点

2011-03-28 10:20:17 1354

1354 本文通过对该接口的分析,提出了解决该接口设计难点的方案。以上方案经过FPGA布线后仿真测试,证明是切实可行的。

2012-01-24 18:08:19 708

708 基于FPGA的SDI接口设计,學習FPGA的好資料!!!!

2016-06-06 10:00:46 29

29 Zynq开发板FPGA比特流文件可以通过三种途径下载: 1. 利用SDK生成的FSBL.elf文件自动加载FPGA比特流配置文件,将比特流文件,FSBL.elf文件和u-boot.elf文件利用

2017-02-08 15:20:09 895

895 基于比特币的媒体区块链面临着一个巨大的挑战。传统上,比特币无法像一些区块链开发者和用户所希望的那样进行无缝扩展。它在这方面的局限性引发了对比特币媒体区块链未来的质疑。这还增加了像以太坊这样的替代区块链在媒体市场上超越比特币的可能性。在媒体区块链公司在成长过程中,需要将扩展的因素放到他们的考虑计划中。

2018-09-27 14:41:26 387

387 关键词:Lattice , LVDS视频接口 Lattice公司的LatticeECP2 7:1 LVDS视频评估套件采用LatticeECP2 或LatticeXP2 FPGA

2019-03-20 12:50:01 956

956 在FPGA上设计了一种波特率连续可调的UART接口,该接口符合RS-232C通信协议。将波特率转换为比特持续时间,在固定工作时钟频率下通过改变比特持续时间来实现波特率的连续可调,并将比特持续时间

2021-06-01 09:56:05 10

10 FPGA和外围接口-基础版

2023-05-22 10:57:24 568

568

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2023-07-27 16:10:01 1565

1565

电子发烧友网站提供《使用加密保护7系列FPGA比特流.pdf》资料免费下载

2023-09-13 15:31:19 0

0

电子发烧友App

电子发烧友App

评论