pci总线是高速同步总线,采用高度综合优化的总线结构,目前广泛应用于各种计算机系统中,总线以32位(或64位)数据总线、33mhz(或66mhz)的时钟频率操作,具有很高的数据传输速率。

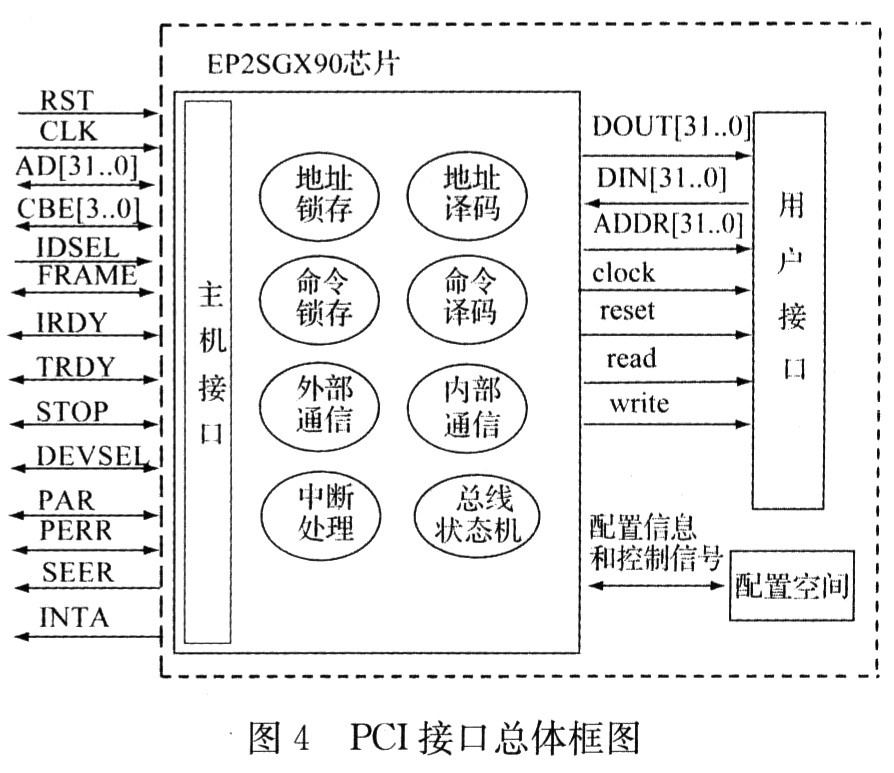

目前开发pci接口大体有两种方案,一种是采用专用的pci接口芯片,实现完整的pci主控模块和目标模块接口功能,将复杂的pci总线接口转换为相对简单的用户接口。采用这种方案,用户只要设计转换后的总线接口即可,其优点是缩短了开发周期,缺点是用户可能只用到pci接口的部分功能,因此而造成逻辑资源浪费,缺乏灵活性。一种是使用可编程器件,采用fpga进行pci接口设计,这样可以依据插卡功能进行最优化。这种方案设计灵活,不必实现所有pci功能,节约系统的逻辑资源。

本文所述设计方案是采用xilinx公司的virtex2系列xc2v6000芯片来实现pci主/从设备接口控制器。通过pci总线使得计算机上的视频码流传送到解码器中。对fpga的设计全部采用verilog hdl语言作为设计输入,并且为解码部分功能的实现预留了足够的空间。

系统结构设计

为了对视频流进行解码,需要快速而大量的数据传输。本设计简述了一种通过pci总线通信的解决方案。通过host主机对目标设备的控制,实验板即可以做目标设备,也可以做主设备。图1是本设计的系统框图。

在默认情况下,实验板目标设备处于工作状态为主设备为空闲状态,主控host通过i/o方式进行寄存器的读写控制操作。当需要传输大量数据时,host通过写i/o方式通过实验板申请pci总线的使用权,pci总线申请成功后,实验板主设备开始工作,通过dma方式与主控host进行通信。

pci总线配置空间的实现

当实验板的目标设备工作时,需要对其配置空间进行配置。pci总线定义了3种物理地址空间:存储器地址空间、i/o地址空间和配置地址空间。前两者是普通的计算机系统地址空间,而配置空间是pci所特有的。根据pci总线规范[1],所有的pci设备都必须提供配置空间。pci总线仲裁器首先访问一个目标设备的配置空间,以确定总线上存在的设备,主机host才能继续对这个目标设备进行其他类型的访问,如内存访问、i/o访问。配置空间是长度为256字节并且有特定记录结构或模型的地址空间,可以在系统自举时访问,也可在其他时间访问。配置空间访问时,对配置空间读令名为“1010”;对配置空间写命令为“1011”。依据pci规范[1],可设定配置空间中的各寄存器值如下:

供应商id:9918h;设备id:2003h;修订id:01h,分类代码:078000h。这是一个非标准pci设备,所以任意使用了一个保留值。

命令字:0001h。表示只支持i/o读写控制。

基地址寄存器:目标设备只用到一个基地址寄存器,在此基础上实现多个寄存器,定义控制寄存器地址为:基地址+2ch;数据传输寄存器地址为:基地址+18h。

其他没有用到的配置寄存器在读时全返回0。

主设备工作机制

主控host首先分配两个内存空间,一个用于存放地址信息,一个用于存放真正的数据。当实验板做主设备时,数据传输使用dma方式对存储器空间直接进行读写操作,数据传输结构如图2所示。

主设备先进行存储器读操作,以从内存空间1中读取主控host分配的pageaddr和pagecnt。主设备得知内存空间2的地址后,即可在传输数据时,读取或者写入到这些真正的数据存储区。实验板做主设备时,为了不和主控host上的其他主设备冲突,设定突发长度为8,传输8个32位数据后释放pci总线,然后开始申请总线使用权,以便继续传输数据。上述操作均由时序状态机进行控制。

主设备时序状态机

时序状态机是pci接口控制器的核心,各种令名、数据交换、控制均在状态机的管理下进行工作。图3是实验板做主设备时,pci总线接口控制器时序状态机。实验板做目标设备的状态机就不在这里介绍了。

这一状态机共有8个状态,分别是:mstate_idle、mstate_req、mstate_addr、mstate_data、mstate_last、mstate_addr_p、mstate_data_p、mstate_last_p。他们代表总线作业时的不同阶段,意义如下:

mstate_idle:主设备空闲状态。实验板目标设备工作,当host通过写i/o方式通知目标设备需要开始以dma方式传输大量数据时,start信号有效,主设备开始申请总线使用权,状态跳转到mstate_req。

mstate_req:主设备开始申请总线使用权状态。主设备开始申请总线使用权,使连接到仲裁器上的req_o_信号有效,通知仲裁器实验板的主设备需要使用pci总线,等待仲裁器的裁决。实验板主设备得到可以使用总线的通知时,必须等到前一个正在占用总线的主设备完成其传输,并且释放总线后,才能真正使用pci总线,即实验板主设备需要采集到frame_i_无效并且irdy_i无效。当pagecnt=0表示一页数据已经传输完毕,于是开始读取下一页数据的存放地址,状态跳转到mstate_addr。当pagecnt!=0表示一页数据还未传完,状态跳转到mstate_addr_p,继续这一页数据的传输。

mstate_addr:主设备页地址状态。这个状态frame_o_信号有效,开始地址周期,ad上出现的是32位页地址信息,cbe_o_上出现的是存储器读命令,这个状态是准备做存储器读操作,在总线上送出地址后,跳转到mstate_data。

mstate_addr_p:主设备数据地址状态。这个状态同mstate_addr状态一样的是,开始地址周期。所不同的是ad上出现的是在mstate_data状态下读到的32位数据地址信息。根据需要,可以进行读/写存储器操作。

mstate_data:主设备读页信息状态。这个状态是读存储器,irdy_o_信号有效。数据真正的传输是在trdy_i_信号和irdy_o_信号同时有效时,可以读取到数据是页信息,代表存放数据的地址信息和存放数据的长度。数据传输的突发长度是2,所以一次pci访问读取两个32位数据,读完一个数据后状态立即跳转到mstate_last去读取最后一个数据。当host主机要求停止数据传输时,通过使stop_i_信息有效告诉主设备,主设备必须放弃这次数据的传输,状态跳转到mstate_last。

mstate_data_p:主设备读/写数据状态。这个状态是数据的传输,突发长度是8,一次pci访问可以读取8个32位数据,当cnt=2时,表示读完7个数据,状态跳转到mstate_last_p。与状态mstate_data一样,如果host主机要求停止数据传输时,主设备必须放弃这次数据的传输,状态马上跳转到mstate_last_p。

mstate_last:主设备读取最后一个页信息状态。该状态下frame_o_信号无效,irdy_o_信号有效,表示这是最后一个读取数据周期,数据传输和mstate_data状态一样,是在trdy_i_信号和irdy_o_信号同时有效时。当host主机要停止数据传输时,stop_i_有效,主设备释放总线并回到mstate_idle状态,准备开始申请下一次总线使用权,以进行数据传输。

mstate_last_p:主设备读取最后一个数据状态。这个状态同mstate_last一样,读取的是这次pci访问的最后一个数据。

下面是用verilog hdl描述的状态机的核心代码:

结束语

本文介绍了在fpga上实现pci接口控制器的设计方案,通过实验板做主设备进行大量数据的高速传输。采用对主控host内存的直接读/写进行数据传输,用突发方式使用背靠背单数据传送,在时钟频率33mhz下,数据流量接近每秒33百万次传送,实验中数据传输效果很好,完全符合pci总线的要求,这种设计提供了灵活的接口控制,为后续的视频解码ip核提供了良好的接口。

电子发烧友App

电子发烧友App

评论