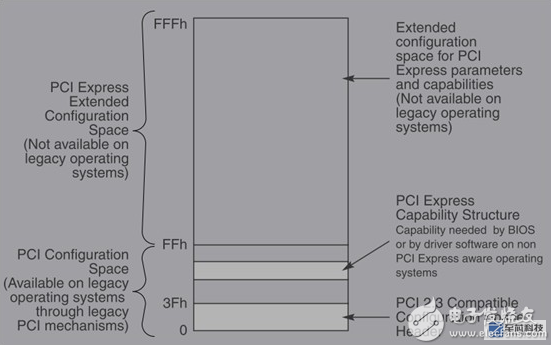

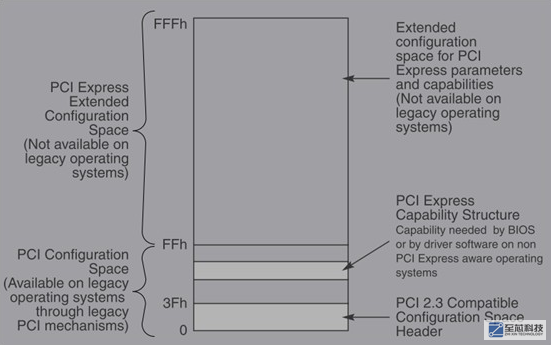

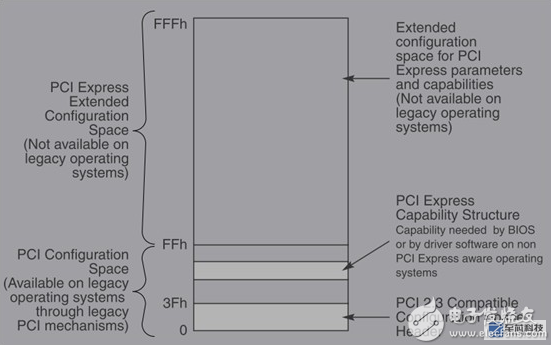

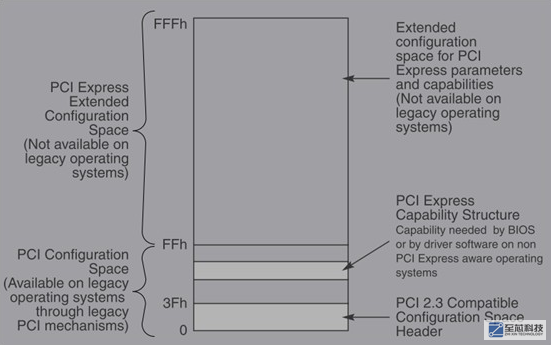

大家好,又到了每日学习的时间了,今天我们来聊一聊PCIe的软件配置方式。 关于PCIe的软件配置和初始化 PCIe设计出来考虑了和pci兼容问题。所以PCIe的软件配置方式可以沿用PCI的配置方式

2019-07-29 09:26:32 7337

7337

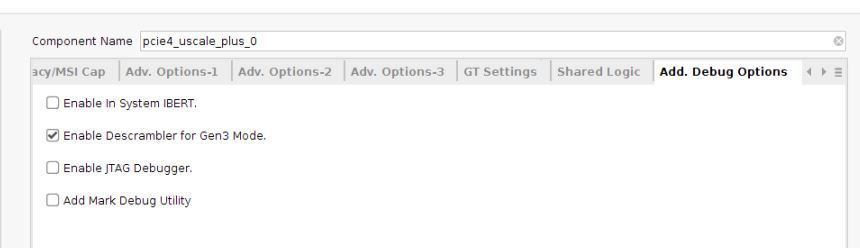

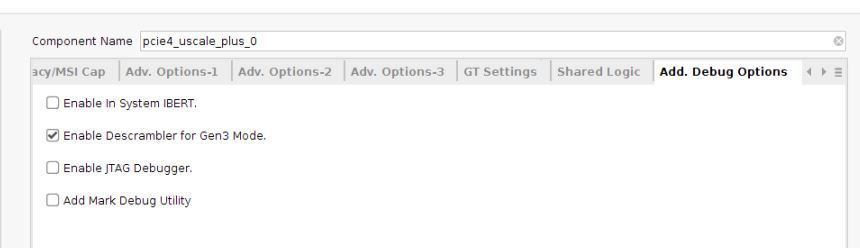

PIPE 接口上的数据在 Gen3 的速度下被加密。当调试 PCIe 问题时,能在 PCIe 链接上查看各个包会很有帮助。 若要实现此目的,用户需拥有协议链接分析器。由于其成本较高,能接触到此等设备

2020-11-29 10:29:00 3572

3572

在Linux系统下,有两种链接文件:一种是硬链接(Hard Link);另一种是软链接,也称为符号链接(Symbolic Link)。

2022-10-21 14:26:57 1139

1139 本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

2023-09-26 11:39:14 5659

5659

6678的pcie和fpga的pcie TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

2018-06-21 15:49:12

有没有研究PCIE的,求指导。{:4_100:}

2013-03-23 23:46:18

小弟学习K1_STK(从官网下的最新的例程keystone软件开发包)里面的PCIE(例程),这个是例程里面RC端和EP端用的是MSI中断。PCIE

2018-06-21 03:49:49

1.PCIE的发送和接收数据本工程的目的是在XC7K325tffg的平台上实现pcie的数据发送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的结构:架构各个模块的作用PCIE部分

2019-12-26 10:46:09

复合体`-- 00:00.00 0x1957 0x4002 桥接设备 0x04 当我连接基于 x4 的 NVMe SSD 卡时,链接没有建立。PCIE0用于连接卡。同一张卡在其他 PC 上工作。失败

2023-03-29 06:13:08

开发环境:windows开发平台:QT5.11.31.PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2019-12-26 10:27:19

开发环境:windows开发平台:QT5.11.31、PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2022-01-13 16:44:54

PCIE-52P90H

2023-03-29 22:43:17

M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

前言PCIE设备并不局限于常见的显卡,很多人存在的误区,其实现在芯片组把硬盘、网卡、声卡、显卡、采集卡之类的都归属于PCIE总线。注意:英特尔快速存储技术中的链接电源管理 (LPM) 是一项节能技术

2021-12-27 07:57:58

我想用C6657的PCIE接口扩展一个WIFI.

C6657的PCIE需要一个LVDS的参考时钟(PCIECLKP, PCIECLKN), WIFI芯片的PCIE需要一个HCSL的参考时钟

2018-06-21 18:45:06

本文档旨在提供关于将PCIe接口集成到基于AMBA的片上系统(SoC)的指导。

假设PCIe接口通过基于AXI或ACE协议的互连连接到SoC的其余部分。

读者应熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

PCIe提供了一种可裁减高速串行I/O点到点的总线连接。PCIe的LAN是一个全双工的通道,由一对接收差分对和一对发送差分对构成。PCIe的带宽可以通过增减LANE数来调整。PCIe规范定义了x1

2019-06-03 07:09:56

一、PCIe基本知识1、PCI-Express(peripheral component interconnect express):是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO

2021-11-11 08:05:11

硬盘是大家都很熟悉的设备,一路走来,从HDD到SSD,从SATA到NVMe,作为NVMeSSD的前端接口,PCIe再次进入我们的视野。作为x86体系关键的一环,PCIe标准历经PCI,PCI-X

2021-05-25 09:22:48

PCIe设备的低功耗状态要求系统驱动程序显式地将设备置于低功耗状态,从而PCIe链路则可以依次变为低功耗链路状态。PCIe规范允许PCIe链路在没有系统驱动的情况下进入低功耗状态。这个特性就是所谓

2021-12-28 06:18:35

pcie虚拟化技术中,一端pcie的虚拟通道又睡指定,是通过软件配置吗

2019-11-11 10:34:47

几个测试,只需用他想要的测试名称更改testname。是不是有人知道“break_loop”测试是否可以作为例子用于通过PCIe链接与主机PC建立AC701的通信?还有其他例子吗?感谢所有提前

2019-09-10 07:56:36

Hi 各位管理好

咨询下,我使用STK 6657 中的 PCIE_test 例程进行PCIE通信测试, 6657作为RC端口, pcie外接设备

在代码中有

2018-06-21 18:49:04

`EC20 Mini PCIe是采用 PCI Express® Mini Card标准接口的LTE模块;采用LTE 3GPP Rel.9技术,支持最大下行速率100Mbps和最大上行速率50Mbps

2018-06-05 17:38:23

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

PCIE BOARD 6 PORT DB-9

2023-03-22 20:41:28

MODULE CONV PCIE-SMA

2023-03-22 20:00:22

33800000.pcie:Phy链接从未出现

我尝试使用其他 PCI Express 卡,以太网卡,但在 PCIe Gen1 中,它工作正常:

[ 1.293479] imx6q-pcie 33800000.pcie

2023-04-28 07:36:10

查过mini pcie的信号引脚定义,有52个信号(大多引脚无用),X1 LANE 的情况,查看飞思卡尔或INTEL处理器的设计资料,关于这个应用除了主要 的差分收、发和差分时钟信号之外还需要额外

2017-11-29 11:50:51

嗨,在ML605设计中,信号“PCIE_250M_MGT1_P / N”从器件“ICS874001”驱动到PCIe MGT参考时钟。根据以下链接中给出的相位噪声值,http

2020-06-08 15:30:33

DEV SYSTEM P4080 PCIE

2023-03-22 19:55:54

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

DEVELOPMENTSYSTEMT4240PCIE

2023-03-22 19:56:26

个固定的较低链接速度和一个(当前未使用的)disable-gpio 引脚: &pcieb{ compatible = "fsl,imx8qxp-pcie

2023-04-03 06:31:15

ZYNQ7045的PCIE电路设计,板卡使用插针式连接器,引出了PCIE信号,未使用金手指。为了插入机箱设计了扩展版,插座与插针对应,带有PCIE金手指。目前遇到的问题是,当板卡连接扩展板使用金手指

2023-05-16 11:07:40

/pci_epc 中没有)。它应该由内核中激活的驱动程序创建(drivers/pci/controller/dwc/pcie-designware-ep.c?)。它是在启动 pcie 链接后创建

2023-06-09 08:23:25

协议:47960 (0xbb58)

PCIe0:pcie@3400000 根复合体:无链接

PCIe1:pcie@3500000 根复合体:无链接

我的问题是:

我是否需要启用任何与 pcie

2023-05-09 12:00:30

:能使用xiinx 的PCIE ip核完成读写功能对以上课程有兴趣的同学点下面链接学习 : 明德扬FPGA课程_PCIE高速接口XILINX.ISE教程_哔哩哔哩_bilibili这只是我们明德扬课程

2022-02-14 09:50:22

,那就很容易把pcie协议理解彻透彻,当然这里狭义指的是上层交互的TLP协议,数据链路层和物理层更复杂的事情是硬核做的,用起来PCIE并不需要深入了解。

如何使用紫光PCIE,首先FPGA端需要一个

2023-11-17 14:35:30

刚接触PCIe,想用PCIe口与PC通信,EP模式。把板子插到PC上之后,通过windriver能查看到TI设备,但是用PCItree不能看到,这样正常吗?我运行的程序

2018-08-07 08:28:19

我们可以将多个 PCIe 设备 (IC) 连接到一般的单个 PCIe 控制器(在我们的案例中更具体地说是 NXP LS20xxA 处理器)吗?

例如,将四个不同的 PCIe x1 设备 (IC

2023-05-05 07:35:41

[tr=transparent]12槽PCIe扩展坞PCIE3-1612扩展系统是12槽位扩展系统,采用PCIe Gen3 Multi-Root Switch,系统支持12个PCIe X8 插槽

2018-07-09 09:24:53

[tr=transparent]12槽PCIe扩展坞PCIE3-1612扩展系统是12槽位扩展系统,采用PCIe Gen3 Multi-Root Switch,系统支持12个PCIe X8 插槽

2018-07-03 09:37:11

嗨,我能够在我们的定制板上连接到virtex 7 fpga。我的块级设计具有用于pcie的轴桥作为终点和axi bram。但我无法使用pcie链接从外部处理器访问bram。任何人都可以帮忙解决这个问题吗?大多数情况下,我猜这与地址翻译有关,我无法弄清楚。谢谢

2020-04-22 09:31:47

我试图从xapp1052识别PCIe BMD示例中的主要数据端口,以便我可以在其中添加我的设计。我试图为PCIe接收数据[63:0] trn_rd添加一些常量值。但是在我给出一个ReadData

2019-03-20 15:09:18

我是一名PCIe新手,想了解以下问题:

1、如何测试PCIe?

2、如何读写PCIe(两块开发板通过PCIe线互连,分别配置为RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

嗨,我想通过pcie链接访问外部处理器的内存。 CDMA如何知道外部处理器的内存?如何在cdma中寻址外部处理器内存?我试过访问内存并得到CDMA解码错误?谢谢

2020-04-22 10:28:03

大家好:我拿到了ML605板。我使用EDK工具创建了一个带MicroBlaze + PCIe + DDR3的AXI4系统,并生成XMP文件。我想设置一个测试平台来模拟PCIe到DDR3的事务。 (即

2019-08-28 09:56:07

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收发器IP提供了一系列完整的PCIe 2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持

2023-04-03 19:47:28

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本应

2023-04-03 19:50:56

M31 PCIe 5.0 PHY IP,用于存储和高带宽连接 M31 PCIe 5.0 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

在用FPGA开始一个PCIe系统设计,你需要了解PCIe规范、核心和链接,终端设备的设计考虑。

2010-12-14 15:06:47 0

0 PCIe 3.0的技术架构上相较于PCIe 2.0有了显著的改进,同时也在制造面、成本、功耗、设计复杂度与兼容性之间进行适当取舍并截取优化的部份。

2011-02-27 22:29:21 1360

1360 PCIE总线基本资料 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具

2012-05-10 14:45:47 0

0 近日,北京泛华恒兴发布了PS PCIe-3811转接板。PS PCIe-3811可实现PXIe总线到PCIe总线的无源转接,支持×4宽度的PCIe链路,适用于PCIe系统。

2013-06-07 11:05:38 7590

7590 PCIe总线规范与总线频率和编码

2016-12-13 21:06:49 8

8 本文档内容介绍了基于SIM7100-PCIE4G模块PCIE封装硬件资料,供参考

2018-03-15 11:26:13 137

137 大家好,又到了每日学习的时间了,今天我们来聊一聊PCIe的软件配置方式。 关于PCIe的软件配置和初始化 PCIe设计出来考虑了和pci兼容问题。所以PCIe

2018-07-27 19:16:08 3355

3355

该信号为全局复位信号,由处理器系统提供(RC),处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。

2018-12-22 14:45:41 22377

22377 Linux链接分两种,一种被称为硬链接(Hard Link),另一种被称为符号链接(Symbolic Link)。默认情况下,ln命令产生硬链接。

2019-04-25 18:00:25 1563

1563 。”

在李正茂看来,第一个C是链接,5G强调的仍然是链接。李正茂指出:“链接是基础,但5G时代的链接是智能化的链接。”

2019-05-23 09:02:58 678

678 静态链接使用静态库进行链接,生成的程序包含程序运行所需要的全部库,可以直接运行,不过静态链接生成的程序体积较大(即使是在静态链接中,整个库文件也并没有全部装入到可执行文件中,所装入的只是需要的函数)。

2020-11-12 15:50:49 2198

2198

美国微芯(Microchip)发布了两款 Retimer 芯片,特点是支持 PCIe 5.0 的 32GT/s 链接速率。两款 XpressConnect 芯片的型号分别为 RTM-C 8xG5

2020-11-12 16:25:54 2219

2219 2021年4月6日 Broadcom最新的PCIe Gen 5 switch芯片内置了SerialTek PCIe抓包分析功能,可以大大方便服务器、存储系统厂商调试PCIe Gen 5在初始化

2021-04-13 15:30:47 4797

4797

/秒(PCIE5.0 X16),增长了480倍。 PCIe 5.0 第5代PCIe技术 PCIe5.0速度是 PCIe 4.0 的两倍,并具有向下兼容性。PCIe 5.0 协议分析仪能够支持 32GT

2021-06-19 11:04:51 33055

33055 最近,看到很多文章都在介绍 Linux 中的文件系统,其中就包括:inode 节点、软链接、硬链接等重要的概念。 于是就有小伙伴私信问我:这些概念我都懂,但是我能利用他们来完成什么工作呢? 或者说

2021-06-21 16:33:43 1471

1471 随着英特尔的十一代酷睿发布,PC硬件已经实现了对PCIe 4.0固态硬盘的全面支持。PCIe 4.0接口的全面普及推动了固态硬盘提速潮,PCIe 4.0逐渐走进了大众的视野,成为购买者选购固态硬盘

2021-09-14 18:09:49 22294

22294 前言PCIE设备并不局限于常见的显卡,很多人存在的误区,其实现在芯片组把硬盘、网卡、声卡、显卡、采集卡之类的都归属于PCIE总线。注意:英特尔快速存储技术中的链接电源管理 (LPM) 是一项节能技术

2022-01-05 14:11:24 7

7 计算机链接 /多站链接模块 产品规格书

2022-08-29 09:57:48 2

2 电子发烧友网站提供《PCIe 9110I PCIe 9210I PCIe 9410I EMC证书.pdf》资料免费下载

2022-10-14 10:05:14 1

1 由于最新PCIe标准必须支持以前各代PCIe标准,所以对验证团队来说,每一代新的PCIe标准的测试矩阵都会呈指数级增长。再加上标准发展导致的测试复杂度增加,这明显提高了实现最新PCIe标准所用的整体测试时间。

2022-11-29 14:08:33 826

826 什么是 Linux 中的符号链接,为什么要使用它? 符号链接 Symbolic Links,也称为 Symlinks 或 soft link,是一种特殊类型的文件,它就像 Windows

2023-02-11 10:12:47 905

905 学习Linux动态链接库是一个绕不开的话题,我们今天就一起来看一下什么是动态链接库、动态链接库有什么好处、如何编译出一个动态链接库等几个关于动态链接库的几个基本概念

2023-02-17 10:49:57 734

734

PCI Express® 6.0 (PCIe® 6.0) 规范由 PCI-SIG® 于 2022 年 1 月发布。最新一代的 PCIe 标准带来了许多激动人心的新功能,旨在提高计算密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序

2023-05-22 17:27:51 4407

4407

PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 506

506

PCIe是一种高速串行计算机扩展总线标准,自2003年推出以来,已经成为服务器(Server)和PC上的重要接口。今天为大家简单介绍一下PCIe的发展历史以及它的工作原理。 一、PCIe的由来

2023-07-04 18:15:03 9791

9791 自2003年推出以来,PCIe发展至今已经从最初的1.0升级到了6.0,在上一篇文章中为大家介绍了PCIe基础知识:《什么是PCIe?》 ,本文则为大家简单介绍一下 PCIe 标准的演进历史以及

2023-07-26 08:05:01 867

867

我们在进行PCIe RTL仿真时,由于PCIe ltssm协商过程比较复杂,导致PCIe ltssm进入L0状态所花费的时间比较长(大概在20~60分钟,因代码复杂度、服务器性能、PCIe速率

2023-08-17 09:42:22 725

725

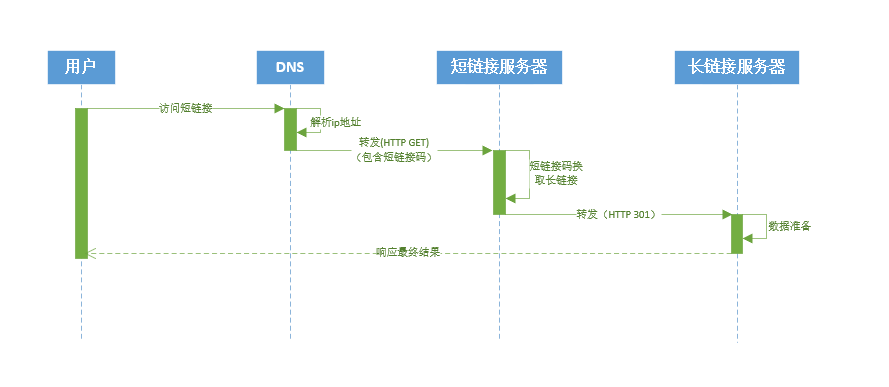

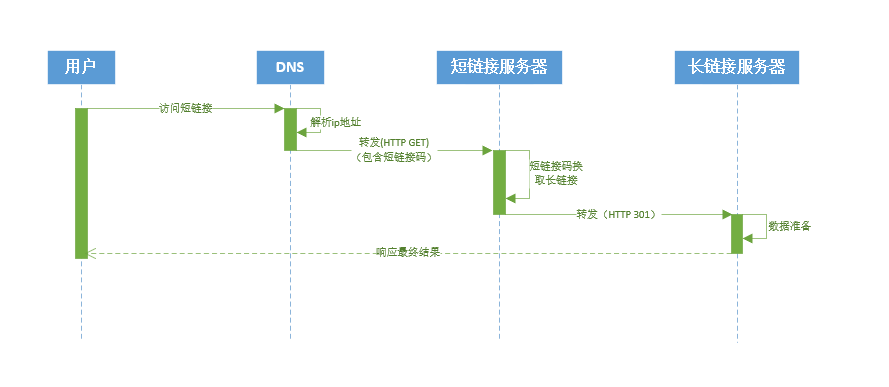

最近在做一套推广系统,将其中涉及的 长短链接问题 在这里分享一下。推广方式主要是以短信方式慰问客户并推送宣传链接(非广告),但链接真的是太长了,先不说短信按字数收费问题,就是看到就想立刻删除。所以

2023-10-08 14:31:52 318

318

硬链接PK软链接

2023-10-12 18:16:49 646

646 随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1300

1300

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503

电子发烧友App

电子发烧友App

评论