NXP公司的LPC2930是集成了ARM968E-S CPU核和两个TCM区块的MCU,工作频率高达125MHz,并具有全速USB 2.0 Host/OTG/Device控制器,CAN和LIN,56 kB SRAM,外接存储器接口,三个10位ADC和多种串行接口,可广泛应用在消费电子,工业和通信市场。本文介绍了LPC2930主要特性和优势,整体方框图和各种功能的方框图,包括时钟区框图,调制和取样控制子系统(MSCSS)方框图,ADC方框图,PWM方框图,PCRSS方框图,CGU0和CGU1方框图,时钟发生架构图和PLL方框图以及自供电USB接口框图与USB OTG端口配置图。

The LPC2930 combine an ARM968E-S CPU core with two integrated TCM blocks operating at frequencies of up to 125 MHz, Full-speed USB 2.0 Host/OTG/Device controller, CAN and LIN, 56 kB SRAM, external memory interface, three 10-bit ADCs, and multiple serial and parallel interfaces in a single chip targeted at consumer, industrial, and communication markets. To optimize system power consumption, the LPC2930 has a very flexible Clock Generation Unit (CGU) that provides dynamic clock gating and scaling.

LPC2930主要特性和优势:

ARM968E-S processor running at frequencies of up to 125 MHz maximum.

Multilayer AHB system bus at 125 MHz with four separate layers.

On-chip memory:

Two Tightly Coupled Memories (TCM), 32 kB Instruction TCM (ITCM), 32 kB Data TCM (DTCM).

Two separate internal Static RAM (SRAM) instances; 32 kB SRAM and 16 kB SRAM.

8 kB ETB SRAM, also usable for code execution and data.

Dual-master, eight-channel GPDMA controller on the AHB multilayer matrix which can be used with the SPI interfaces and the UARTs, as well as for memory-to-memory transfers including the TCM memories.

External Static Memory Controller (SMC) with eight memory banks; up to 32-bit data bus; up to 24-bit address bus.

Serial interfaces:

USB 2.0 full-speed Host/OTG/Device controller with dedicated DMA controller and on-chip device PHY.

Two-channel CAN controller supporting FullCAN and extensive message filtering

Two LIN master controllers with full hardware support for LIN communication. The LIN interface can be configured as UART to provide two additional UART interfaces.

Two 550 UARTs with 16-byte Tx and Rx FIFO depths, DMA support, modem control, and RS-485/EIA-485 (9-bit) support.

Three full-duplex Q-SPIs with four slave-select lines; 16 bits wide; 8 locations deep;Tx FIFO and Rx FIFO.

Two I2C-bus interfaces.

Other peripherals:

One 10-bit ADC with 5.0 V measurement range and eight input channels with conversion times as low as 2.44 μs per channel.

Two 10-bit ADCs, 8-channels each, with 3.3 V measurement range provide an additional 16 analog inputs with conversion times as low as 2.44 μs per channel.Each channel provides a compare function to minimize interrupts.

Multiple trigger-start option for all ADCs: timer, PWM, other ADC, and external signal input.

Four 32-bit timers each containing four capture-and-compare registers linked to I/Os.

Four six-channel PWMs (Pulse-Width Modulators) with capture and trap functionality.

Two dedicated 32-bit timers to schedule and synchronize PWM and ADC.

Quadrature encoder interface that can monitor one external quadrature encoder.

32-bit watchdog with timer change protection, running on safe clock.

Up to 152 general-purpose I/O pins with programmable pull-up, pull-down, or bus keeper.

Vectored Interrupt Controller (VIC) with 16 priority levels.

Up to 22 level-sensitive external interrupt pins, including USB, CAN and LIN wake-up features.

Processor wake-up from power-down via external interrupt pins, CAN, or LIN activity.

Configurable clock-out pin for driving external system clocks.

Flexible Reset Generator Unit (RGU) able to control resets of individual modules.

Flexible Clock-Generation Unit (CGU) able to control clock frequency of individual modules:

On-chip very low-power ring oscillator; fixed frequency of 0.4 MHz; always on to provide a Safe_Clock source for system monitoring.

On-chip crystal oscillator with a recommended operating range from 10 MHz to 25 MHz. PLL input range 10 MHz to 25 MHz.

On-chip PLL allows CPU operation up to a maximum CPU rate of 125 MHz.

Generation of up to 11 base clocks.

Seven fractional dividers.

Second, dedicated CGU with its own PLL generates USB clocks and a configurable clock output.

Highly configurable system Power Management Unit (PMU):

clock control of individual modules.

allows minimization of system operating power consumption in any configuration.

Standard ARM test and debug interface with real-time in-circuit emulator.

Boundary-scan test supported.

ETM/ETB debug functions with 8 kB of dedicated SRAM also accessible for application code and data storage.

Dual power supply:

CPU operating voltage: 1.8 V ± 5 %.

I/O operating voltage: 2.7 V to 3.6 V; inputs tolerant up to 5.5 V.

208-pin LQFP package.

−40℃pplication to +85℃ ambient operating temperature range.

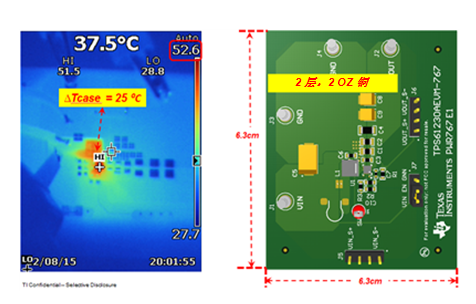

图1。LPC2930方框图

图2。LPC2930时钟区框图

图3。LPC2930调制和取样控制子系统(MSCSS)方框图

图4。LPC2930 ADC方框图

图5。LPC2930 PWM方框图

图6。LPC2930 PCRSS方框图

图7。LPC2930 CGU0方框图

图8。LPC2930时钟发生架构图

图9。LPC2930 PLL方框图

图10。LPC2930 CGU1方框图

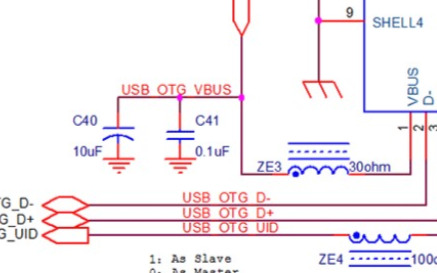

图11。LPC2930 自供电USB接口框图

图12。LPC2930 总线供电USB接口框图

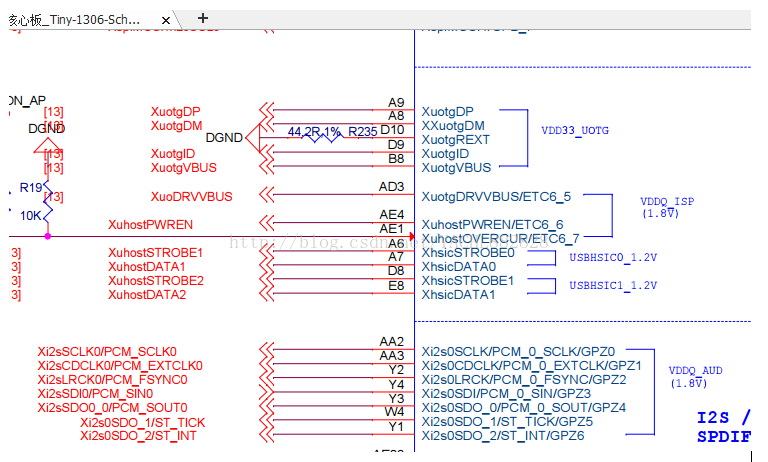

图13。LPC2930 USB端口配置图:USB端口1 OTG双规设备,USB端口2主机

图13。LPC2930 USB OTG端口配置图:USB端口1 主机,USB端口2主机

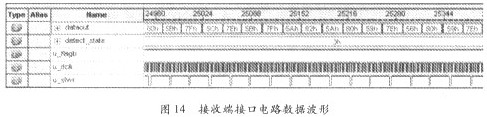

图14。LPC2930 USB OTG端口配置图:USB端口2 设备,USB端口1主机

基于LPC2930设计的高速USB-OTG接口方案

- US(46135)

- LPC2930(6687)

相关推荐

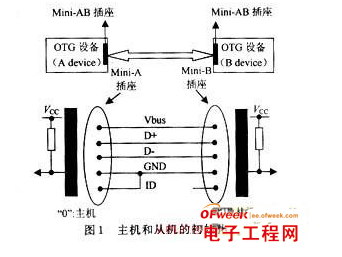

USB OTG Vbus电源框图及应用方案

到智能手机以及从相机到打印机之间的数据传输需求也随之增加。 USB On-the-Go(OTG)是使设备能够充当主设备或从设备的规范。USB OTG可广泛应用于PC、智能手机、ePOS(电子销售点)和移动电源。主设备或从设备的角色可以根据协议进行改变。数据可

2018-03-09 09:21:13 17788

17788

17788

17788

基于TF32A09系列芯片的高速数据流加密的解决方案

高速数据流加密转接器具有2个USB 2.0高速(480Mb/s)接口(OTG)和内置高速加密算法(如SM1)。其中USB_Host接口和传统的移动存储设备相接、USB_Device接口和PC机相接

2019-01-04 08:14:00 5715

5715

5715

5715

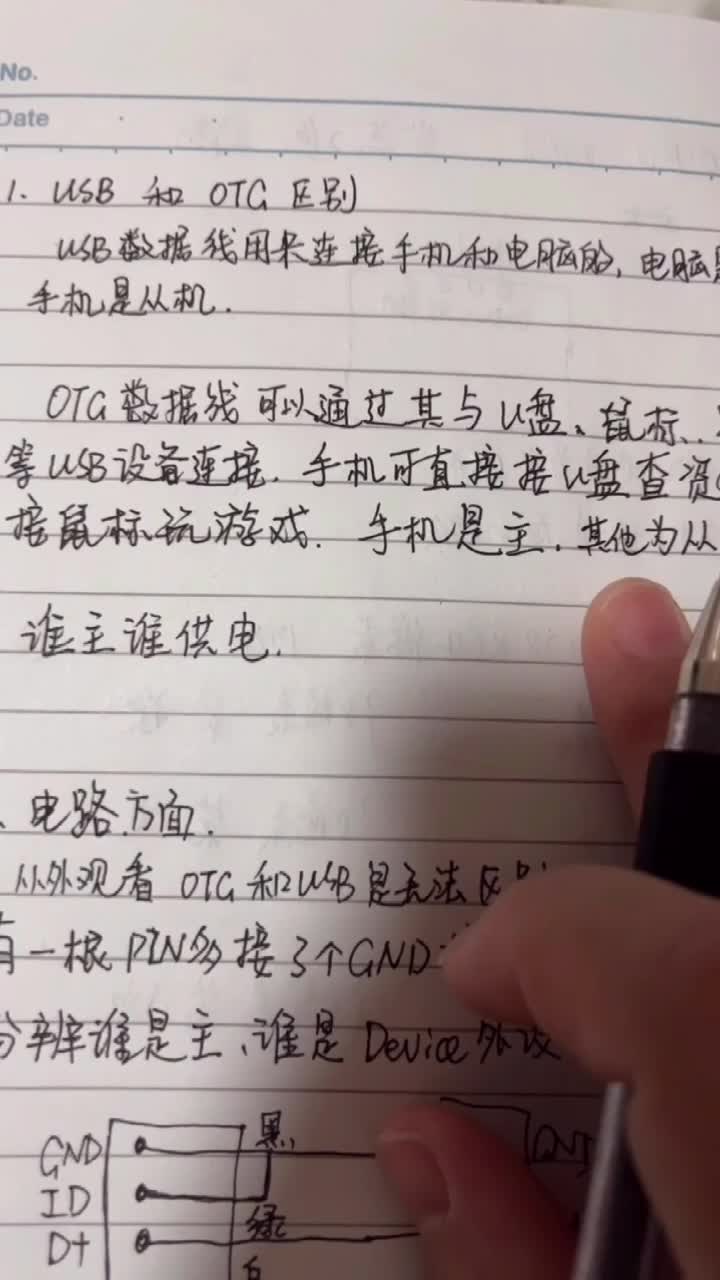

OTG硬件检测电路

1. OTG接口与转换器 OTG是"On The Go"的英文缩写,字面上可以理解为“安上即可用”。USB传输是主从结构,一切USB传输都有Host发起。比如在开发板上可以插入

2023-07-11 08:40:46 868

868

868

868

LPC2930

LPC2930 - ARM9 flashless microcontroller with CAN, LIN, and USB - NXP Semiconductors

2022-11-04 17:22:44

LPC2930FBD208

LPC2930FBD208 - ARM9 flashless microcontroller with CAN, LIN, and USB - NXP Semiconductors

2022-11-04 17:22:44

USB-OTG是否需要连接Vbussx才能用作USB大容量存储器呢?

了评估板与我的定制板的 shematc 比较。此外,USB-ORG 作为 DFU 设备在工程模式下工作——所以我猜焊接和 USB 引出线是正确的。图1。USB-OTG2.Pic的自定义电路板原理图。USB-OTG 的评估板原理图。

2022-12-14 07:56:39

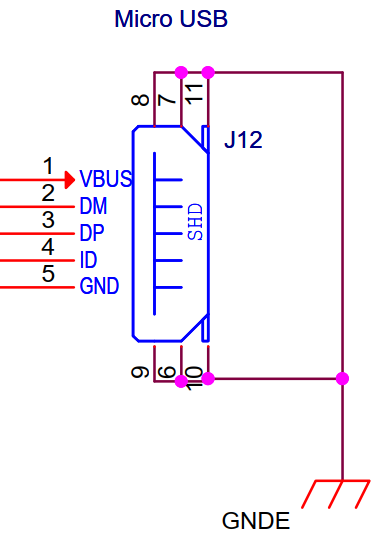

USB OTG原理+ ID 检测原理

。也就是说,手机既可以做外设,又可以做主机来传送数据,可用电缆的连接方式来决定初始角色(由ID线的状态来决定)。USB OTG接口中有5条线: 2条用来传送数据(D+ 、D-);1条是电源线(VBUS

2015-02-10 11:19:47

USB接口易损坏的解决方案

该问题由某客户提出,发生在 STM32F205VCT6 器件上。据其工程师讲述:为了实现产品的设计中使用STM32 的 USB OTG 接口,作为其产品的一个通用 USB 接口来用。在其产品小批量试产后,发现STM32的 USB OTG 接口在其产品的使用过程中易损坏。

2023-09-08 06:13:11

USB接口的 MP3/WMA播放方案OTG13T

USB接口的 MP3/WMA播放方案OTG13T 板载USB接口,支持所有市售

2010-03-12 11:20:28

USB高速物理层不工作怎么解决?

数据。如果禁用 OTG 的内部 DMA,全速 USB 设备工作正常,但高速设备无法在枚举时传输设置命令。如果启用 OTG 的内部 DMA,则所有全速和高速设备都无法枚举。有没有成功案例?

2023-01-05 08:43:05

BeagleBone Black USB一线通(3)

20来寸的显示器上,还是有些不协调。索性我们使用图形界面远程登陆,实现BB-Black的图形显示。这样的话,仍然是使用那条连接到USB-OTG上面的多接口USB线缆,就可以实现一线通的目的。功能完备又

2014-10-22 17:05:17

NXP LPC2939 MCU USB接口方案

,768kB闪存以及外接存储器接口,三个10位ADC,多个串行和并行接口.主要用在消费类电子,工业,医疗和通信市场.本文介绍了LPC2939主要特性, 方框图,以及各种USB,USB OTG接口方框图

2018-11-20 11:06:06

使用USB-OTG下载程序失败后如何刷机才能解决呢

使用USB-OTG下载程序失败后,主板不能被识别到了。笔记本设备管理器中的imx6ul设备也是在不断的连接与掉线中,无法维持。如何刷机才能解决?

2022-01-10 07:00:34

使用USB通信如何将USB驱动程序与lpc 54018控制器接口连接?

使用 USB 通信 如何将 USB 驱动程序与 lpc 54018 控制器接口?请发送以下步骤....

2023-04-17 06:51:20

双网口如何分配OTG相关管脚?

由单网口改为双网口后,USB-OTG的ID管脚、USB_DET_BUS、USB_DRV_BUS管脚被占用,从之前的fex看到u***_det_vbus_gpio=port:PH17u

2022-01-05 07:04:12

可以在同一个设备中使用USB-OTG和USART1吗?

整个 DTS 中的任何设备树文件都没有引用此 pin。但是,如果我禁用 usb-otg 设备,USART1 就会开始工作。但我不想那样做。因此,在阅读了 usb-otg 驱动程序文档后,我发现了以下

2022-12-29 09:15:33

基于USB接口的OTG应用技术开发

disconnected", minor);}结束语本文是在基于ARM9开发板linux操作系统下实现USB接口的OTG应用技术,实现了双角色设备的开发。随着OTG技术的发展,USB的应用将会更为广泛,并且移动设备间的直接数据传输成为可能。

2018-12-05 10:36:11

基于TUSB6020的USB OTG接口设计

,TI公司推出的高速USB2.0 OTG双功能控制器TUSB6020,是一种小型解决方案,既能作为针对USB外设的功能控制器使用,又能作为点对点或点对多点通信中的主机/外设工作。本文在此基础上研究

2018-11-22 11:23:28

如何去调试U-Boot和TF-A中的USB以及OTG控制器呢

”参数的情况下工作。但是,在 U-Boot 中使用 OHCI 驱动程序时,可以很好地访问 USB 驱动器。另一个可能与此相关的问题是带有 USB-OTG 的 DFU 在设备上无法正常工作。ROM 代码

2022-12-20 07:00:28

如何处理LPC5514 USB高速设备勘误问题?

引用“usb_device_cdc_vcom”来测试从 Windows 窗体应用程序接收文件。我有一个关于如何处理勘误表的问题。3.4 USB.3:“对于USB高速设备控制器,连接某些全速集线器

2023-03-29 08:07:51

如何将sbsfu工程中的uart接口换成usb otg接口?

引脚的 usart6。可能的解决方案 (?) : 1)将sbsfu工程中的uart接口换成usb otg接口; 2) 将USB DM 和DP 引脚直接连接到可用的usart/uart 接口之一

2022-12-29 11:38:00

恩智浦NXP LPC3000系列ARM9

重AHB总线-指令和数据、DMA、USBUSB接口-LPC3200:12M全速,LPC3100:480M高速-支持Device、Host和OTG功能-支持DMA传输

2013-02-20 11:30:52

英特尔航空相机只有一个USB-OTG连接

嗨,我想将几台摄像机连接到英特尔航空板,但它只有一个USB-OTG连接。我想知道是否有任何方法可以使这些连接可视化几个图像。谢谢。以上来自于谷歌翻译以下为原文Hi,I would like

2018-11-06 11:12:23

请教双网口如何分配OTG相关管脚

由单网口改为双网口后,USB-OTG的ID管脚、USB_DET_BUS、USB_DRV_BUS管脚被占用,从之前的fex看到u***_det_vbus_gpio=port:PH17u

2022-01-13 07:24:39

基于ARM处理器LPC2142的高速数据采集卡设计

提出了一种基于LPC2142且具有USB (通用串行总线) 接口的高速数据采集卡的设计方案,给出了基于ARM7处理器LPC2142和FPGA芯片的软硬件设计方法,该设计方案解决了高速实时信号与

2009-03-07 10:05:07 9

9

9

9USB OTG技术在数据采集系统的应用

本文介绍了USB OTG 技术在数据采集系统中的设计与实现,重点阐述了USB OTG 的工作原理、USB 主从机的硬件切换设计和固件程序设计。USB OTG(On The Go)能够实现设备间真正的点对

2009-08-11 10:16:56 47

47

47

47基于LPC2290嵌入式系统USB接口的设计

基于LPC2290嵌入式系统USB接口的设计:为嵌入式系统设计并实现了USB主机接口。硬件设计采用LPC2290为主控平台, ISP1160为USB主控制器;软件设计借助于ZLG/FS文件系统,完成了USB主机控制器驱

2009-12-31 17:07:46 30

30

30

30基于TUSB6020的USB OTG接口设计

首先介绍了TUSB6020的功能特性及内部结构,阐述了TUSB6020的工作原理,分析了TUSB6020与外部主机的连接方式,提出了一种TMS320DM6437与TUSB6020的USB OTG接口设计方案,其中包括硬件设计

2010-01-20 15:40:07 28

28

28

28基于LPC2148和MCP2510的高速USB-CAN卡

本文介绍了基于LPC2148和MCP2510的USB-CAN接口卡。LPC2148是基于ARM7TDMI-S核的微控制器,处理器速度高,内置USB2.0全速控制器和SPI接口。MCP2510是独立的CAN控制器, 支持V2.0A/B技术规范,通过SPI接

2010-02-25 11:47:17 35

35

35

35LPC3130 LPC3131微控制器用户手册

NXP LPC3130/3131以180MHz ARM926EJ-S CPU为内核,在一个芯片中集成了高速USB2.0 OTG、高达192KB SRAM、NAND Flash控制器、灵活的外部总线接口、4通道10位A/D和许多串行、并行接口,定位于消费应用

2010-03-12 15:50:32 24

24

24

24USB OTG扩展子板的实现

介绍了采用ISP1362控制芯片制作的一块扩展子板,该板为美国模拟器件公司的ADSP-BF533 EZKIT-Lite 评估板提供了USB OTG支持,并在BlackFin 16位DSP上通过USB OTG接口实现了与PC机以及U盘的数据

2010-07-06 16:12:25 53

53

53

53USB OTG晶片设计

USB系统简介 USB OTG传输协议 USB OTG芯片设计 USB OTG 芯片实作 USB的优点在于低廉易建置,缺点USB采用主从式架构(Master/slave system),所有外围装置都要靠单一主控端 (PC)。

2010-07-18 11:39:44 49

49

49

49MAX3301E型USB OTG电路原理及应用

在介绍USB OTG的基础上,着重介绍Maxim公司的MAX3301E型USB OTG电路的特点、内部结构和工作原理。

2010-12-03 16:52:52 0

0

0

0TDI的USB OTG控制器获得USB-IF高速认证

嵌入式USB互连解决方案供应商TransDimension(简称TDI)公司近日宣布,其TD1120单芯片USB OTG高速从端和全速主端控制器成功完成USB Implementers Forum (USB-IF)的高速

2006-03-13 13:05:27 542

542

542

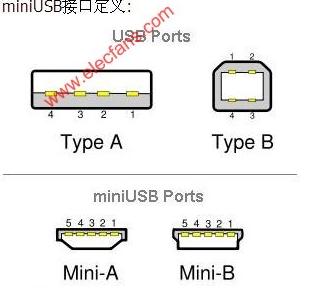

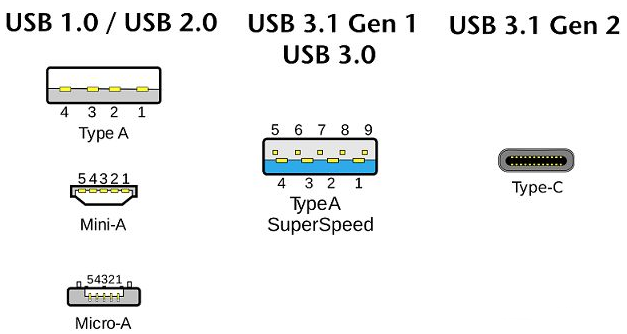

542mini usb 接口定义 5针usb接口定义图

mini usb的接口定义如下:1:VCC2:D-3:D+4:id5:GND其中id脚在otg功能中才使用。由于mini usb接口分mini-A、B和AB接口。如果你的系统仅仅是用做slave,那么就使用B

2008-04-27 17:50:51 68650

68650

68650

68650

IR-UWB通信系统高速USB接口的设计与实现

IR-UWB通信系统高速USB接口的设计与实现

摘要: 采用高速USB接口连接计算机终端与UWB通信系统基带模块,设计并实现了USB接口电路,控制UWB通信系统基带模块与USB接口设

2010-03-13 11:32:33 1984

1984

1984

1984

基于LPC2939设计的MCU USB接口技术

基于LPC2939设计的MCU USB接口技术

LPC2939是NXP公司的集成了两个TCM 的ARM968E-S CPU 核的MCU,工作频率高达125MHz,并集成了全速USB 2.0主/OTG/设备控制器,CAN和LIN,5

2010-04-22 17:54:20 2007

2007

2007

2007

基于LPC1311设计的Cortex-M3 CPU USB接

基于LPC1311设计的Cortex-M3 CPU USB接口方案

NXP LPC1311/13/42/43 是基于Cortex-M3 的微控制器,具有高度集成和低功耗,可用于嵌入式应用。CPU工作频率高达72MH

2010-05-11 17:57:27 1974

1974

1974

1974

USB OTG收发器ISP1301

ISP1301是通用串行总线USB OTG(On-The-Go)收发器,完全兼容通用串行总线规范Rev.2.0和OTG补充规范Rev.1.0a。ISP130

2010-07-19 14:57:34 1437

1437

1437

1437USB OTG连结多种行动装置介绍

本文简述USB规格附录的各种功能,叙述此一技术当前的发展状况,并以Cypress EZ-OTG控制器为例,进一步来说明USB OTG实际能。

2011-05-22 11:55:15 2196

2196

2196

2196ISP1362 USB OTG 控制芯片及应用

ISP1362 是飞利浦公司推出的OTG 解决方案系列中产品,它在单芯片上集成了一个OTG 控制器、一个高级主控制器(PSHC)和一个基于飞利浦ISP1181 的外设控制器。ISP1362 的OTG 控制器完全兼容USB

2011-06-23 16:13:13 120

120

120

120飞兆推具全面USB-OTG支持FAN5401x锂电池开关式充电器

全球领先的高性能功率和便携产品供应商飞兆半导体公司 (Fairchild Semiconductor)与客户共同工作,开发出具有全面USB On-The-Go (USB-OTG)支持的FAN5401x 系列USB兼容锂离子电池开关式充电器产品。

2011-11-03 09:31:26 1088

1088

1088

1088USB_OTG_IP核中AMBA接口的设计与FPGA实现

作为一种简单易用和高速的串行总线,USB(通用串行总线)从出现至今,越来越受到人们的欢迎。而随着OTG(On The Go)技术的推出,更加拓展了USB的应用领域。USB OTG设备具备双重角色的功能

2012-05-22 11:15:56 81

81

81

81USB_OTG扩展子板的实现

介绍了采用ISPl362控制芯片制作的一块扩展子板,该板为美国模拟器件公司的ADSP— BF533 EZKIT—Ute评估板提供了UsB OTG支持,并在BlackFin 16位DSP上通过USB OTG接口实现 了与PC机以及U盘的数据通信。

2016-03-01 10:10:58 4

4

4

4USB OTG IP的适用范围及库的使用

STM32F105、STM32F107、STM32F2、STM32F4 HS OTG IP 可作为高速、全速和低速USB主机 USB OTG 可作为高速和全速USB设备 FSFSHS 存在于STM32F2

2017-09-15 10:35:40 3

3

3

3关于LPC2930的简介及设计信息

1. General desc<x>ription The LPC2930 combine an ARM968E-S CPU core with two integrated TCM

2017-09-15 11:44:32 3

3

3

3AVR单片机的ISP1362OTG设计方案分析

行业的应用,也不适用于野外作业,而OTG技术的推出则可实现在没有PC的情况下,设备与设备之间的数据传输,它拓展了USB技术的应用范围。本文采用的设计方案是基于Philips公司的ISP1362 OTG控制芯片,参照最新的USB OTG技术规范,设计了一种遵

2017-10-20 15:23:30 0

0

0

0基于DSP的USB接口设计方案简析

摘要:介绍了一种基于DSP的USB 接口设计方案,分别从接口的硬件设计、接口操作原理、软件设计流程以及中断服务程序设计要点等方面进行阐述,并利用Cypress 公司提供的USB2.0 接口芯片

2017-10-21 09:32:07 3

3

3

3typec接口的otg线自制教程分享

本文介绍了TYPEC的来源对typec接口的引脚进行了说明,阐述了typec接口工作主从机的连接,最后介绍了typec接口的otg线自制教程。

2018-03-09 10:35:31 234004

234004

234004

234004

USB-OTG插槽类型和连接方式

OTG设备使用插头中的ID引脚来区分A/B Device,ID接地被称作为A-Device,充当USB Host,A-Device始终为总线 提供电力,ID悬空被称作为B-Device,充当USB

2018-05-11 12:29:00 12197

12197

12197

12197USB 2.0高速现成双角色控制器

TUSB6020是一个USB 2高速,上的GO(OTG)双角色控制器设计的无缝接口到VLYNQ串行接口,并适用于广泛的应用。

2018-05-09 16:54:20 13

13

13

13OTG接口设备主从功能实现 OTG检测原理概述

USB OTG标准在完全兼容USB2.0标准的基础上,增添了电源管理(节省功耗)功能,它允许设备既可作为主机,也可作为外设操作(两用OTG)。

2018-05-11 16:12:00 10346

10346

10346

10346

USB OTG的工作原理解析

OTG补充规范对USB 2.0的最重要的扩展是其更具节能性的电源管理和允许设备以主机和外设两种形式工作。OTG有两种设备类型:两用OTG设备(Dualrole device)和外设式OTG设备

2019-07-19 15:58:02 15429

15429

15429

15429

英创信息技术EM9170的USB-OTG接口注意事项

的主要原因是:USB-OTG接口与PCB接通时,由于物理连接器及其它原因,偶尔会在USB_VBUS及GND信号上产生一个浪涌脉冲。正是由于这样一个浪涌脉冲的存在,可能使CPU内部的一部份功能电路损坏。为了消除USB连接时的浪涌脉冲对系统的影响,需要在USB连接器及系统

2020-01-15 15:26:12 897

897

897

897

英创信息技术EM335x工控主板USB OTG接口ESD保护介绍

EM335x工控主板预装正版WEC7操作系统,通过USB OTG接口与计算机连接后,可方便实现在线调试应用程序、文件传输、虚拟串口、远程桌面等功能,USB接口支持热插拔特性,因此必须对其加以ESD

2020-02-03 09:06:42 2370

2370

2370

2370

Silicon Power宣布推出三款USB OTG U盘

据外媒消息,Silicon Power日前宣布推出三款USB OTG U盘,可使用户更方便地携带数据。

2021-01-05 10:47:42 1673

1673

1673

1673EE-288:适用于ADSP-BF533 Blackfin®处理器的USB OTG接口

EE-288:适用于ADSP-BF533 Blackfin®处理器的USB OTG接口

2021-04-13 16:54:44 2

2

2

2适用于ADSP-BF533 Blackfin®处理器的EE-288 USB OTG接口

适用于ADSP-BF533 Blackfin®处理器的EE-288 USB OTG接口

2021-06-18 08:38:10 2

2

2

2STM32F4中USB与PC双向通信

STM32F4系列处理器内部集成了USB-OTG控制器,在不要外部USB IC下就可以实现USB通信,最近两天看了下如何利用STM32的USB实现通信,记录下关键步骤:1. 从http

2021-12-27 19:04:37 33

33

33

33如何确认USB接口是不是“真”高速

USB标准组织把USB 3.0/3.1改名为USB 3.1 Gen 1/Gen 2,代表它们的传输速率。而USB接口样式,则用Type-A、Type-B、Type-C进行区分。像USB 3.0就是使用USB Type-A接口样式、USB 3.1 Gen 1标准的高速接口。

2022-06-30 15:03:54 3829

3829

3829

3829

USB接口EMC注意事项及电路设计

PCB Layout、USB问题问答(设备插入与识别)、USB接口EMC注意事项(接地设计、连接器设计、线缆设计、电缆设计、走线设计、USB OTG)。

2023-05-08 09:51:32 1531

1531

1531

1531

OTG接口与转换器

OTG 接口与转换器 OTG 是“On The Go”的英文缩写,可以理解为“安上即可用”。USB 传输是主从结构,一切 USB 传输都由 Host 发起。 在开发板上可以插入 U 盘,这时开发板

2023-07-17 11:04:38 1085

1085

1085

1085

新品登场!雅特力发布AT32F402与AT32F405高速USB2.0 OTG MCU

因应高速USB市场需求,产品技术不断推陈出新,USB2.0发展带来的高速连接能力,优化消费者的产品使用体验,且由于支持即插即用和热插拔,提高设备易用性,USB接口在各项设备中成为主流通用接口

2023-09-05 13:34:49 459

459

459

459OTG功能使用方法

OTG功能使用方法 什么是OTG功能? OTG(On-The-Go)即为“即插即用”的高速USB接口,在目前的市场上企业和普通消费者极度青睐,其在人们的生活中的应用场景非常广泛,比如U盘、键盘

2023-10-30 09:57:18 1710

1710

1710

1710什么是USB HOST、USB Slave和USB OTG?它们之间有什么区别?

什么是USB HOST、USB Slave和USB OTG?它们之间有什么区别? USB(通用串行总线)是一种用于连接设备的通信接口标准,它允许设备之间进行数据传输和通信。USB HOST、USB

2024-02-02 15:32:57 1235

1235

1235

1235 电子发烧友App

电子发烧友App

评论