1. 背景 这篇文章主要介绍了DDR3IP核的写实现。 2. 写命令和数据总线介绍 DDR3 SDRAM控制器IP核主要预留了两组总线,一组可以直接绑定到DDR3 SDRAM芯片端口,一组是留给

2020-12-31 11:17:02 5068

5068

检测、各种工程机械倾角测量等行业中的推广和应用,要求倾角传感器采集到的大量数据能够在各种恶劣的工业控制环境和现场中得到有效的、完整的保存。海量数据存储器的使用解决了我们对大容量采集数据的存储;内置

2012-11-20 14:00:52

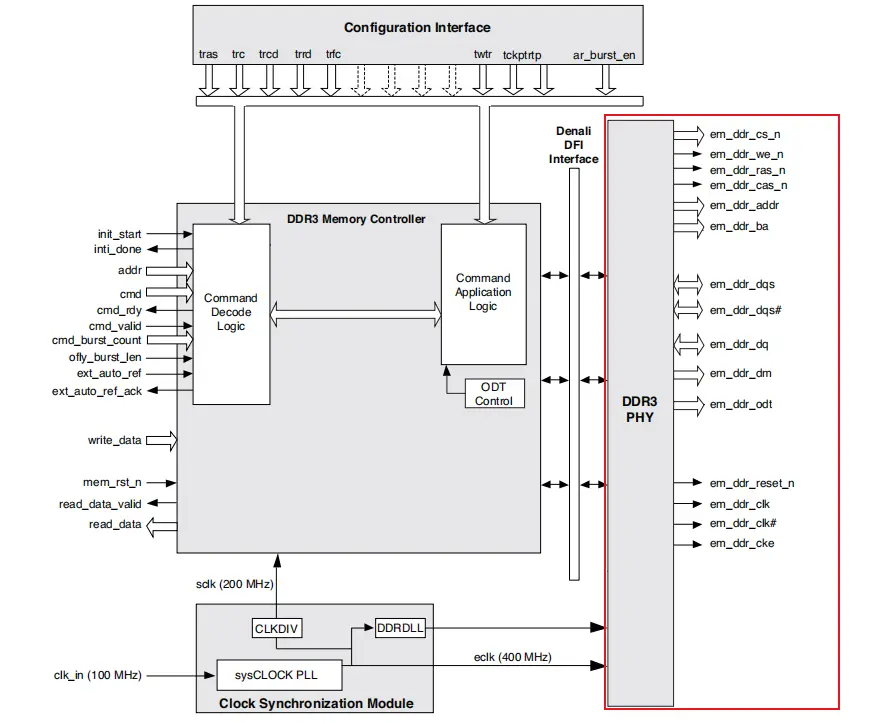

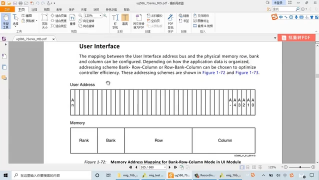

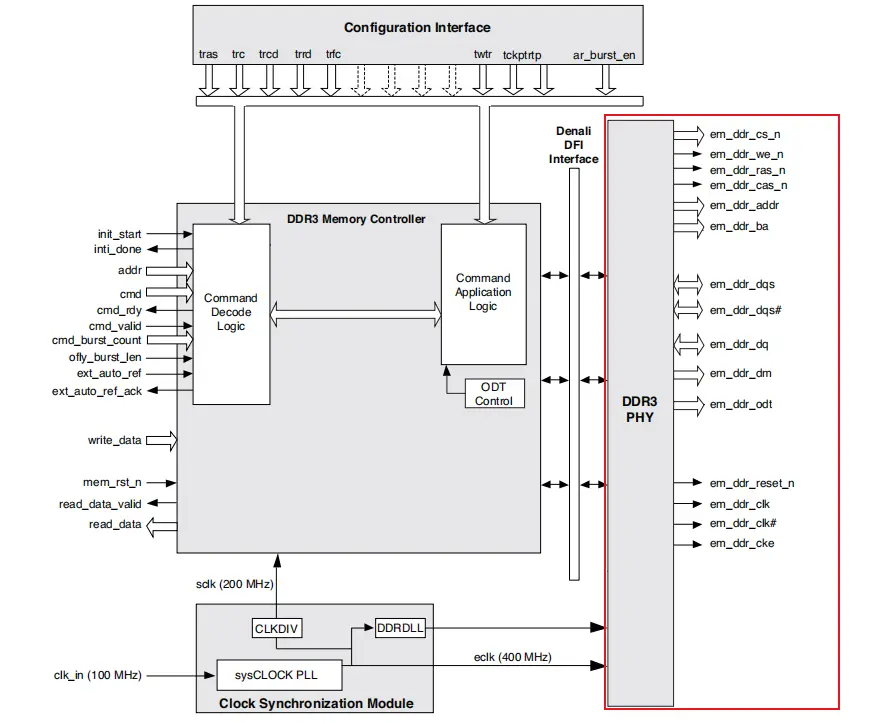

的SDRAMs其结果如图6所说,63位,N=3。图6 地址映射例子2.5. DDR3内存控制器接口为了使得数据能够有效的将数据源从DSP搬运外部DDR3 SDRAM中,DDR3内存控制器使用了一个命令

2018-01-18 22:04:33

使用microblaze处理器。我必须通过DDR3内存发送一些固定值,如8位数据(X'FF'),即我将该数据写入Genesys2 DDR3内存并从内存中读出数据。我已经通过Xilinx网络设备视频手册

2019-05-05 15:29:38

。为了充分利用和发挥DDR3存储器的优点,使用一个高效且易于使用的DDR3存储器接口控制器是非常重要的。视屏处理应用就是一个很好的示例,说明了DDR3存储器系统的主要需求以及在类似数据流处理系统中

2019-05-24 05:00:34

DDR3存储器接口控制器是什么?有什么优势?

2021-04-30 06:57:16

你好,我使用Virtex7的HP库来实现DDR3控制器。我的控制器将以1600Mbps的速度运行,因此主控制器中的VRN和VRP应连接一个80Ω电阻,以实现更高的性能。实现addr / cmd信号

2019-03-25 11:04:50

和安全性大大提高。 2 DDR3介绍 DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比 DR2有更高

2014-12-15 14:17:46

本贴资料整理于《例说FPGA 可直接用于工程项目的第一手经验》1.1功能概述:对FPGA提供的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次写入和读出操作。先从0地址开始遍历写256

2017-02-15 20:31:49

的DDR3内存控制器或内存控制器生成的设计生成的设计,我得到此错误“启动状态结束:低。在我的设计或PCIe中只有PCIe内核的其他比特流示例设计已成功配置。分享我的一些观察, - 配置过程中电压似乎稳定

2020-06-09 15:48:02

配给一个内核以简化软件任务分区• DDR 子系统 (DDRSS)– 支持 LPDDR4、DDR4 存储器类型– 具有内联 ECC 的 16 位数据总线– 支持高达 1600MT/s 的速度片上系统

2023-04-14 15:42:08

核心,以WinCE为软件平台,能实时、连续地采集清晰的视频数据。1 系统结构框图及视频数据采集原理视频数据采集系统结构如图1所示。从图1中可以看出。系统由嵌入式微处理器S3C2440、存储器(包括

2019-08-06 08:30:15

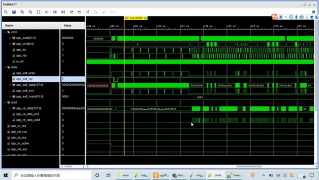

因为工作的需要,最近做了下DDR3 IP核的读写仿真,仿真过程中DDR写数据正常,但在对DDR读取数据时出现以下的情况:1.MEM_DQ、MEM_DQS、MEM_DQSN始终为高阻态

2019-12-26 23:11:56

® ALTMEMPHY宏功能来构建所有的 DDR2或者 DDR SDRAM外部存储器。通过将 Altera DDR2 或者 DDR SDRAM 存储控制器、第三方控制器或者定制控制器用于特定的应用需要,可以实现控制器功能

2017-11-14 10:12:11

DMA控制器在DSP数据采集系统中的应用 DMA 控制器可以无需CPU 介入而在内部存储器、外部存储器和芯片外设之间传送数据,其在DSP 系统中有广泛的应用价值。基于以DSP 芯片

2009-04-28 10:47:02

(flight-time skew)来降低共同切换噪声(SSN)。走线摆率可以达到0.8tCK,这个宽度导致无法确定在哪两个时钟周期获取数据,因此,JEDEC为DDR3定义了校准功能,它可以使控制器

2019-04-22 07:00:08

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面写FPGA的BANK1,3连接外部存储控制器(如下图,且只有四个BANK),所以要将DDR3连接在BANK3上。所以DDR3如何与FPGA芯片

2021-11-29 16:10:48

传输给AT91RM9200;在AT91RM9200上,Lnux驱动实现存储器映射I/O和物理内存重映射,避免了视频数据在应用程序与内核之间的二次拷贝,提高了应用程序的网络发包效率。 1 HPI接口硬件

2018-11-26 11:12:49

的等待时间。 共享存储器效率 —— 为进一步提高共享存储器的执行效率,在 CorePac 内置了扩展存储器控制器 (XMC)。对共享内部存储器 (SL2/SL3) 和外部存储器 (DDR3 SRAM

2011-08-13 15:45:42

控制器通常包括CPU、存储器、输入输出接口、定时器、ADC、DAC等模块,能够实现各种控制、计算、数据处理等功能。 相对于传统的计算机系统而言,MCU控制器具有体积小、功耗低、性价比高等优点,因此在

2023-05-05 14:59:21

TC364 微控制器是否支持外部存储器?

根据我的阅读,外部总线接口用于外部存储器。 在该微控制器的数据手册中,我看到外部总线为 0。

2024-03-04 06:13:37

6655时钟PLL配置与DDR3的配置1 时钟概述PLL与PLL控制器的逻辑组成和处理流程如图1所示。PLL控制器能够通过PLLDIV1到PLLDIV16这些分频器灵活便利的配置和修改内部的时钟信号

2018-01-24 21:27:10

管理,具有高带宽、高性能特性,适合于嵌入式处理器与高性能外围设备、片内存储器及接口功能单元的连接。 根据两种总线的特点和广泛支持,为了给嵌入式SoC系统提供USB接口,需要设计USB和AHB间的桥接IP核

2019-05-13 07:00:04

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

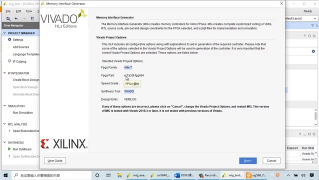

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制和读写时序的情况下,也能通过MIG IP控制器读写DDR存储器。一、新建工程在Vivado环境

2019-12-19 14:36:01

RASn,CASn等,是IP核自动产生的么?要如何配置条件,给DDR3写入数据并读取DDR3的数据,谢谢,现在头绪不清,第一次做,拜托各位解惑了

2016-01-14 18:15:19

请教各位大神,小弟刚学FPGA,现在在用spartan-3E的板子,想用上面的DDR SDRAM进行简单的读写,用MIG生成DDR核之后出现了很多引脚,看了一些资料也不是很清楚,不知道怎么使用生成的这个IP核控制器来进行读写,希望大神们稍作指点

2013-06-20 20:43:56

本视频是Combat FPGA开发板的配套视频课程,本章节课程主要介绍Gowin中DDR3 的基础知识、DDR3的IP core的特性和使用以及DDR3的IPcore例程的仿真。课程资料包含DDR3

2021-05-06 15:34:33

后点击“OK”:四、配置IP核在配置界面,“Memory Protocol”选择“DDR3”;在“General”页面“Clocks”“Memory clock frequency”配置DDR的速率为

2019-12-19 10:16:43

& 14用于DDR3内存接口,但由于我使用的是3.3V的fash存储器IC,我必须使用bank 14进行闪存存储器接口。原因是需要的资源仅在Bank 14中可用.DDR3存储器连接的bank应该工作在

2020-04-17 07:54:29

。具有短的线迹长度、最多两个 DDR3 器件和平衡的 T 拓扑是必须满足的要求;否则,应遵循 VTT 终端指南。特性在具有集成式 DDR 控制器的 Sitara AM437x 处理器上采用系统优化

2015-04-03 17:14:40

。具有短的线迹长度、最多两个 DDR3 器件和平衡的 T 拓扑是必须满足的要求;否则,应遵循 VTT 终端指南。主要特色在具有集成式 DDR 控制器的 Sitara AM437x 处理器上采用系统优化

2018-09-26 08:53:27

FPGA外部的DDR2芯片,它与DDR2 IP核的接口通常命名为“mem_*”。● DDR2 IP核内部分两个部分,即图示的“ALTMEMPHY”和“存储控制器(Memory Controller

2016-10-27 16:36:58

关于DDR3的时序(Altera的外部存储器接口手册)1. 关于突发地址的对齐(Burst-Aligned Address),是指突发时加载的地址,与突发长度之间,正好符合对齐关系。即当前地址

2018-03-16 10:46:27

。为了充分利用和发挥DDR3存储器的优点,使用一个高效且易于使用的DDR3存储器接口控制器是非常重要的。视屏处理应用就是一个很好的示例,说明了DDR3存储器系统的主要需求以及在类似数据流处理系统中

2019-05-27 05:00:02

TMS320C32的外部存储器接口的特点 TMS320C32是一个32位微处理器,它可以通过24位地址总线、32位数据总线和选通信号对外部存储器进行访问。其外部存储器接口结构如下图l所示。 在图l中

2019-06-14 05:00:08

供电(可由子卡提供); 动态存储性能:1.存储带宽:64位,DDR3 SDRAM,500MHz工作时钟;2.存储容量:最大支持4GByte DDR3 SDRAM; 其它接口性能:1.1个高精时钟单元

2017-05-26 15:57:19

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

,根据不同操作完成对应接口的时序控制[7],进而实现对DDR3的正确读写访问。2 DDR3存储器控制模块设计DDR3 IP核生成的控制器逻辑框图如图2所示,采用UI接口的方式相比于AXI4接口,不需要自己

2018-08-02 09:32:45

的冲突。帧地址控制模块控制帧地址的切换。为了提高并行处理的速度,简化数据读写冲突,将图形数据和视频数据分别存储在不同的DDR3中。2DDR3存储器控制模块设计MIG生成的DDR3控制器的逻辑框图[5

2018-08-02 11:23:24

12位,扩展成16位后进行存储,DDR3内部以1067M处理速度,32位的处理带宽进行存储,写数据时从地址全0写到地址全1,读数据时也从地址全0读到全1,经对比无误,说明该控制器能够较好地进行高速读写操作。`

2018-08-30 09:59:01

选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足

2019-06-24 06:07:53

如图1所示由视频A/D采集的原始视频数据,在Philips公司生产的TM1300专用视频处理器中压缩后,通过USB控制器送至PC机。PC机的整个通过USB控制器传输到TM1300,解压后发送至视频D

2021-06-29 07:30:00

FIFO、紧耦合存储器及16位的SRAM集成在SOPC系统中,并在FPGA开发板上实现的方法,其内容包括外设的接入方法,以及紧耦合存储器如何通过紧耦合从端口直接与处理器的紧耦合数据/指令主端口相连等

2018-12-07 10:27:46

的片上系统。针对本设计中触控屏帧缓存读操作的特点,选择以Avalon 主端口接口的形式对模块进行开发,大大提高了处理器运行效率,同时实现了触控屏控制器IP 核的参数化设计, 提高了控制器对于不同LCD

2018-11-07 15:59:27

存储器带宽的利用效率,设计成批量读写的模式,减少读写切换工作的开销。该内存模块具体完成以下功能:1)使用DDR控制器IP核完成对DDR内存的初始化配置,产生读写命令和其他各种控制信号;2)根据出口

2019-04-12 07:00:09

你好,如果我在HP库(Bank 32,33,34)中有一个QDRII接口,在设备XC7K325T中的HR Bank(Bank 17,18)中有一个DDR3接口,我该如何为MIG生成的内存控制器选择

2020-07-22 11:04:20

ddr3.xdc的一些严重警告,因为似乎DDR3控制器的某些内部信号在xdc中受到限制,但是Vivado无法找到它们。这可能发生在其xdc文件试图限制IP内部逻辑的其他核心中。所以我想知道在这种情况下,我

2019-03-26 12:29:31

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

现在因为项目需要,要用DDR3来实现一个4入4出的vedio frame buffer。因为片子使用的是lattice的,参考设计什么的非常少。需要自己调用DDR3控制器来实现这个vedio

2015-08-27 14:47:57

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据

2022-02-08 07:08:01

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

Virtex-6内存控制器只能支持16 x(128Mb x 8b)MT41J128M8 IC = 2GB DDR3 SDRAM。我的问题是:1.当我在存储器接口生成器的控制器选项级选择“组件”时,我已经可以选择

2020-06-15 06:59:58

我正在使用vivado 2014.3,MIG 7 ddr3 verilog IP,内存时钟400MHz,用户时钟200 MHz,ddr数据宽度64位,AXI数据宽度128位。在我的系统中,我们有微型

2020-08-05 13:45:44

vc707)上进行了仿真和实现。它的简单CPU有:2个端口(指令地址和指令数据)3个端口(mem地址,mem数据输入,mem dataout),...但现在我想使用SRAM DDR3作为主存储器

2020-08-25 13:19:36

大家好,我试图通过vivado v14.3生成DDR3控制器。我正在选择DDR3 SODIMM模块“MT8KSF1G72HZ-1G6”。该工具支持该器件,最高频率可达666.66MHz,但该模块的数据表明最高频率可达800MHz。请帮我确定问题所在。感谢致敬Tarang JIndal

2020-07-31 06:07:43

你好我们计划使用XC7Z020 PS部分的DDR3内置控制器将其连接到2个芯片[MT41K128M16] -32位数据宽度。我们计划再使用一个DDR3组件来支持ECC。请告知我们XC7Z020 PS中DDR3控制器引脚的详细信息,包括ECC引脚详细信息。谢谢Pench

2020-03-24 09:34:32

产品,其它产品也将陆续推出。凭借其创新的架构和强大的功能,SPEAr1310以最先进的技术引领嵌入式市场,实现前所未有的成本竞争力、性能以及灵活性。”内置DDR2/DDR3内存控制器和完整的外设接口

2018-12-12 10:20:29

作者:Robert Taylor1德州仪器双数据速率同步动态随机存取存储器。哇!真够拗口的。很多人甚至可能都不认识这个全称;它通常缩写为 DDR 存储器。图 1 是 PC 中使用的 DDR 模块图

2018-09-18 14:11:40

目前有一个项目需要使用DDR3作为显示缓存,VGA作为显示器,FPGA作为主控器,来刷图片到VGA上。VGA部分已经完成,唯独这个DDR3以前没有使用过,时序又比较复杂,所以短时间内难以完成,希望做过DDR3控制器的大神指点一二。急求!!!!

2015-11-16 09:18:59

在用DM642处理图像数据过程中,摄像头采集回来数据后是先存入ddr存储器,然后cpu从ddr中提取数据在进行处理,在进行输出,是这个过程吗?

2015-11-29 15:20:55

数据速率 800Mbps

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

GL50H 为用户提供一套完整的 DDR

2023-05-19 14:28:45

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

比较简单,就是让核0和核1同时处理DDR3中一个4K行的数据块,其中核0处理前2K行,核1处理后2K行,两者所处理数据以及所用参数都不交叉,处理后数据以EDMA data sorting模式存储至DDR3

2018-06-25 07:14:21

FPGA与DDR2存储器接口DDR2控制器的设计原理是什么?DDR2控制器的应用有哪些?

2021-04-30 06:28:13

一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波形数据

2019-06-03 05:00:05

SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适合那些需要海量存储器的应用领域,例如视频方面。那么有谁知道,高速SDRAM控制器的视频有哪些吗?

2019-08-09 06:23:43

传输给AT91RM9200;在AT91RM9200上,Lnux驱动实现存储器映射I/O和物理内存重映射,避免了视频数据在应用程序与内核之间的二次拷贝,提高了应用程序的网络发包效率。1 HPI接口硬件设计HPI是一种并行接口

2019-05-22 05:01:10

用中档FPGA实现高速DDR3存储器控制器

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(D

2010-01-27 11:25:19 879

879

MAX17000A脉宽调制(PWM)控制器为笔记本电脑的DDR、DDR2、DDR3存储器提供完整的电源方案。该器件集成了一路降压控制器、一路可

2010-11-25 09:26:24 682

682

使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 基于协议控制器的DDR3访存控制器的设计及优化_陈胜刚

2017-01-07 19:00:39 15

15 控制器用户接口设计方案。该控制器用户接口已经在Xilinx 公司的VC707 开发板上通过了功能验证,并成功的被应用到高速图像数据采集系统中。

2017-11-17 14:14:02 3290

3290

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储管理系统。DDR3存储器控制模块使用MIG生成DDR3控制器,只需通过用户接口信号就能完成DDR3

2017-11-18 18:51:25 6412

6412

和Stratix III FPGA的接口。

Stratix III FPGA:

具有强大的DDR3写调平功能,实现和高速DDR3存储器的接口。

提供I/O电路,能够更灵活地支持现有以及新兴的高速外部存储器标准。

保持高速数据速率时的最佳信号完整性

2018-06-22 02:04:00 3475

3475 大家好,我叫Paul Evans,是Stratix III产品营销经理。到目前为止,我已经从事了6年的双倍数据速率存储器工作,今天和大家一起讨论一下DDR3。DDR3的主要难题之一是它引入了数据交错

2018-06-22 05:00:00 8250

8250 车载视频拼接的项目,该项目使用到了LVDS高速接口和DDR3接口,摄像头采集的视频图像数据需要先存入DDR3中然后与通过LVDS传输的主机视频数据进行拼接输出,最终在屏幕上显示画中画的效果。分享给大家

2022-03-14 14:46:06 564

564

本文介绍一个FPGA开源项目:DDR3读写。该工程基于MIG控制器IP核对FPGA DDR3实现读写操作。

2023-09-01 16:23:19 743

743

电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0

正在加载...

电子发烧友App

电子发烧友App

评论