A8: 在序列总线架构下,每个pin脚可以传递较多的频宽且能够扩充到较高的频宽。相对于并行总线架构的分享式的多点拓墣型态,序列总线架构能够使不同装置间特定的点对点连结成一个网络。 这消除了总线仲裁,提供具决定性的低延迟且大量简化热插拔/热交换系统的执行。

Q9: PCI Express 架构基础规格( PCI Express Architecture Base Specification)的关键特色为何?

Q9: PCI Express 架构基础规格的关键特色如下:

? 能够与现有PCI列举的和软件的装置驱动模块兼容,当允许软件随着新版与已扩充的PCI架构的特性所具备的优点而演变时,提供一个平顺的移转到新的硬件上。.

? 每个点对点的相互连结可能有1, 2, 4, 8, 12, 16或 32的双单工 2.5 Gbps线路 (2.0 Gbps 的有效速率),在节点间提供可达到128Gbps(16 gigabytes/秒)的可扩充的频宽。

? 可预测的低延迟 能够促成应用装置所需的实时数据传递

? 将每个pin脚的频宽最佳化,以促成独特且小型的格式因素,简化电路板的设计和信号路径,并减少信号整合的问题。

? 一个阶层化的架构,使得实体层可以附加在铜质、光学的和新兴实体的信号媒体,以允许它能够移转到未来的传输作业上,并且在不影响数据链路层或传输层的情况下,对其架构(scheme)进行编码。

? 服务品质(Quality of Service;QoS) 属性。.

? 原生的热插拔/热交换能力。

? 原生的电源管理能力能力。

? 已延伸的配置属性

Q10: PCI Express 架构 如何传递每个pin的最佳频宽,而这么做为什么是很重要的呢?

A10: PCI Express 架构利用今日通用的SERDES技术和 8B/10B 数据编码作业,以创造2个不同的、4个pin脚、2.5Gbps、具备一个嵌入式时脉的双单工序列数据流的组合。PCI Express 架构也删除了 PCI/PCI-X当中所有用来对应到数据封包当中具相同功能性的sideband 信号pin脚。PCI Express 架构 提供每个单一pin脚125 MBs的频宽[(2 directions * 2 Gbps/direction * 1000 Mbs/Gbs) / (8 bits/byte * 4 signal pins)].

除了有来自减少pin脚数目的成本节省之外,PCI Express 架构的每个单一pin脚的最佳频宽允许弹性的输入/输出分割,能够区分系统和终端使用者对于热转换PCI Express扩充模块的存取。

Q11: 在通讯系统当中, PCI Express 架构是否打算用在控制面、数据面或者两者都有?

A11: 两者都有。一个与32个数据线路点对点连结的PCI Express 架构,提供总共128 Gbps (16 gigabytes/second)的频宽,是支持足以通讯系统在可预见的未来,在控制与数据面上的需求。

Q12: PCI Express 架构会用在装置外或内建于装置中呢?

A12: PCI Express 架构会用在于应用装置外或内建于其中是一个视应用装置需求而决定的。当PCI Express 架构应用的最初焦点是放在内建于应用装置当中,它也被期望能够随着时间的演进,PCI Express 架构将会被用在应用装置内,以供输入/输出的扩充之用。

Q13: 第一个采用PCI Express架构的产品预定何时推出?

A13: PCI-SIG 不能预测供货商在产品供应上的有效性或着对他的会员公司尚未公开的产品计划加以评论;然而,有些会员厂商已经宣布他们期望在2003年下半年初期将以PCI Express 基础规格为基础的产品进行投产。

Q14: 与PCI/PCI-X?相较, PCI Express 架构的系统成本是多少?

A14: 负责建立PCI Express 架构规格工作小组的关键原则是要做到让第一代的PCI Express 架构系统的成本不能比传统的32位 33MHz PCI系统来得贵。然而,市场的力量最终将会决定PCI Express 架构系统的成本。可以预期的是,当技术本身随着时间进步而获得改善,实现PCI Express应用的成本将会比相同的PCI设计来得低。

Q15: PCI Express 架构 打算取代PCI/PCI-X®吗?

A15: 不。PCI-SIG 未来将同时支持PCI/PCI-X 和PCI Express 架构。两个架构皆拥有有利于PCI-SIG会员的关键属性。 PCI-SIG 将会持续、主动地推广这两技术,以做为系统扩充槽、转接卡、嵌入式系统的host和其它各种应用的连结接口之用。 OEMs 和IHVs业者 将决定哪一种技术用在哪一种特定的应用上。

Q16: PCI Express 架构的插槽打算与应用系统中的PCI/PCI-X slots插槽同时存在吗?

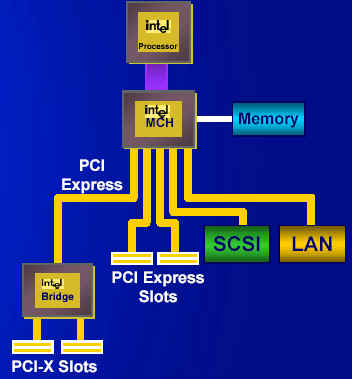

A16: 是的。PCI Express 架构插槽能够与PCI/PCI-X 插槽同时存在。PCI-SIG正在开发一个 PCI Express 桥接规格 ,以定义出足以连结一个服从 PCI Express 基础的接口和一个服从 PCI 2.3/3.0或 PCI-X 1.0/2.0的接口间的一个产业标准。实际的系统执行将由OEMs和IHVs业者决定。

Q17: PCI Express 架构 打算取代AGP吗?

A17: 是的。PCI Express 架构最初所锁定的应用目标之一就是用来做为一个图形处理用的输入/输出附加节点。第一代的PCI Express 架构提供比AGP8X多两倍的频宽。此外, PCI Express 架构支持在单一系统上的多个图形处理用的输入/输出装置。PCI-SIG 主动地推广PCI Express 架构以做为取代AGP之用。.

Q18: PCI Express 架构 打算取代Serial ATA吗?

A18: 不。PCI Express 架构不打算取代Serial ATA。PCI Express 和 Serial ATA是互补的技术。 Serial ATA 是专门用在内部的储存装置且软件是百分之百地与当前的平行ATAi相容。。PCI Express 架构 和Serial ATA之间的关系将会与当前的 PCI 与Serial ATA.的关系相似。

Q19: PCI Express 架构将会对 1394b, USB 2.0, InfiniBand* 架构, Fibre Channel, SCSI, Etherne和其它受欢迎的输入/输出技术产生怎样的影响?

A19: PCI Express 架构, 透过它现存的目前对于许多诸如热插拔/热交换与实时装置等尖端的连结特性的支持,被预期作为连结这些和其它输出/输入技术的系统连结桥接标准。OEMs 和 IHVs业者将会决定这些技术当中有哪一种技术是用来连结到PCI Express 架构上.。

Q20: PCI Express 架构会与HyperTransport竞争吗?

A20: 不会。PCI-SIG 将HyperTransport和PCI Express 架构 视为互补而不是竞争的技术。 HyperTransport 是一个在一块板子上芯片对芯片的相互连结,它能够与一个拥有PCI Express 架构系统连结的应用装置同时存在的。

Q21: PCI Express 架构是与RapidIO相竞争的吗?

A21: 可以说 是也可以说不是。RapidIO实际上有两种不同的实体规格,一个是在板子上芯片对芯片的相互连结,另外一个是序列式的系统相互连结,它们共享一个相同的标准。 PCI-SIG视RapidIO在板子上芯片对芯片 相互连结的作法是与PCI Express架构互补而非竞争。.

序列RapidIO 本身的定义是指一个专供通讯系统所用的系统相互连结的接口,且在这些应用系统上是与PCI Express 架构 相竞争的。PCI-SIG相信PCI Express 架构 会是更好的选择,因为它可同时应用于运算与通讯的市场,且能在所有的目标市场上提供更快、更广但更便宜的采用成本等优势。PCI-SIG 主动地推广PCI Express 架构 ,使其做为通讯系统所用的一种更好的系统相互连结的替代方案。PCI-SIG在全球市场的推广以及得益自大量生产的经济利益,将使得PCI Express 架构的采用对通讯系统的市场而言是相当有值得的。

Q22: 相对于其它的PCI-SIG技术,PCI-Express架构的专利授权模式有所改变吗?

A22: 没有。所有的PCI-SIG 技术是根据PCI-SIG By-Laws的规范,统一地来管理。

电子发烧友App

电子发烧友App

评论