ST-BUS总线规范

在电信设备中,模块互连普遍采用总线架构,其中应用最为广泛的是ST-BUS(即Serial Telecom BUS,串行电信总线)。电信芯片制造商Zarlink半导体公司根据电信模块化应用的需要对ST-BUS的信号与时序规范作了明确的定义,该总线在很大程度上简化了不同模块间的通信方式,可以传输包括音频、视频、控制信息等在内的数据信息。

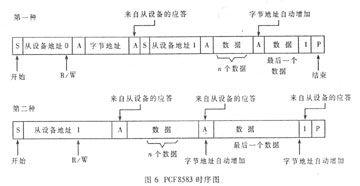

由定义知,ST-BUS是一种传输数字信息的高速同步串行通信总线,其总线信号包括帧同步、位时钟和串行数据,帧同步信号是一个负脉冲,分为两种类型:类型0的 F0 同步脉冲仅出现在帧开头的一个位时钟周期内,它决定着总线上各部件何时开始收或发一帧信息数据流;类型1的 F1 同步脉冲也出现在帧开头且需维持8个位时钟周期(即一个时隙周期),在此期间总线上各部件 同时也在收或发信息数据流,相比于类型0,类型1同步方式应用较少。另外,考虑到模块间通信速率的匹配,ST-BUS定义了四种标准时钟频 率 ,即 16.384MHz、8.192MHz、4.096MHz和2 .048MHz,均可用作部件的内部时钟,且同一时刻只能选择其一,而自适应系统则采取自动选择 模式。除了常用的基准时钟2.048MHz外,其余时钟频率总是对应数据速率的两倍,即ST-BUS支持的最大数据速率为8.192Mbps。假设ST-BUS速据速率为2.048M bps,则时钟频率可在2.048MHz与4.096MHz中任取其一。ST-BUS的一个完整 帧周 期为12 5μs,每帧又根据不同数据传输速率分为不同的时 隙数。不过,为了与E1信号时隙一一对应,实际应用中ST-BUS常采用每帧32时隙的信号方式。

由于通信系统越来越复杂,为了提高设备兼容性且便于系统或模块升级,电信设备广泛采用模块化设计思想和方法,而ST-BUS正是便于将各功能模块联接起来协调工作的总线标准,所以模块只要具备ST-BUS总线接口就能方便地嵌入特定通信设备。

ST-BUS收发电路与CPLD逻辑设计

ST-BUS收发电路设计

为了实现完整的ST-BUS收发模块,首先介绍一下ST-BUS收发电路设计。

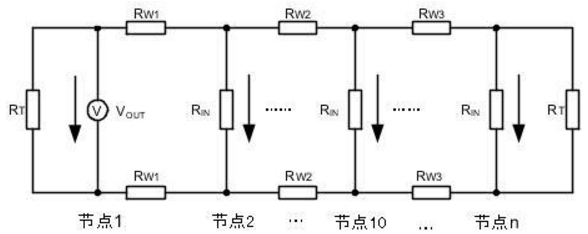

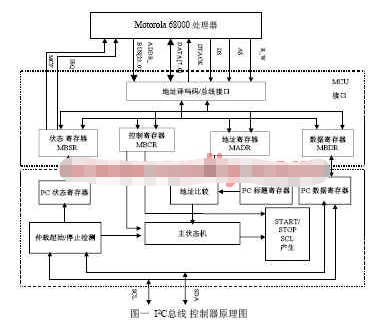

为ST-BUS收发模块的电路原理图。这里,ST-BUS收发模块功能电路以CPLD作为核心元件,CPLD采用全球第二大可编程器件厂商Altera公司MAX7000B系列的 EPM7128SLC84-15(128个宏单元,PLCC84封装)。

同时考虑到调试与验证方便,电路模块采用一个Atmel公司的AT89C51单片机(DIP40封装,文中不作详细讨论)作为外部控制器。单片机通过四线制SPI接口设置收发模块的工作模式、时隙参数等,也可通过SPI或并口P0接口读(或写)ST-BUS收发模块接收(或发送)的数据,并通过RS-232C接口与计算机通信。另外,ST-BUS收发模块还设置了2个中断输出信号,并在分别连接到单片机的中断输入引脚 INT0 和 INT1 。因此,单片机也可以采取中断方式来读取ST-BUS收发模块接收到的数据。

单片机的外接晶体11.059MHz;CPLD片上系统时钟由外部4.096MHz有源晶体振荡器提供,采用10引脚双列插座的JTAG接口实现CPLD的在线编程;RS-232C与TTL接口电平转换采用MAXIM公司的MAX232ACPE。

ST-BUS收发模块设计

ST-BUS收发模块的功能是实现ST-BUS总线串行数据的可靠收发,接下来就探讨 F0 同步模式下ST-BUS总线接收与发送的模块设计。

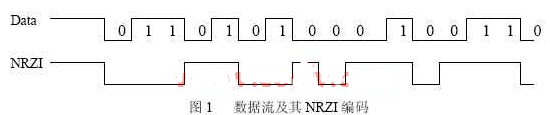

ST-BUS总线数据收发规则为:发送端在时钟C2上升沿时发送数据,而接收端在C2下降沿时采样并读取数据,且 F0 同步脉冲在第0时隙开始的第一个C2上升沿处保持低电平。需要说明的是,实际应用中ST-BUS收发模块的一端接到各种接口的数据交换单元,且通过外部控制接口设置各路数据所占用的时隙位置参数,不过,在不影响本文讨论ST-BUS收发模块设计的情况下,这里暂不考虑收发数据与其它接口的交换部分,并假定收发模块各路数据通道占用固定的时隙通道(实际上,这里是由单片机软件设置的)。

另外,根据时钟等信号的提供方式,时序电路模块的工作模式常分为主动模式和被动模式两种。若电路模块所需时钟和同步信号均来自外部,该模块就处于被动模式;相反,若时钟和同步信号由模块内部产生,该模块就处于主动模式。下面的讨论假设模块处于时钟与帧同步均由外部提供的被动模式,但讨论结果对主动模式同样成立。

(一)接收模块

ST-BUS接收模块的功能原理框图。从本质上讲,ST-BUS接收模块的功能是根据所设置的ST-BUS时隙位置接收所需数据,再通过特定接口送出接收模块并维持至少一个位时钟周期。模块接收数据时,由于发送端(见后)在上升沿处建立ST-BUS总线上的数据信号,此时位时钟C2上升沿应仅触发状态转换及计数器计数,因此接收端应在数据稳定期间采样,即在C2下降沿处读取串行数据。因此,双通道接收模块用Verilog HDL实现时可采用两个always语句加以描述,部分代码如下(为了简化起见,信号和常数声明略,下同)。

第一个always语句内容为:

if(!f0)begin //同步检测,同步则置标志并复位计数器

f0_flag<=1;bitcounter<=bitsofbyte-1;bytecounter<=0;end

else if(f0_flag)begin //判断当前是否处于同步状态

case(bitcounter) //时隙内位计数处理

0:begin bitcounter<=bitsofbyte-1; //当前时隙末位则位计数器复位

if(bytecounter==(bytes_per_frame-1)) //检查是否帧末时隙

begin bytecounter=0; //时隙计数复位

if(f0)f0_flag<=0;end / /无同步信号则清除同步标志

else bytecounter<=bytecounter+1;end //非帧末时隙则递增

default:bitcounter<=bitcounter-1; //正常接收数据时计数器递减

endcase end

位时钟C2下降沿触发数据锁存并作接收处理,则第二个always语句内容为:

if(f0_flag)begin if(bytecounter==byte_pos1)//检查当前时隙是否接收数据

begin receive2_flag<=0;din1<=din1<<1;din1[0]<=dr;

if(bitcounter==0)receive1_flag<=1;end

else if(bytecounter==byte_pos2) //多通道接收(同上)

……

end

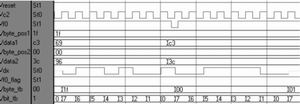

在Altera公司提供的Quartus II 5.0 SP1集成开发环境下,基于MAX7000S系列的CPLD器件EPM7128SLC84-15对上述双通道ST-BUS接收模块作综合,占用资源为27个LC,占用率为21%。再做综合后时序仿真,结果如图4(a)。因未讨论单片机的控制接口,仿真的通道设置如下:第一通道为0时隙,第二通道为31时隙,这样设置也是为了验证帧切换问题。由仿真结果可以看出,接收模块的功能和时序正确。

(二)发送模块

ST-BUS发送模块的功能原理框图。从本质上讲,ST-BUS发送模块的功能是按照所设置的时隙将待发数据变换为特定的串行格式发送,即将数据信号转换为ST-BUS总线信号。由前述,发送端在位时钟C2的上升沿处可以既转换状态又发送数据,因此,双通道发送模块用Verilog HDL实现时可以采用一个always语句加以描述,相应的部分代码如下:

if(!f0)begin f0_flag<=1;bitcounter<=bitsofbyte-1;bytecounter<=0;

if(byte_pos1==0) //时隙0为第一通道,发送数据data1

begin dx<=data1[7];dout1<=data1<<1;dout2<=data2;end

else if(byte_pos2==0) //时隙0为第二通道,发送数据data2

……

else dx<=1'bZ; end //非选定时隙,则输出高阻释放总线

else if(f0_flag)begin case(bitcounter)

0:begin

…… //状态转换,类似于接收模块

if(bytecounter==byte_pos1-1) //发送第一通道数据

begin dx<=dout1[7];dout1<=dout1<<1;end

else if(bytecounter==byte_pos2-1)//发送第二通道数据

……

else dx<=1'bZ;end

default:begin bitcounter<=bitcounter-1;

…… //同上,发送数据

end endcase end

采用与接收模块类似的方法,在Quartus II 5.0 SP1开发环境下基于EPM7128SLC84-15器件对双通道发送模块作综合,占用资源为25个LC,占用率为20%。后时序仿真,结果如图4(b)。仿真时,为了说明双通道发送模块的发送时序与通道设置的顺序无关,与接收模块的通道设置相反,发送模块的第一通道设置为31时隙,第二通道设置为0时隙。由仿真结果可见,发送模块的功能和时序也正确。

接收和发送模块的功能原理框图可知,两个模块之间的差异只有数据收发部分,两个模块的同步检测、时隙定位以及位定位都可以共用,因此两个模块可以合并为一个收发模块,如图3(c)所示,能节省部分器件资源。从综合结果来看,如果收发模块相对独立,那么资源占用将是27+25=52个LC,占用率高达41%。而接收与发送模块合并后的收发模块,占用资源35个LC,占用率27%。显然,有效地节省了CPLD的LC资源。

上面讨论并没有严格区分被动模式和主动模式,但是,前面的电路设计已考虑到了双模式的验证,CPLD器件的外接晶体振荡器可以让ST-BUS收发模块工作于主动模式。当工作于主动模式时,收发模块会自己产生时钟和帧同步等信号,并提供给ST-BUS总线上的其它部件。相反,当工作于被动模式时,收发模块的收发部分会屏蔽掉本地时钟,而由外部ST-BUS总线提供时钟。

基于所选定的CPLD器件EPM7128SLC84-15分析收发模块最高工作性能可知,接收模块和发送模块的最高工作频率均大于20MHz。这说明,所设计模块的工作频率高于前面所述C2几种工作频率的最大值,也就是说在C2的各频率条件下,ST-BUS收发模块都是适用的。

结束语

文中所讨论的ST-BUS收发模块的实现电路及CPLD内部逻辑设计已成功应用于某专用通信设备的E1接口板,运行性能稳定。基本文中设计的收发模块,在多种不同规模的可编程器件上已成功实现了ST-BUS与RS-232等多种标准接口单元以及部分自定义接口的顺利对接,完成各种 接口与ST-BUS总线间的数据复接通信,工作性能稳定可靠。

电子发烧友App

电子发烧友App

评论