本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

,可以提供高达132MB/s的数据传送速率;它具有严格的规范,只要符合PCI规范的扩展卡插入任何PCI系统就能可靠地工作。但由于PCI总线协议的复杂性,其接口的实现比VESA、ISA和MCA等总线要困难

2018-12-17 11:23:00

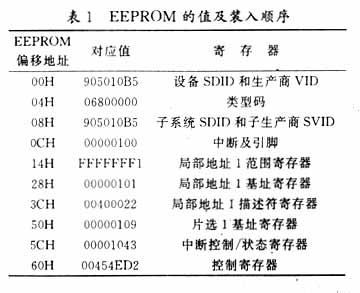

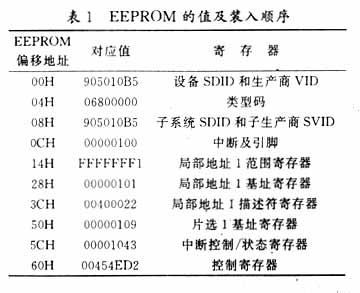

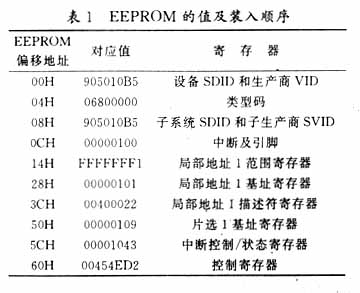

[29]置1可以用串行EE P R 0 M重新配置PCI9050。(4)访问内部寄存器 PCI9050提供一系列的内部寄存器来为总线接口设计与实现提供最大的灵活性,寄存器分为两类:PCI配置寄存器和局

2018-11-29 14:52:52

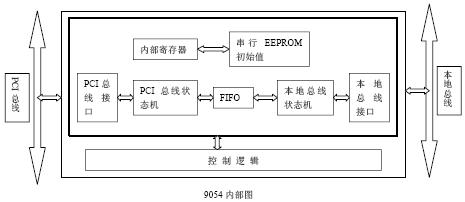

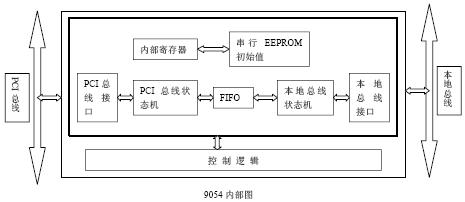

PCI总线接口的开发提供了一种简洁的方法,设计者只需设计出本地总线接口控制电路,即可实现与PCI总线的高速数据传输。图3是应用PCI9054作为接口芯片,开发PCI总线扩展卡的总体硬件框架图 下面简单

2018-12-05 10:12:42

、AMCC S5933,PLX 公司的PLX9054、PLX9080 等,通过专用芯片可以实现完整的PCI主控模块和目标模块的功能,将复杂的PCI总线接口转换为相对简单的用户接口,用户只要设计转换后的总线

2008-10-09 11:23:38

PCI总线特点是什么?PCI接口开发现状如何?如何去设计PCI接口?

2021-04-29 07:09:04

有哪位大神用过pci ip核,为什么输入lm_req32请求,pci侧没有reqn请求输出呢?

2016-06-27 17:56:59

PCI总线是一种不依附于某个具体处理器的局部总线。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供了

2008-12-09 13:46:13

/s的传输速率。PCI9052对9052编程可实现复用/非复用的8位、16位、32位的本地总线接口。同时它还具有内部FIFO可以加速本地总线的操作。

2021-04-15 07:02:21

与RTL8139的接口解决方案已在试验中得到实现,并已用于IP分组语音数据的以太网传输,效果良好。随着ISA总线的淘汰,PCI接口的网络控制器必将在嵌入式领域中得到更广泛的应用。

2009-09-19 09:43:24

求大神,FPGA内部的PCI的IP软核实现PCI接口设计?

2013-05-02 16:12:21

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

数据通信接收芯片,实现DVB-ASI信号的接收。关键词:DVB;异步串行接口;PCI;IP核前言 随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息

2012-11-28 15:38:05

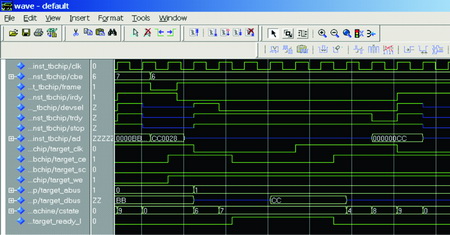

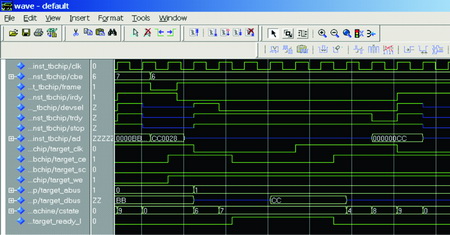

本文的应用背景为某一工业测控系统,该系统采用FPGA实现测量数据的采集和控制信号的输出,通过定制PCI接口IP实现一个32位目标设备的PCI总线接口转换。PCI核选用AlteraPCI编译器所包括

2018-12-04 10:35:21

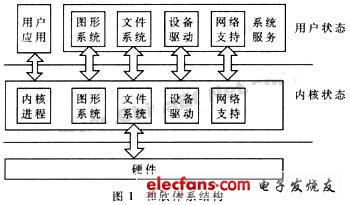

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口

2019-06-11 05:00:07

PCI核的功能则相对较弱。 根据VoIP、CDMA等先进的通讯系统对PCI总线接口的实际需求,我们通过评估比较,决定采用Altera公司的64位66MHz PCI Core,在VERIBEST

2019-04-17 07:00:06

PCI核的功能则相对较弱。 根据VoIP、CDMA等先进的通讯系统对PCI总线接口的实际需求,我们通过评估比较,决定采用Altera公司的64位66MHz PCI Core,在VERIBEST

2019-04-12 07:00:11

性,因此本文选择了PCI总线。33MHz、32位的PCI总线的数据传输速率最高可达133MBps, 完全可以满足高速实时传输的需求。选择了Altera公司的PCI编译器软件包来实现PCI接口控制电路

2018-12-07 10:34:34

(Peripheral Component Interconnect)总线是当今PC 领域中流行的总线。目前实现PCI 接口一般采用专用器件, 有效方案分为两种:使用可编程逻辑器件和使用总线专用接口

2010-09-22 08:51:09

独立的配置空间,可实现即插即用。这些优点使得PCI总线在数据采集、嵌入式系统和测控等领域得到广泛应用。实现PCI总线协议目前主要有专用接口芯片和CPLD实现两种方式。专用接口芯片使用简单方便、工作稳定

2019-05-29 05:00:02

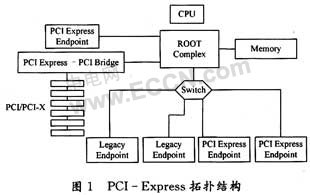

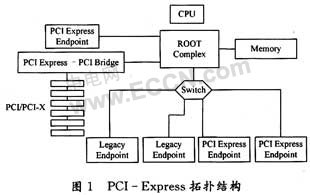

250 MB/s。对于需要与主机进行大容量传输的系统来说,该总线标准的优势是非常明显的。由于PCIE总线硬件设计简单,吞吐量大,软件向下兼容,只要找到合适的总线接口芯片,很容易将现有的PCI总线设备

2019-05-21 05:00:02

基于FPGA的PCI总线接口设计

2017-09-30 09:12:46

基于FPGA的PCI总线接口设计

2020-03-15 11:43:10

][tr][td] WISHBONE总线简介WISHBONE总线规范是一种片上系统IP核互连体系结构。它定义了一种IP核之间公共的逻辑接口,减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性

2018-12-05 10:35:32

如何实现单片机与PCI总线接口的并行通信?

2021-04-29 07:14:26

PCI总线是什么?有什么特点?如何利用FPGA去设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-05-31 06:37:24

什么是PCI总线?它有什么特点?如何利用FPGA设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-04-29 06:10:31

如何利用双端口RAM去实现PCI总线接口?

2021-05-06 06:30:53

,以及对应的波形图和 Verilog HDL 实现。我们调取的 DDR3 SDRAM 控制器给用户端预留了接口,我们可以通过这些预留的接口总线实现对该 IP 核的控制,本章节将会讲解如何根据

2022-02-08 07:08:01

本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

2021-04-08 06:25:12

设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准,因此,开发统一的IP核接口标准对提高IP核的复用意义重大。本文简单介绍IP核概念,然后从

2018-12-11 11:07:21

怎么实现基于IP内核的PCI总线接口设计?

2021-05-27 06:34:05

本文提出了一种新的包括PCI9054单周期读、写和存储器映射传输的设计,并讨论了通用PCI总线高速数据采集卡的实现方案。

2021-06-08 06:28:30

PCI总线特点及开发现状PCI接口配置空间的实现求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案

2021-04-15 06:17:20

Engineering 公司的FlightCORE-1553 IP 核作为总线协议控制器,它完全满足1553B 总线协 议,为主处理器和1553B 总线提供了完整、灵活的接口,能够实现总线控制器(BC)、远程 终端

2019-05-21 05:00:22

如何实现基于IP模块的PCI接口设计?

2021-04-20 06:28:50

PCI9030是什么?PCI9030主要有哪些特点?设计PCI总线接口有哪些步骤流程?

2021-04-15 06:57:46

操作系统中的实现有很大不同。首先,由于嵌入式处理器的时钟频率低,地址、数据总线窄,导致嵌入式系统对一个通用IP包的处理要花费更多的处理机时间,从而影响其他任务的执行,因此需要对庞大的复杂的TCP/IP

2019-04-28 09:57:18

消息。ICMP回复消息经常被用来调用ping程序测试对方主机是否在线。在嵌入式TCP/IP协议栈中,ICMP回送消息用一种十分简单的方式实现,即将ICMP类型的字段由echo类型改变为echo reply类型

2019-04-23 07:00:10

PCI核的功能则相对较弱。根据VoIP、CDMA等先进的通讯系统对PCI总线接口的实际需求,我们通过评估比较,决定采用Altera公司的64位66MHz PCI Core,在VERIBEST

2019-05-08 07:00:46

的实时性,因此本文选择了PCI总线。33MHz、32位的PCI总线的数据传输速率最高可达133MBps, 完全可以满足高速实时传输的需求。选择了Altera公司的PCI编译器软件包来实现PCI接口控制电路

2019-05-05 09:29:32

IP核来实现PCI接口,利用基于PCI协议的IP核来实现PCI接口,这种设计开发速度较快,灵活性较好,但是IP核价格昂贵。采用FPGA实现PCI总线协议。采用CPLD/FPGA等可编程逻辑器件实现PCI

2019-05-30 05:00:02

以下为IP核验证平台提供的IP核的详细说明: 功能0 PCI 桥设备 完全VHDL、VERILOG源代码设计提供,无时间限制; 支持PCI总线桥规范1.1协议; 支持PCI总线规范2.3协议

2019-06-20 05:00:02

PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。 S1500硬件验证板照片以下为IP核验证平台提供

2019-06-12 05:00:07

一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波

2019-06-03 05:00:05

的PCI总线速度更快(数据传输率为133 Mb/s)、实时性更好、可控性更佳,更易于实现高速实时的I/O口控制卡、通信接口卡、数据采集卡等。但PCI总线也因其32位地址与数据复用、控制总线及时序较复杂

2019-04-29 07:00:09

核处理器NIOSⅡ作为系统的主控制器,结合ARINC429专用器件和其他外围设备实现数据的收发功能。 ARI NC429接口板由数据收发、存储器扩展、监控、PCI总线接口等模块组成。NIOSⅡ控制

2019-04-26 07:00:08

控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。许多公司推荐使用现成的或经过

2019-04-12 07:00:09

介绍 PCI 总线的特点,对现有的 PCI 总线的接口设计方法进行分析;介绍 PCI 接口芯片CY7C09449PV的结构及其与数字信号处理器TMS320C32之间接口电路的设计,提出一种基于PCI和 C32的数据

2009-04-08 09:53:42 26

26 采用可编程逻辑器件CPLD,分四个模块——控制寄存器模块、PCI控制器状态机模块、SRAM 控制器模块和仲裁器模块,分别完成通信并解析PCI总线、PCI状态的控制和翻转、负责SRAM接口数

2009-06-01 14:25:22 16

16 基于FPGA的PCI总线接口设计::PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接

2009-06-25 08:17:18 48

48 PCI 总线接口控制器的设计是基于PCI总线的应用设计的关键所在。本文在介绍PCI9054接口控制器的基础上,给出了一种通用的高速数据采集接口的设计,并提出了一种新的包括PCI9054单

2009-07-30 15:33:13 18

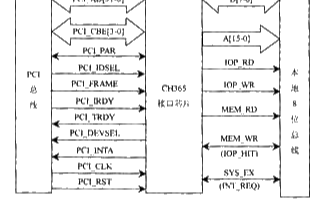

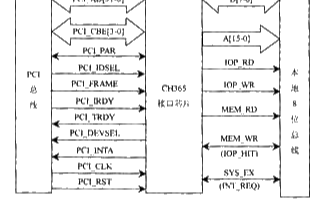

18 PCI 总线是先进的高性能32/64 位局部总线,成为微机总线标准。PCI 总线接口设计较其它总线接口设计复杂,本文讨论了接口设计的方案,选择CH365 作为接口芯片,描述了数据采集

2009-08-19 10:19:55 27

27 本文简要介绍了PCI 总线的仲裁机制, 完成了PCI 总线仲裁器核心的设计、实现。通过ModelSim 进行了软件仿真,最后在XILINX 公司的FPGA 上加以了验证。

2009-09-03 08:18:29 27

27 RJ45与PCI总线接口原理图

2009-10-27 18:24:25 232

232 摘 要: 本文采用Altera的CPLD实现了PCI总线至UTOPIA接口的逻辑转换控制,为低成本实现ATM终端奠定了基础。

2006-03-11 13:16:50 864

864

PCI总线接口定义图

为32位总线,且可扩展为64位,有124个脚(实际上去掉4个定位卡有120引脚),AD线有32条,工作频率为33MHZ/66MHZ,最大传输速率133MB/S。总

2008-05-31 14:19:10 3705

3705 PCI总线接口芯片PCI9054及其应用PCI9054是PLX公司推出的一种PCI主模式桥芯片。本文主要介绍了它的特性、功能及应用,说明了以PC

2008-10-09 11:18:03 7642

7642

基于PCI总线的GP-IB接口电路设计

摘要: 主要介绍作为从设备如何根据PCI总线协议设计PCI总线接口电路,从而实现基于PCI总线的GP-IB接口电路设计,重点阐述PCI总

2008-12-26 15:14:36 1168

1168

PCI总线定义

PCI 是 Peripheral Component Interconnect 的缩写。接口卡的外观:PCI 标准 32位/64位 接口卡

2009-02-12 10:37:58 1455

1455

PCI9052总线接口芯片及其ISA模式应用

PCI9052是PLX公司开发的服从PCI协议的从模式接口芯片,它能够实现ISA总线到PCI总线的平滑转换。主要阐述了PCI9052

2009-05-04 21:48:45 1562

1562

PCI9052是PLX公司开发的服从PCI协议的从模式接口芯片,它能够实现ISA总线到PCI总线的平滑转换。主要阐述了PCI9052在ISA模式下的应用开发过程和方法,并给出了一个实例,说明了如何

2009-05-09 12:02:57 1124

1124

摘 要 :PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接口的

2009-06-20 13:13:28 936

936

摘 要: 以自行研制开发的PCI高速总线背板为背景,系统地论述了PCI总线的仲裁机制、总线的缺省占用、仲裁信号协定及优先级仲裁算法,给出了采用EPLD实现仲裁器功能的编程设计

2009-06-20 13:32:20 961

961

基于PCI IP核的码流接收卡的设计

本文介绍了一种基于Altera公司的PCI接口IP核的DVB码流接收系统的硬件设计方案及设计要点的分析。该设计采用Altera公司的新一代FPGA

2009-09-26 18:02:08 716

716

基于Virtex5的PCI-Express总线接口设计

PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG联合成立的Arapahoe Work Group共同草拟并推举成取代PCI总线标准的

2009-10-05 10:25:20 910

910

基于FPGA的PCI接口控制器的设计与实现

pci总线是高速同步总线,采用高度综合优化的总线结构,目前广泛应用于各种计算机系统中,总线以32位(或64位)

2009-12-14 14:29:54 1736

1736

PCI总线目标接口芯片PCI9052及其应用

摘要:PCI9052是PLX公司继PCI9050之后新推出的一种低成本的PCI总线目标接口芯片,它传输速率高,数据吞吐量大,

2010-03-03 19:21:58 2492

2492

PCI总线接口芯片CH365

一、概述

CH365是一个连接

2010-11-08 17:43:04 5334

5334 提出了一种使用CPLD解决双端口RAM地址译码和PCI接口芯片局部总线仲裁的的硬件设计方案,并给出了PCI总线接口芯片

2011-01-07 12:13:03 1891

1891

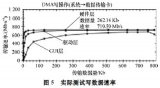

出了一种PCI总线从设备的CPLD实现方法。该方法遵从PCI规范2.2版,实现了资源自动配置并且支持数据突发传输。试验证明该方法的有效性,其突发传输速率可达20 MBs -1 。

2011-11-30 17:06:11 60

60 本文将对PLX公司的PCI9052总线目标接口芯片的功能及其在PCI板卡设计中的应用进行介绍,PCI9052是PLX公司继PCI9050之后新推出的、可用于低成本适配器的总线目标接口芯片。

2011-12-29 09:42:51 3083

3083

IP核验证平台采用6层板PCB设计,使用独立的外部时钟同步芯片,可以为PCI及其它接口提供稳定的零延迟时钟系统电路,满足PCI总线的时钟要求,使验证平台高速,稳定,可靠的工作。

2012-01-17 14:02:19 1501

1501

《LogiCORE IP Initiator/Target v3.1 for PCI 入门指南》提供经过全面验证的 32 位和 64位预实现 PCI 总线接口。本指南讲述支持的基于 Virtex 和 Spartan 架构的 32 位和 64位核的设计流程,并且介绍

2012-01-17 16:15:44 0

0 PCI总线是目前最为流行的一种局部性总线 通过对PCI总线一些典型功能的分析以及时序的阐述,利用VetilogHDL设计了一个将非PCI功能设备转接到PC1总线上的IP Core 同时,通过在ModeISim SE PLU

2012-04-01 15:06:44 40

40 利用PCI专用接口芯片PCI9052和DEI1016 429总线收发芯片设计了ARINC429接口卡,采用DSP作为主控CPU完成数据自动处理,用双口RAM完成DSP与PCI总线数据交换。实验表明:所设计的接口卡传输效率高

2012-05-09 16:14:25 80

80 根据1553B数据总线协议及其接口技术要求,设计了一种基于PCI局部总线的1553B总线接口卡。系统使用PLX公司的PCI9052和DDC公司的1553B协议芯片BU-61580,通过FPGA芯片EP1C12B进行PCI协议和1553B协议

2012-07-31 14:09:03 3098

3098

Xilinx FPGA工程例子源码:PCI总线IP核(华为的商用)

2016-06-07 14:54:57 30

30 PCI总线规范与其接口

2017-10-31 09:09:14 18

18 基于PCI桥接IP Core的VeriIog HDL实现

2017-10-31 09:28:57 22

22 PCI总线的ARINC429接口卡设计

2017-10-31 10:13:01 25

25 采用IP核的设计方法,将外设组件互连标准(PCI)总线接口与具体功能应用集成在一个FPGA上芯片, 提高了系统的集成度。在对PCI IP核进行概述的基础上,介绍了IP核的设计方法,实现了PCI总线

2017-11-17 12:27:03 4488

4488

。本文介绍PCI Express 总线接口的设计方法,,并实现一个基于IP核的PCI Express 总线接口。

2018-07-18 10:35:00 1873

1873

PCI9052是PLX技术公司继PCI9050之后推出的低成本、低功耗、高性能总线接口芯片,通过该芯片可以使多种局部总线快速转换到PCI总线上。

2019-10-22 16:46:53 3510

3510 所以若用FPGA芯片直接设计PCI接口则难度大且开发周期长,而专用的PCI接口芯片可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的接口。

2020-04-23 09:17:50 2877

2877

PCI总线协议非常复杂,目前实现PCI接口的有效方案分为两种:即使用可编程逻辑器件和使用专用总线接口的器件,可编程逻辑器件实现PCI接口比较灵活,可以利用的器件比较多,现在有许多生产可编程逻辑器件的厂商(如Xilinx的Logicore和Alerra的AMPP)都提供经过严格测试的PCI接口功能模块

2023-08-01 14:37:19 553

553

电子发烧友App

电子发烧友App

评论