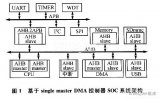

为了在嵌入式系统设计中实现对SDRAM存储器的访问,本文提出了一种基于AMBA-AHB总线规范的SDRAM控制器设计方案。方案首先简要介绍了AMBA总线规范,然后在完成整个存储控制器的整体框架

2014-01-02 13:59:42 4099

4099

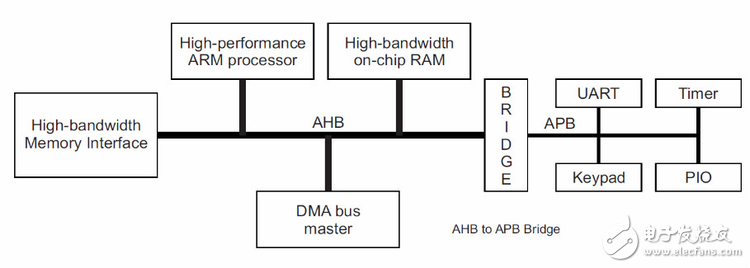

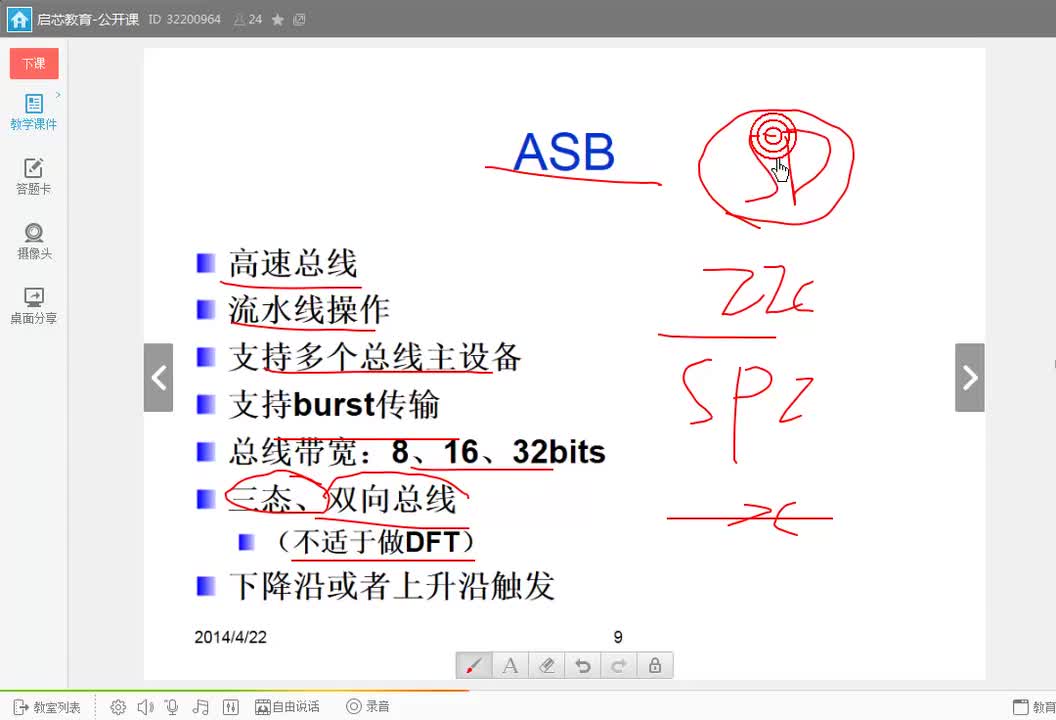

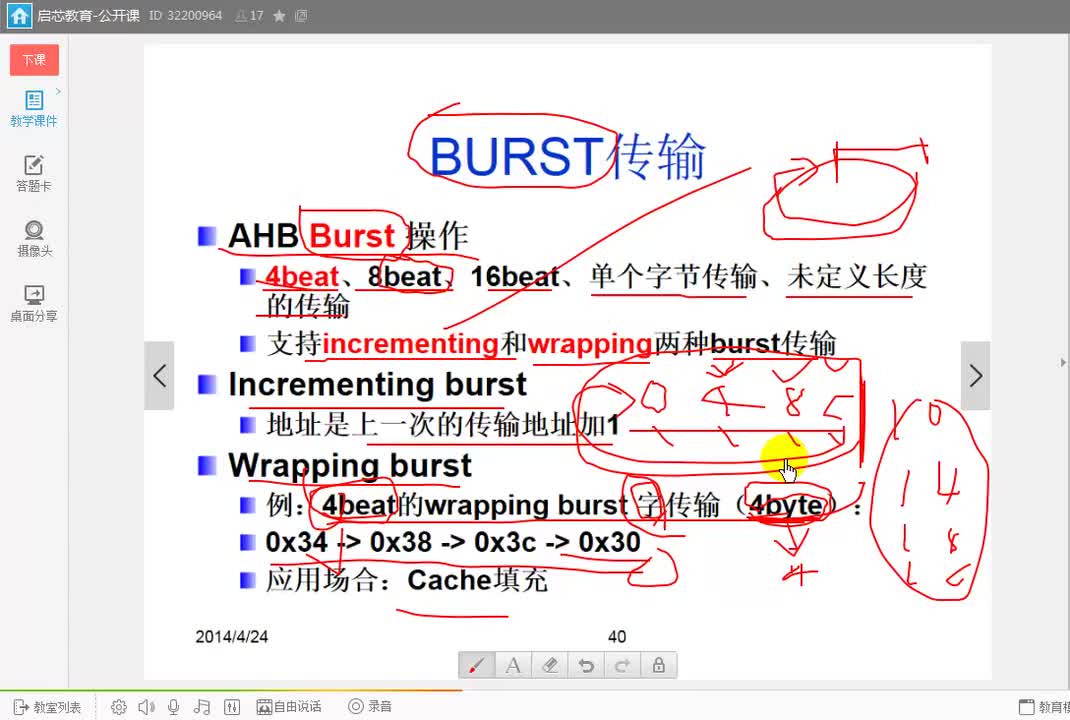

AHB总线用于高性能,高时钟工作频率模块。AHB在AMBA架构中为系统的高性能运行起到了基石作用。AHB为高性能处理器,片上内存,片外内存提供接口,同时桥接慢速外设。高性能,数据传输,多总线主控制器,突发连续传输,分步传输。

2016-12-30 09:59:41 1735

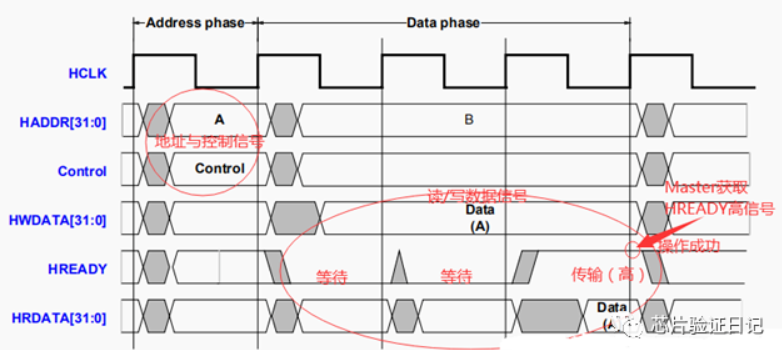

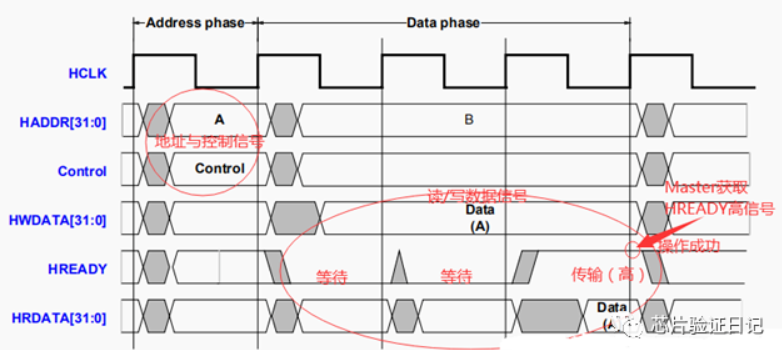

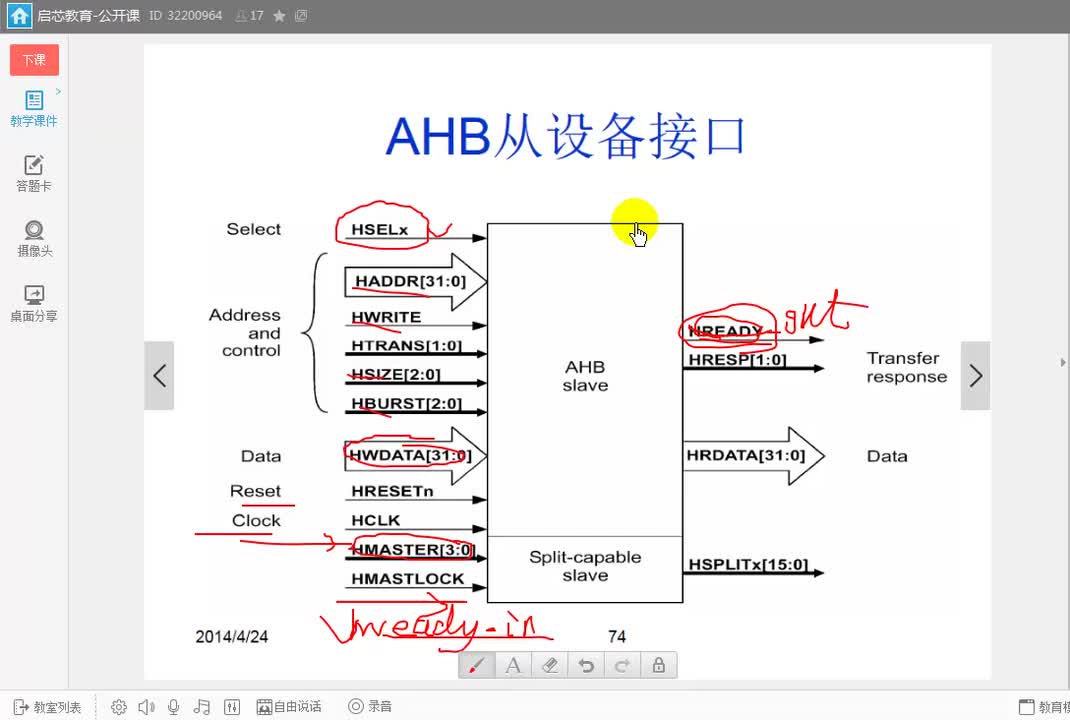

1735 在AHB总线中,hready这个信号是最难理解,最容易搞错,也是系统调试的过程中出问题最多的地方之一,同时也是很多面试官最喜欢问的知识点之一。本文做一个梳理,帮助大家彻底理解这个知识点。

2022-12-17 08:07:49 4171

4171

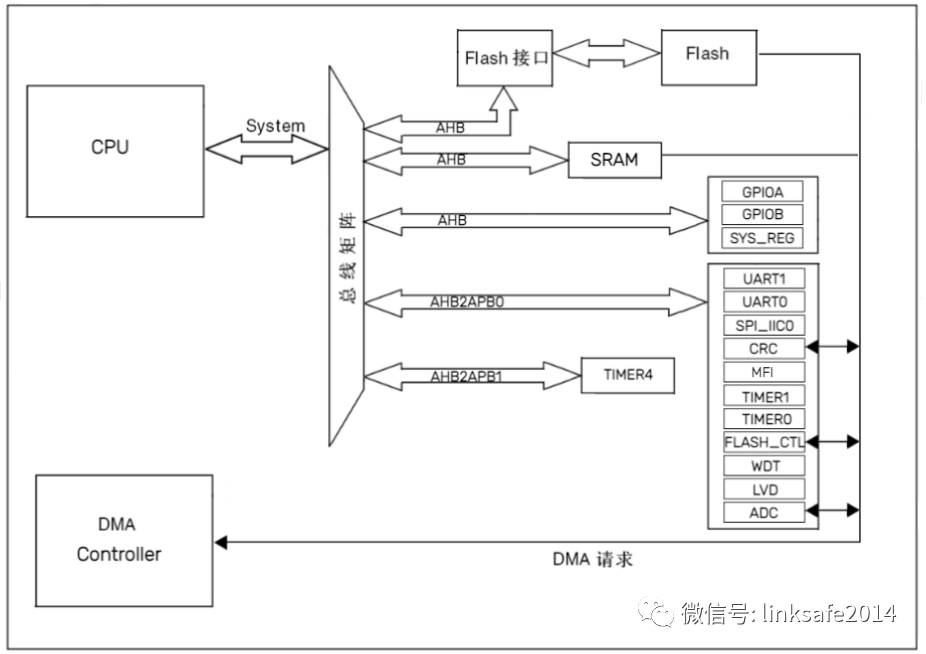

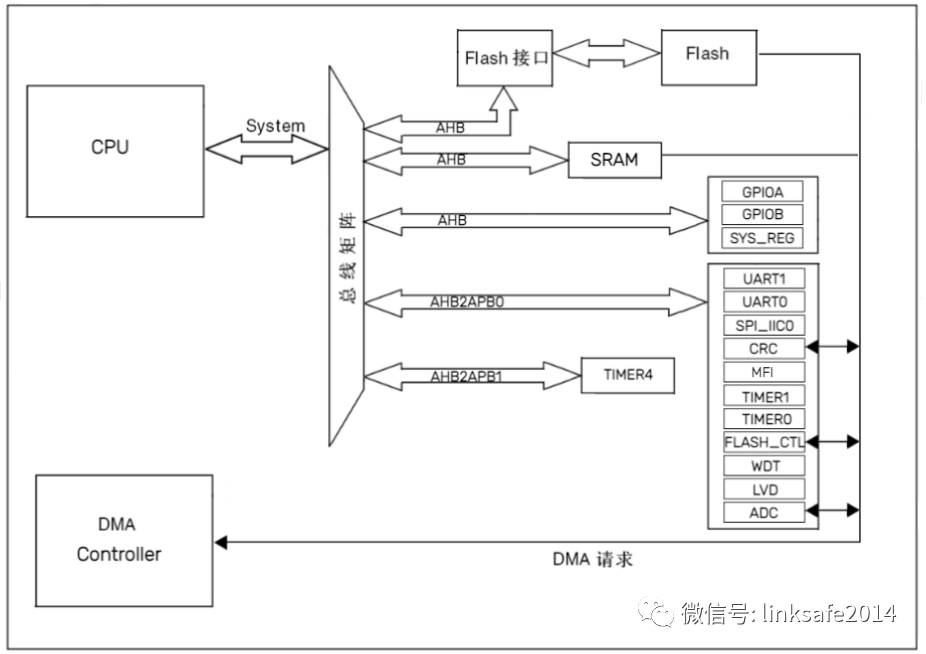

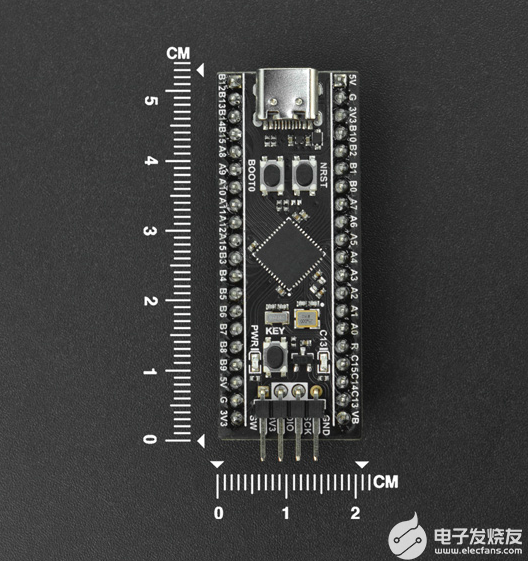

本系统的主要功能部件包括ARM Cortex-M0内核、AHB总线矩阵、CMSIS-DAP调试端口、语音识别模块、SD卡模块等,具体系统框图如下图所示。

2023-04-03 11:39:43 1055

1055 AHB到APB的桥(AHB2APBx),它连接所有的APB设备这些都是通过一个多级的AHB总线构架相互连接的。

2023-06-16 11:14:34 195

195

HREADY信号是slave发出的控制谁的?看有人写的程序HREADY即当了输入又当作输出,看的晕乎乎的。HRESP信号,是和HREADY信号同步吗?两者怎么配合?希望大家用一个等待过程的实例,说明一下。非常感激!

2015-01-04 13:58:26

随之改变。仲裁:主设备可以在被分配到总线而有不需要使用总线的时候进行一个不是IDLE的传输吗?应用于:AHB是的。主设备可以在被分配到总线而有不需要使用总线的时候进行一个不是IDLE的传输。但是请注意

2022-06-08 16:20:29

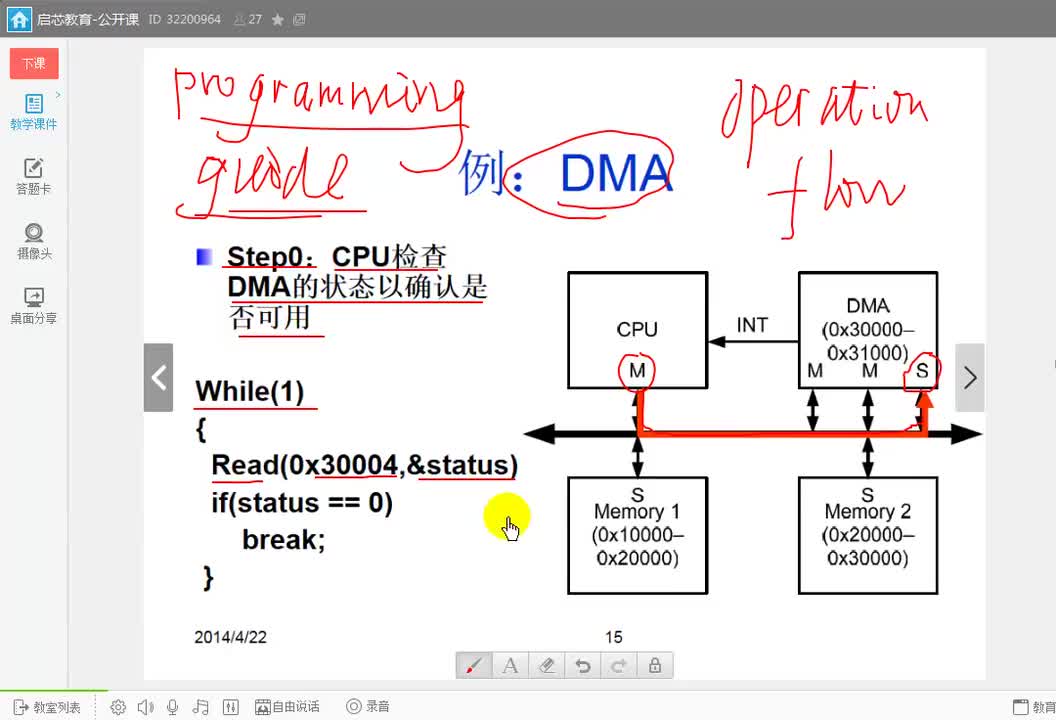

1、AHB总线:(1)Flash 存储器;(2)DMA;(3)复位和时钟控制;(4)CRC;(5)以太网;(6)SDIO;2、APB2总线:(1)USART1;(2)高级控制定时器TIM1和TIM8

2021-08-02 06:22:03

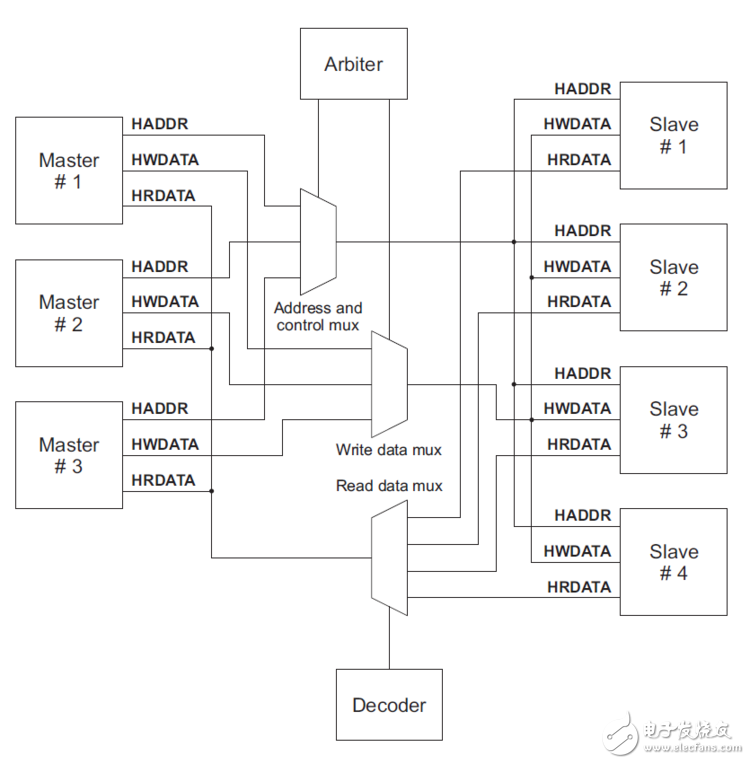

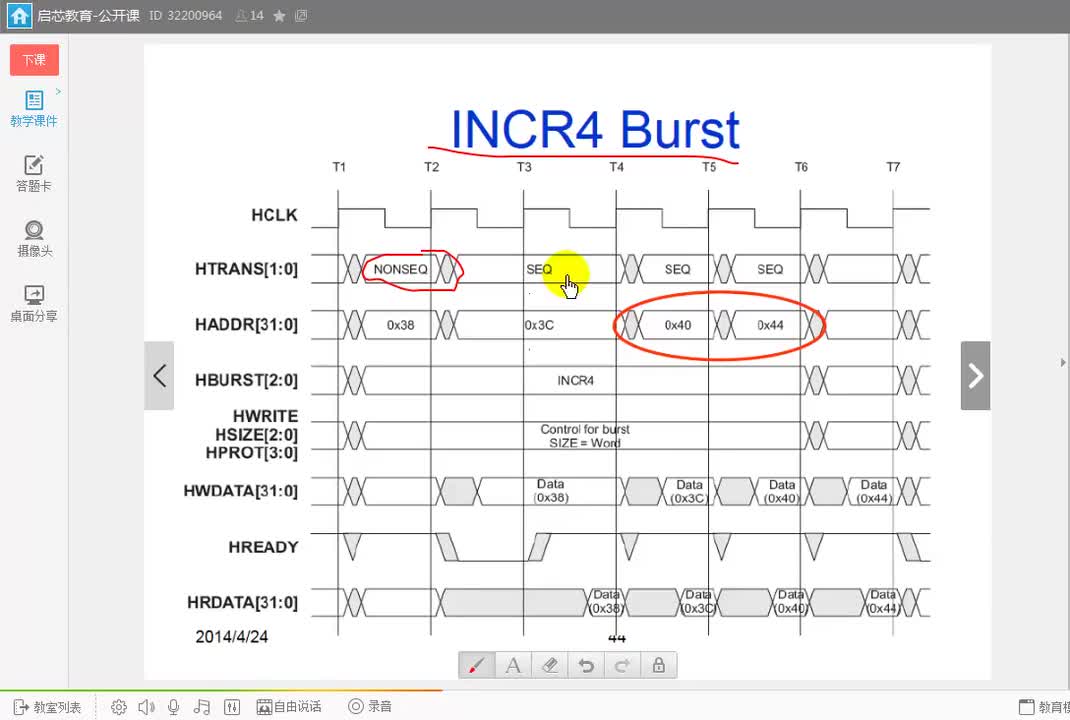

1、AHB传输的时序图分析正文1:AHB章节最后再复习一遍多主机的概念:总线是被总线上所有的部件所共享的一组通路(连线),对于支持多主机的总线,如果某一个主机想要与其他的部件进行通信(获得

2022-06-09 17:45:33

。SYSCLK 系统时钟,最大72MHzHCLK:AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟经过总线桥AHB--APB,通过设置分

2021-08-18 06:22:16

AHB总线由哪些部分组成?分类有哪几种?

2022-02-16 07:03:13

高级高性能总线是什么意思?从通信双方数据交互的层面说一下总线是如何通信的?

2021-11-29 06:16:38

主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连:● 八条主控总线:— Cortex™-M4F 内核 I 总线、D 总线和 S 总线— DMA1 存储器总线— DMA2 存储器总线

2021-08-05 07:51:29

本帖最后由 eehome 于 2013-1-5 10:04 编辑

AHB总线规范读书笔记

2012-08-16 20:46:07

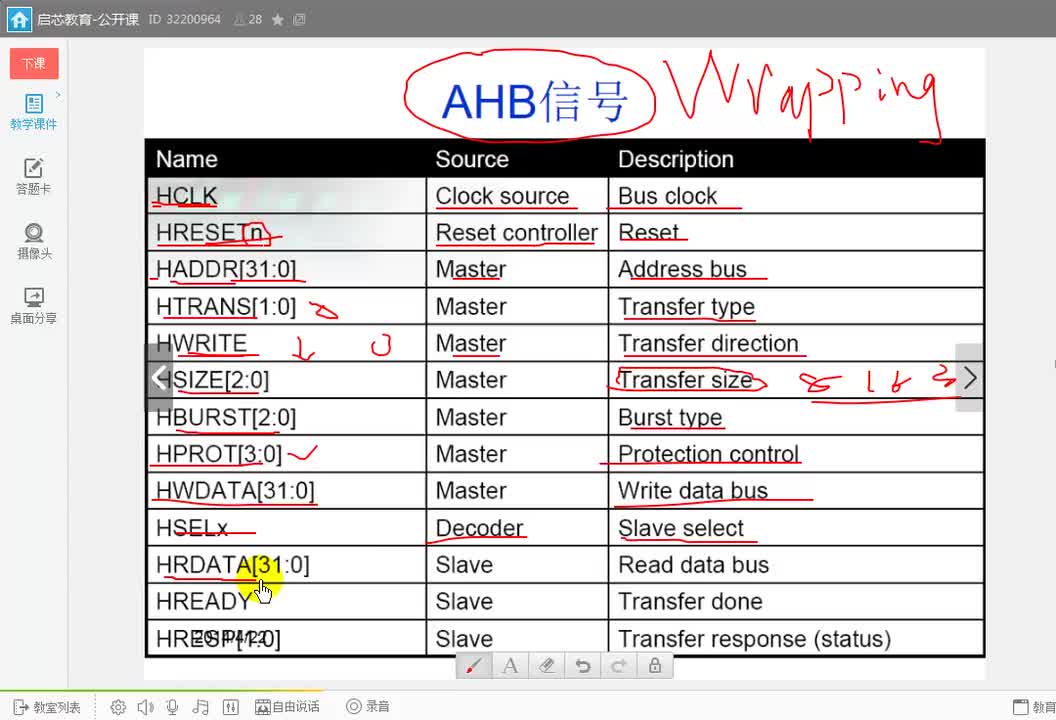

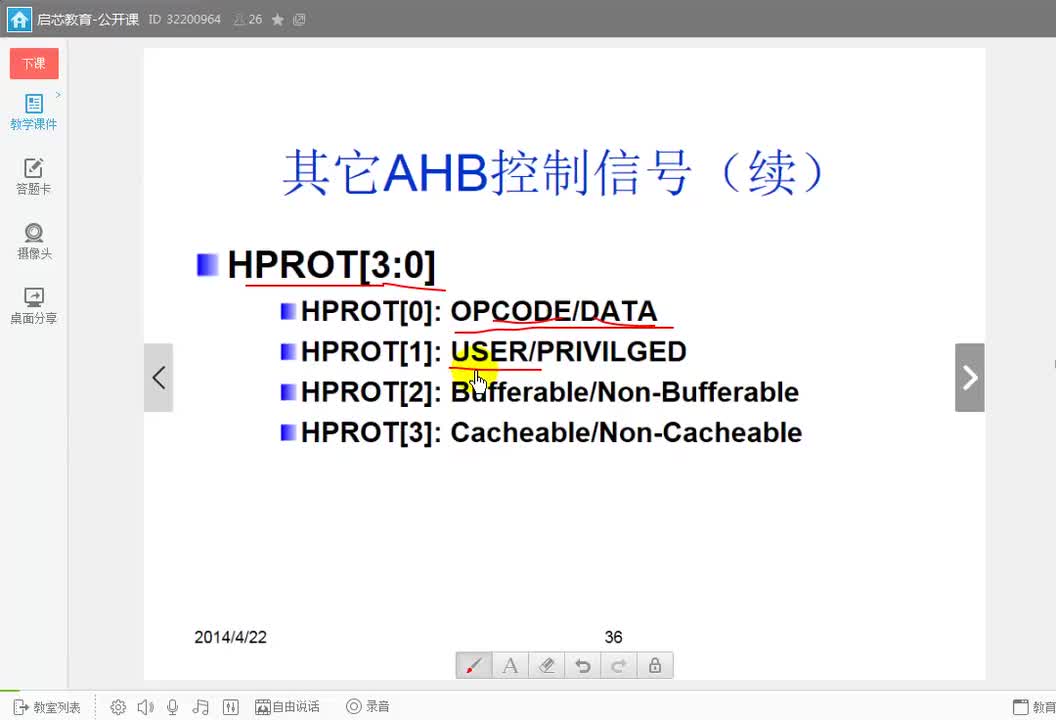

1、AMBA AHB总线信号接口介绍Advanced Microcontroller Bus Architecture, 即 AMBA,是 ARM 公司提出的总线规范,被很多 SoC 设计所采用

2022-04-07 10:03:19

STM32菜鸟学习手册——1、AMBA、APB、AHB简介芯片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构

2022-02-17 07:18:33

1、漫谈AMBA总线-AHB在上篇文章文章我们已经分析了AMBA总线系列中的APB总线的优点和缺点。总结得出:缺点1: APB支持且仅支持一个主机缺点2: APB两个周期才能完成一个数据的传输

2022-06-07 16:57:54

一、概括 首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。 南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率高

2021-08-20 06:18:24

一、概括首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率高

2021-08-23 07:34:30

, ASB, APB);Qchannel文章目录1 AMBA总线2 AHB2.1 一个典型的基于AHB的微控制器2.2 AHB总线互联结构:中心选择器连接master与slave2.3 AHB的特性3 APB4 AHB和APB的区别与联系4 Q-channel1 AMBA总线内容来源:维基百科词条-Ad.

2022-02-09 07:46:07

ARM用AHB总线single模式的执行效率,比如要写50个数据或者读取50个数据,50个cycle能搞定吗?

2022-06-08 10:31:23

什么是AMBA?AMBA分为哪几种?AXI、AHB与APB的性能有什么不同?AHB总线是如何组成的?APB总线有哪些主要应用?

2021-06-18 06:55:01

问答选编问:Cortex-M1微控制器有哪些接口资源?答:Cortex-M1处理器挂在AHB总线上,AHB总线通过桥接逻辑可以挂APB总线,APB总线上可以挂的接口有IIC、UART、PWM、中断

2019-07-26 07:46:51

第一级,Cortex-M1 内核及 ITCM、DTCM; 第二级,AHB 总线及 GPIO、CAN、Ethernet、DDR3 Memory、PSRAM、SPI-Flash、AHB Master

2022-10-13 06:58:05

Gowin_PicoRV32 系统架构包括 Gowin PicoRV32 内核、指令存储器ITCM 和数据存储器 DTCM、轻量化 UART、AHB 总线扩展接口和 Wishbone总线及外部设备,如图 1-1 所示。

2022-10-14 06:56:23

MCU 内核系统,包括 MCU Core、AHB 总线及外部设备、AHB2APBBridge、APB1 总线及外部设备等。 FPGA 内核系统,包括 MCU 内核系统的时钟和复位信号输入、MCU

2022-10-13 07:51:10

VIC是一款符合高级微控制器总线体系结构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

VIC为中断系统提供接口,并通过两种方式改善中断延迟:

•将中断控制器移至AMBA AHB总线•为高优先级中断源提供矢量中断支持

2023-08-02 13:57:35

STM32总线STM32F1时钟系统STM32F4时钟系统1 STM32总线首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘

2021-08-19 06:50:28

AMBA是什么?AHB总线和APB总线的作用是什么?STM32F103系列芯片的总线结构是由哪些部分组成的?

2021-11-03 08:10:01

系统架构

多层AHB总线矩阵

存储空间

存储器映射

片上SRAM

位带操作

片上闪存

自适应闪存加速器(STM32F2新增)

启动模式

代码空间的动态重映射(STM32F2新增)

内嵌bootloader

2023-09-13 06:20:58

DMA新增特性简介和功能框图 双AHB主端口和AHB总线矩阵 DMA控制器的channel、stream和仲裁 FIFO(Vs. Direct模式) (STM32F2新增) 数据pack

2023-09-13 07:02:59

STM32F301x6/8的ADC具有高性能与低功耗的特征。该ADC具有AHB从总线接口,允许快速数据处理;且ADC转换时间与AHB总线时钟频率无关,相互独立。也就是说,该系列的ADC可以拥有

2021-08-18 06:41:06

Kbytes),备用SRAM高达4 Kbytes,宽范围的强化输入输出以及外部连接至两个APB总线,三个AHB总线和一个32-bit多AHB总线矩阵.所有设备提供三个12位模数转换器,两个数模转换器,一

2021-08-12 07:33:05

主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连:● 八条主控总线:— Cortex™-M4F 内核 I 总线、D 总线和 S 总线— DMA1 存储器总线— DMA2 存储器总线

2022-01-19 06:10:45

的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率高。另外,南桥最后...

2021-08-23 07:56:19

时钟的区别:最常见的是,从外部8MHz的输入源为始,这个源会经过锁相环(PLL)的9倍频至72MHz,然后分别供给Cortex-M3内核、AHB总线、APB1总线、APB2总线使用:

-供给

2012-11-04 13:39:52

处理器的微控制器都可以由这个定时器获得一定的时间间隔。2. SysTick相关寄存器状态寄存器-CTRLSTCLK外部时钟源:AHB总线时钟的 1/8FCLK 内部时钟:AHB总线时钟——STM32F103是72MHz重装载数值寄存器-LOAD当前值寄存器-VAL校准寄存器-CALIB

2021-08-12 06:32:31

的广泛应用,已经成为SoC 设计中广泛使用的总线标准。AMBA rev20中的AHB,采用地址/数据分离格式,支持固定长/不定长猝发(burst) 交易、分裂(split) 交易特性和多个主设备的总线

2019-05-13 07:00:04

demo的代码里面将AHB 时钟设置到200MHz但是 数据手册 手册里标明 最高只能到166Mhz,这是很么情况到底哪个是对的,电机系统和ADC也是AHB 总线上的 到底哪个时钟参数

2023-06-13 07:13:58

我有一个 imxrt1170 板,想使用 flexspi1(连接到 fpga)。我想在 flexspi1 上使用 AHB 总线操作,但是当我访问 BASE_ADDR(0x30000000U

2023-03-27 08:16:47

网上整理的,三条时钟总线上挂的外设简单列举如下:1、AHB总线:(1)Flash 存储器;(2)DMA;(3)复位和时钟控制;(4)CRC;(5)以太网;(6)SDIO;2、APB2总线:(1

2021-08-19 07:32:59

这个不是直接把MAC时钟给关了吗?void ETH_DeInit(void){RCC_AHB1PeriphResetCmd(RCC_AHB1Periph_ETH_MAC, ENABLE);RCC_AHB1PeriphResetCmd(RCC_AHB1Periph_ETH_MAC, DISABLE);}

2019-11-07 04:27:08

的时候选择占用总线或者让主机释放总线两种方式。那么,对于主机来说,主机发出的完整的Burst没有完成,卡在发出的Burst中间的某一个Transfer中。主机需要怎么应对这样的情况呢?如下表所示(漫谈AMBA总线-AHB(2)):原作者:木飞 IC解惑君

2022-06-08 17:05:35

SYSCLK 系统时钟,最大72MHzHCLK:AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟经过总线桥AHB--APB,通过设置分频,可由HCLK得到 PCLK1

2019-06-04 06:28:39

CMSDK工具设计了AHB总线系统,在基于单级AHB总线的框架下,通过APB桥接器和AXI桥接器扩展了APB总线和AXI总线,进而构成该SoC高效的总线框架。通过搭建高效的总线系统将M3处理器与硬件加速

2022-08-26 15:23:33

强有力的后盾,将各种高速设性能发挥到淋漓尽致。 LPC3000系列采用了多重AHB总线架构,各个高速外设同时运行,没有速度瓶颈。 超强的浮点和DSP数据处理能力、超高的数据传输速度和丰富的片内高速外设

2013-02-20 11:30:52

我想知道我们填写什么样的值以及什么影响 AHB 总线请让我明白。const uint8_t AHBPrescTable[16] = {0, 0, 0, 0, 0, 0, 0, 0, 1, 2, 3

2022-12-07 08:49:35

SoC架构如下图所示,整个SoC基于CMSDK开发,除顶层模块与添加到自定义LCD外设模块外,无需添加或编写任何verilog代码。当前版本SoC采用两级AHB总线:第一级AHB总线矩阵上总共有5个

2022-06-22 16:01:31

用CubeMX配置外设时钟分频时,CubeMX只能看APB/AHB时钟,至于外设具体挂在哪个总线上,总是要翻手册查看。本文一次性摘录出来备查。F10x(摘自STM32 RM 008)举例

2022-01-19 08:16:04

ASB和APB,为了节省面积,这时候的总线协定都是采用3态的总线。后来的AMBA 2.0版本,新增了AHB总线,共定义了3组总线:高性能总线(AdvancedHigh Performance Bus

2022-04-21 09:39:55

问题描述:由于芯片size和物理走线的原因,AHB总线信号无法在1拍时钟内从Master传到Slave端(假设信号必须从芯片的最左边到最右端,且左右相距较远),现在设想的解决办法

2021-06-23 09:01:13

介绍一种跨时钟域的32位AHB总线桥的设计与实现。通过采用状态机设计以及使用预防死锁与解除死锁相结合的方法解决死锁,使得该桥支持读写burst、读预取、总线抢占式仲裁等多种

2009-04-15 09:05:40 30

30 如何有效的对SoC 设计进行验证已经成为缩短设计周期的关键问题。针对这个问题,本文提出一种形式化建模与验证方法,对片上系统AMBA 工业总线规范的AHB 总线协议进行形式

2009-11-30 15:29:18 9

9 本文首先介绍了AHB和OPB总线协议特点,并在此基础上详细阐述了OPB_AHB总线桥接器的功能和设计思路,最后给出了OPB_AHB的验证方法和仿真结果。并在Xilinx的EDK环境下利用MicroBlaze软

2009-12-26 17:08:12 23

23 针对标准AHB总线对具有特定访问时序的设备数据传输效率较低的情况,提出一种新的实现方案。利用AHB总线突发传输时的组合信息,根据某种算法生成地址和控制信号,以提

2010-11-11 11:16:34 36

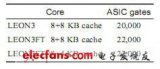

36 本项目利用LEON3的高性能、易编程、开源等优点,开发了AHB总线接口和DMA控制器,实现了Speed专用信号处理器的软件可编程,大大简化了Speed用户的开发过程

2011-06-08 10:31:31 1374

1374

本文介绍S3C2410芯片通过AHB总线与FPGA进行硬件连接技术和基于QuartuslI环境下AHB总线控制时序的实现方法以及ARM-Linux平台下的AHB总线驱动程序的开发。

2017-08-30 15:37:45 3

3 时常常捉襟见肘。 DMA通道合计有12个。可以在座ADC项目时使用DMA。可以提高程序效率。因为不用再从ADC寄存器中读取值。System总线通过总线矩阵完成DMA与外设通讯。AHB总线通过

2017-09-21 09:36:23 6

6 AHB,是Advanced High performance Bus的缩写,译作高级高性能总线,这是一种“系统总线”。AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。AHB 系统

2017-11-14 16:36:43 17155

17155

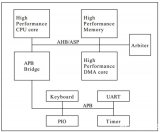

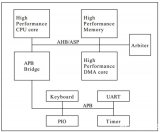

一个典型的基于AMBA 的微控制器同时集成AHB(或ASB )和APB 接口,如图2 所示。ASB总线是旧版的系统的总线,而新版的AHB 总线增强了对性能、综合及时序验证的支持。APB 总线通常用作的局部的第二总线,作为AHB 或ASB 上的单个从属模块。

2018-08-10 09:45:10 6975

6975

在图1所示架构中,每次DMA传输都要发起1次读与1次写操作。若在DMA传输期间有需要紧急处理的异常响应,AHB总线此时又被DMA控制器占用,则处理器只能等DMA控制器释放AHB总线后才能占用AHB总线进行操作,影响处理器效率与系统对异步事件的响应速度。

2018-08-24 15:34:53 1563

1563

4千字节,以及连接到两条APB总线、三条AHB总线和32位多AHB总线矩阵的广泛增强I/O和外围设备。这些设备还具有自适应实时存储器加速器(ART Accelerator™),该加速器允许在CPU频率

2019-09-26 08:00:00 4

4 本文分析了基于芯核的嵌入式CPU 设计的特点,提出了设计基于ARM 核的嵌入式CPU内AHB 接口存在的空洞问题。结合体系的设计,给出了通过改进AHB 总线解决这些空洞的方法。最后讨论了嵌入式CPU 在硬件上对AHB 接口的实现。

2019-10-18 16:13:56 3

3 2 MB,SRAM高达256 KB),备份SRAM高达4 KB,以及连接到两条APB总线、两条AHB总线和一个32位多AHB总线矩阵的大量增强I/O和外围设备。所有设备均提供三个1

2019-12-27 08:00:00 5

5 2 MB,SRAM高达256 KB),备份SRAM高达4 KB,以及连接到两条APB总线、两条AHB总线和一个32位多AHB总线矩阵的大量增强I/O和外围设备。所有设备均提供三个1

2020-01-09 08:00:00 0

0 Kbytes),备份SRAM高达4 Kbytes,以及连接到两条APB总线、两条AHB总线和32位多AHB总线矩阵的广泛增强I/O和外围设备。所有设备均提供三个12位ADC、两个DAC、一

2020-04-27 08:00:00 49

49 KB,RAM高达1 MB(包括192 KB的TCM RAM、高达864 KB的用户SRAM和4 KB的备份SRAM),以及连接到APB总线、AHB总线、2x32位多AHB总线的大量增强I/O和外围设备矩阵和

2020-10-09 08:00:00 29

29 HME-M7它是集成了高级 MCU (Cortex-M3)内核与更高性能 FPGA 资源的智能型芯片。MCU与FPGA可以使用AHB 总线实现数据交互,这就是FP AHB 总线接口。使用AHB总线

2020-11-11 08:00:00 14

14 AHB总线(AdvancedHigh-performanceBus)是AMBA(AdvancedMicrocontrollerBusArchitecture)片上总线体系的一部分。在SOC芯片中,AHB总线主要应用于对性能要求较高的组件之间互联,如用于CPU和片内高速RAM、DMA之间互联。

2020-12-10 10:13:49 3451

3451 CAN是ControllerAreaNetwork的缩写,是最初由Bosch公司开发的一种通信协议,后来被定义为IS011898的国际标准。CAN是一种有效支持分布式实时控制并具有高安全级别的串行通信协议,其应用范围覆盖从高速网络到低成本的多线路互连。

2021-03-29 10:10:10 11

11 ,具有512KB的ROM,128 KB的SRAM,以及连接到两个 APB 总线、两个 AHB 总线和一个 32 位总线的各种增强型 I/O 和外设多 AHB 总线

2021-09-24 17:44:15 5812

5812

一、概括首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率

2021-11-26 10:51:04 10

10 STM32F301x6/8的ADC具有高性能与低功耗的特征。该ADC具有AHB从总线接口,允许快速数据处理;且ADC转换时间与AHB总线时钟频率无关,相互独立。也就是说,该系列的ADC可以拥有

2021-11-26 12:51:03 3

3 处理器的微控制器都可以由这个定时器获得一定的时间间隔。2. SysTick相关寄存器状态寄存器-CTRLSTCLK外部时钟源:AHB总线时钟的 1/8FCLK 内部时钟:AHB总线时钟——STM32F103是72MHz重装载数值寄存器-LOAD当前值寄存器-VAL校准寄存器-CALIB

2021-12-02 18:36:06 9

9 , ASB, APB);Qchannel文章目录1 AMBA总线2 AHB2.1 一个典型的基于AHB的微控制器2.2 AHB总线互联结构:中心选择器连接master与slave2.3 AHB的特性3 APB4 AHB和APB的区别与联系4 Q-channel1 AMBA总线内容来源:维基百科词条-Ad.

2021-12-05 15:36:05 16

16 1M字节和 192K 字节)和高达 4K字节的后备 SRAM,以及大量连至2条APB总线、3条AHB总线和1个32位多AHB总线矩阵 的增强型I/O与外设。 所有型号均带有3个12位

2022-10-17 17:10:27 1089

1089 华大电子MCU CIU32F011x3、CIU32F031x5 器件采用 32 位多层总线结构,该结构可使系统中的多个主机和从机之间的并行通信成为可能。多层总线结构包括一个 AHB 互联矩阵、两个 AHB 总线和两个 APB 总线。

2022-11-11 11:24:10 492

492 V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。

2023-04-14 10:54:54 2764

2764 和128K字节,高达4K字节的后备SRAM,以及大量连至2条 APB总线、2条AHB总线和1个32位多AHB总线矩阵的增强型I/O与外设。

该系

2023-08-25 16:33:17 312

312

电子发烧友App

电子发烧友App

评论