10/100M以太网接口有何功能?CAN总线有哪些优点?怎样去设计RS485总线接口的电路?

2021-10-28 06:56:55

想请教各位前辈,wishbone在工作中很常用吗?我最近在学关于这个的代码,感觉很难懂,而时间又感觉不大够用,需要重点攻击, 所以想知道是否值得投入大量的时间去研究它。望各位前辈不吝赐教

2014-03-02 23:37:04

的方向,用总线操作控制电路产生的一个数据总线使能信号DBEN*来使能该双向缓冲器,使它在有别的器件对本器件进行读写操作时才打开而在其他时候关闭。3 结论 采用CPLD和双端口RAM后使VXI总线接口电路

2018-11-27 11:48:33

怎样去设计一种CAN总线通信板?如何对CAN总线通信板进行仿真?

2021-06-03 06:33:09

怎样去设计一种基于VME总线的以太网接口设备?

2021-05-27 07:00:14

怎样去设计ARINC429总线接口板的硬件?有哪些步骤?怎样去设计ARINC429总线接口板的软件?有哪些步骤?

2021-05-27 06:37:51

随着软件产品的广泛应用,对软件的知识产权保护也开始重要。软件产品通过系列号码加密,每一个软件均有唯一的产品系列号码。那么可以怎样设计一个基于计算机总线的加密电路呢?

2021-04-08 06:26:52

一个通用的Flash控制器,该控制器具有大多数eFlash宏支持的通用功能。次级侧具有用于特定实现的进程相关Flash宏。GFB用作访问闪存资源的数据路径,通过其他接口处理与控制相关的访问。这有助于通用功能在不同过程中的可重用性。

2023-08-11 07:55:01

256KA AHB interface controller; 支持 FLASH256KA Wishbone interface controller

2022-10-10 10:41:38

Gowin_PicoRV32 系统架构包括 Gowin PicoRV32 内核、指令存储器ITCM 和数据存储器 DTCM、轻量化 UART、AHB 总线扩展接口和 Wishbone总线及外部设备,如图 1-1 所示。

2022-10-14 06:56:23

专家您好!OK4418硬件资料(2.6核心板接口资源,第12页)显示外部总线 -- 数据总线可达16位, 地址总线可达14位, 但只看到8位(AP_AD0~7), 现需要用满数据16位和地址14位, 其他的数据总线和地址总线要怎样腾挪? 请指教, 急需! 谢谢![/td]

2022-11-22 07:27:50

PCI总线接口芯片9054及其应用【摘 要】PCI9054是PLX公司推出的一种PCI主模式桥芯片。本文主要介绍了它的特性、功能及应用,说明了以PCI9054作为接口芯片,开发PCI总线扩展卡的硬件

2008-10-09 11:23:38

加以选择。·具有可选的串行EEPROM接口。·具有8个32bit Mailbox寄存器和2个32位Doorbell寄存器。功能描述PCI9054的物理总线接口PCI9054提供了三种物理总线接口

2018-12-05 10:12:42

CH375是一个USB总线的通用接口芯片,支持USB-HOST主机方式和USB-DEVICE/SLAVE设备方式。在本地端,CH375具有8位数据总线和读、写、片选控制线以及中断输出,可以方便地挂接

2011-03-08 14:28:07

;strong>USB总线转I2C总线接口芯片</strong><br/>USB2I2C是一个USB总线的转I2C总线的专用接口芯片

2009-12-16 10:39:56

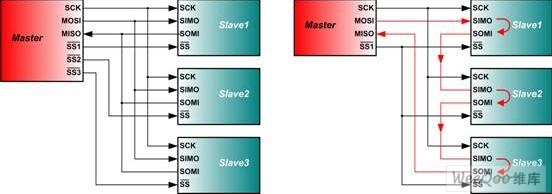

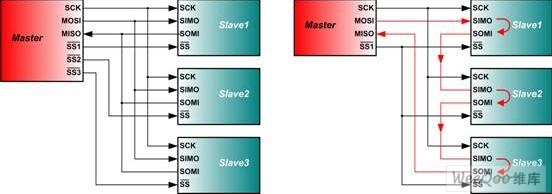

、ADC、FLASH和显示驱动器之类的慢速外设器件通信。 SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备

2012-12-19 19:38:08

从OpenCores网站下了 wb_lpc,添加进e203,寄存器读写都不行,一读就挂死了。

后来照着sirv_gnrl_icb32towishb8改了一个支持32位数据的,也一样的效果。

请过来

2023-08-12 08:26:43

是Avalon-MM的一个扩展,也可以理解为它是Avalon-MM的一个“集线器”,对一个Avalon-MM从机进行复用,这样做的好处是减少从机接口的数量,用一套总线信号就可以挂接多个从机。比如在接口信号的数量紧张

2016-11-26 17:10:43

基于wishbone总线的,但是我们平时接触的最多的还是AMBA总线。大家对AMBA总线都比较熟悉,所以我就集成ahb_to_wishbone_bridge到项目中,这样就把wishbone接口隐藏在内部,你

2022-11-23 14:47:33

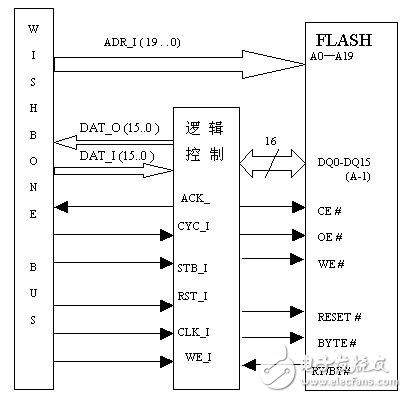

WISHBONE总线,所以本设计的接口具有可移植性。 Am29LV160D芯片特点Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器

2018-12-05 10:35:32

Peripheral Interface)串行外设接口总线[1]是一种同步全双工串行通信接口总线。由于其连线简单使用方便,故得到广泛应用。在实际开发应用中,若主控制器无SPI接口或需要与多个具有SPI接口的外设

2019-05-28 05:00:05

基于TBUF的总线宏结构是怎样的?基于TBUF的总线宏该怎样去设计?如何去验证总线宏设计?

2021-05-06 07:55:47

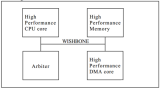

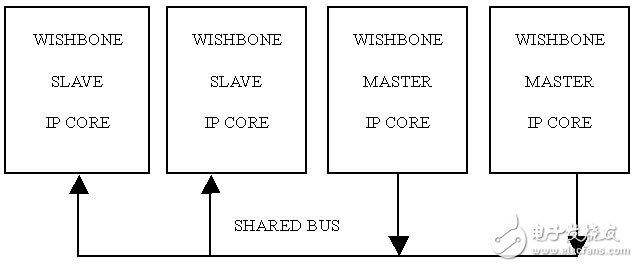

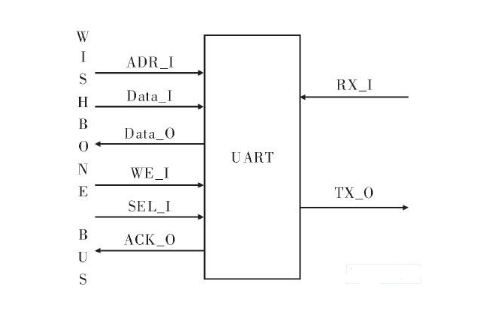

。2Wishbone总线协议Wishbone总线是一种内部总线协议。它可以将片内的各部分以及IP核等连接在一起,用来标准化各个独立部分的接口,以更加方便地架构SOC(Syctem-on-Chip)系统。其特点是结构简单

2019-05-31 05:00:07

NuMicro M05xxBN/DN/DE 系列配备一个外部总线接口 (EBI) , 用来访问外部设备.

为节省外部设备与芯片的连接引脚数, EBI支持地址总线与数据总线复用模式. 且地址锁存使能

2023-06-16 06:41:36

你好,在FM4-176L S6E2CC-ETE板上,在板上编程和Flash使用并行接口时遇到困难。如何使用外部总线接口编程外部闪存。先谢谢你。 以上来自于百度翻译 以下为原文Hello ,I am

2018-12-14 16:04:03

PCI总线是什么?有什么特点?如何利用FPGA去设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-05-31 06:37:24

什么是PCI总线?它有什么特点?如何利用FPGA设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-04-29 06:10:31

本文将介绍如何通过一个差分接口来延长串行外设接口(SPI)总线,而这可以应用在支持远程温度或压力传感器的系统的设计。

2021-05-21 06:33:53

单线接口参考设计可用于串行协议应用,如I2C和SPI总线。它在控制器和电路板上的低成本组件(如温度传感器)之间提供了一个小占地面积的通信通道。这种通信信道通常不需要高速。协议应该很简单,控制器中使

2020-04-30 09:36:09

随着现代技术的发展,SPI接口总线已经成为了一种标准的接口,由于协议实现简单,并且I/O资源占用少,为此SPI总线的应用十分广泛。目前,SPI接口的软件扩展方法虽然简单方便,但若用来通信,则速度

2019-08-09 08:14:34

本文采用基于GAL 芯片实现VME 总线接口电路的思路,对VME 总线接口设计问题进行了深入研究。文中通过软件技术实现了VME 总线地址的译码以及数 据读写与中断逻辑控制,有效简化了硬件电路的设计。

2021-05-28 06:39:41

求一个avalon总线和CY7C68013A的接口转换模块verilog代码

2014-05-15 13:06:30

PCI总线特点及开发现状PCI接口配置空间的实现求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案

2021-04-15 06:17:20

中断总线通常仅有一个处理器处理中断,监视中断请求线(IRQl~IRQ7),IRQ7优先权最高,在响应中断时,一个地址周期产生,这个地址指示请求已被响应,中断响应线(IACK)被仲裁器改变以

2019-04-22 07:00:07

Universal Serial Bus(通用串行总线)的缩写,是一个外部总线标准,用于规范电脑与外部设备的连接和通讯。是应用在PC领域的接口技术。USB接口支持设备的即插即用和热插拔功能。USB是一种统一

2018-02-06 09:50:28

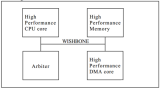

经过努力,开源软核处理器OpenMIPS的实践版终于新鲜出炉了,相对OpenMIPS教学版而言,OpenMIPS实践版最大的特点是引入了Wishbone总线接口,组建了SOPC,包括SDRAM控制器

2014-01-06 17:41:21

怎样去设计CF51QE128快速GPIO的外部总线接口?

2021-05-28 07:01:20

求一种基于USB总线的ARINC429总线接口模块的设计方案。

2021-04-30 07:01:51

PCI9030是什么?PCI9030主要有哪些特点?设计PCI总线接口有哪些步骤流程?

2021-04-15 06:57:46

没问题,现在我做了另一个底板,功能是通过SJA1000扩展CAN接口,我把SJA1000当做NOR Flash挂到GPMC总线上,当然中间通过逻辑芯片做时序转换以及电平转换。现在的问题是核心板接到这个底板

2018-06-20 03:24:28

本文将介绍如何通过一个差分接口来延长串行外设接口 (SPI) 总线,而这可以应用在支持远程温度或压力传感器的系统的设计。 在SPI应用中,主控器件和受控器件间的距离相对较近,而信号也通常不会传递到

2019-06-13 05:00:02

3.1 总线与接口概述 3.1.1 总线和接口及其标准的概念 总线:是在模块和模块之间或设备与设备之间的一组进行互连和传输信息的信号线,信息包括指令、数据和地址。

2009-03-25 13:28:07 31

31 基于FPGA的PCI总线接口设计::PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接

2009-06-25 08:17:18 48

48 PCI 总线是先进的高性能32/64 位局部总线,成为微机总线标准。PCI 总线接口设计较其它总线接口设计复杂,本文讨论了接口设计的方案,选择CH365 作为接口芯片,描述了数据采集

2009-08-19 10:19:55 27

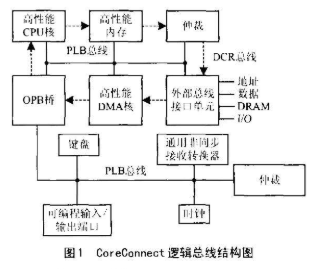

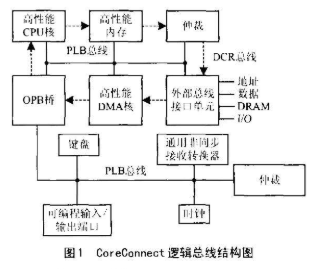

27 本文主要介绍和分析了在集成芯片设计中几种常用的片上系统总线-CoreConnect 总线、AMBA 总线、Wishbone 总线和OCP 总线,通过比较这些总线的特性及适用范围,展望了它们的发展前景

2009-12-14 11:06:48 26

26 以 FPGA 技术为基础,以Verilog HDL 为载体,设计了遵守Wishbone 片上总线规范的IP 核接口,实现了片上系统的IP 核互联。

2010-01-13 15:09:14 13

13 PCA9564是一款采用CMOS工艺,支持并行总线与串行I2C总线通信转换的接口器件,适用于微控制器/处理器使用并行总线扩展I2C总线接口。它支持并行总线与I2C总线双向通信,在I2C总线上

2010-03-10 15:47:12 51

51 PCA9665是一款并行总线与串行I2C总线接口转换的器件,适用于微控制器/处理器使用并行总线扩展I2C总线接口。它支持并行总线与I2C总线双向通信,在I2C总线上,它可以设置为主机或从

2010-03-10 15:49:10 46

46 产品概述 在汽车研发过程中,需要大量的总线数据支持,总线转换工具可以将总线数据转换为我们计算机常见接口,达到总线监视、采集、仿真等目的

2024-02-29 13:56:38

AGP总线接口定义

2008-05-31 14:20:13 2041

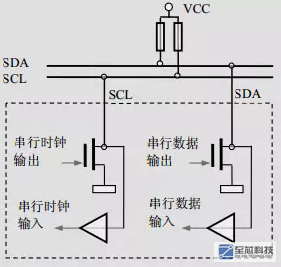

2041 ARM I2C 总线接口的寄存器设置

控制ARM 12C总线接口需要配置总线控制寄存器(rIICCON)、总线状态寄存器(rIICSTA

2009-03-14 18:00:43 1636

1636 摘 要 :PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接口的

2009-06-20 13:13:28 936

936

摘要:基于IP可重用的设计方法,利用WISHBONE总线协议,把两个已成功开发出的具有自主知识产权的THUMP内核在一个芯片上,实现了片上多处理器FPGA。开发重点是实

2009-06-20 15:29:35 656

656

显卡总线接口类型 总线接口类型是指显卡

2009-12-25 10:28:01 8737

8737 SCSI接口-总线终结器

总线终结

2009-12-25 16:00:09 1198

1198 数字接口系列文章之SPI总线

串行外设接口 (SPI) 总线是一种运行于全双工模式下的同步串行数据链路。用于在单个主节点和一个或多个从节点之间交换数据。SPI 总线

2010-01-08 10:46:41 803

803

多串口卡的总线接口

多用户卡主要有ISA、PCI、USB等几种总线接口。

2010-01-08 13:56:19 1263

1263 CAN总线与RS-485总线的通信接口设计

1 CAN总线及RS-485总线简介 CAN总线(Controller Area Network)是由德国Bosch公司于20世纪80年代专门为汽车电子控制系统

2010-01-27 10:46:07 4197

4197

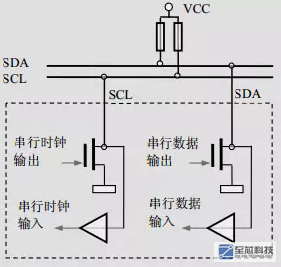

在电路设计中,I2C总线是比较常用的两线式串行通信方式,大多数的CPU都擅长于并口操作,不具备直接操作I2C总线接口的能力。为了使不具备I2C总线接口能力的CPU通过对并口的简单操作实现对I2C总线接口的控制,在分析I2C总线常用工作模式的基础上,设计实现工作

2011-02-12 16:11:01 95

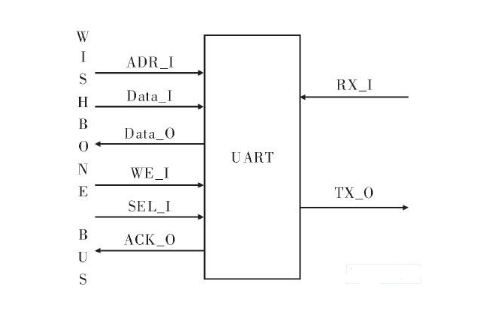

95 本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47:37 3479

3479

本文简要介绍了AMD 公司Am29LV160D 芯片的特点,并对WISHBONE总线作了简单的介绍,详细说明了FLASH memory 与WISHBONE 总线的硬件接口设计及部分Verilog HDL 程序源代码。

2011-06-23 16:32:40 18

18 通用IO接口是Soc系统中非常重要的一种外围端口.本文完成了一种基于WISHBONE总线的GPIO_W B拉制器的逻拜设计和物理实现.文中较其体地介绍了GPIO_W B核的体系结构以及WISHBONE接Q和DMA传偷方式

2011-09-21 16:57:22 32

32 该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果表明,这种新的架构

2011-10-19 15:01:54 27

27 本文介绍了CAN 总线的主要性能及特点,CAN 总线在实际工业应用中的总体结构,同时给出了CAN 总线协议转换器的硬件设计方法和通信协议。主要研究了CAN 总线接口电路设计,把所设计的

2011-10-31 15:01:47 463

463 介绍了基于硬件描述语言Verilog HDL设计的SDX总线与Wishbone总线接口转化的设计与实现,并通过Modelsim进行功能仿真,在QuartusⅡ软件平台上综合,最终在Altera公司的CycloneⅢ系列FPGA上调试。实验

2012-01-11 10:21:21 25

25 随着微电子设计技术与工艺的迅速发展,数字集成电路逐步发展到专用集成电路(ASIC),其中超大规模、高速、低功耗的新型FPGA的出现,降低了产品的成本,提高了系统的可靠性。同时,

2012-05-23 11:14:00 2578

2578

摘 要: 设计了一种基于NiosII处理器的片上系统(SoC),集成了Nios II处理器IP、PCI接口IP、网络接口IP以及基于Wishbone总线的串行接口IP核、 CAN接口IP核等。系统具有可重配置、可扩展、灵

2012-10-18 16:50:29 2487

2487

基于AMBA与WISHBONE的SoC总线桥KBar控制器的设计_陈俊锐

2017-03-19 11:31:31 0

0 大家好,又到了每日学习的时候了。今天我们来聊一聊总线接口。 一、I2C总线 I2C总线是PHLIPS公司推出的一种串行总线,是具备多主机系统所需的总线裁决和高低速器件同步功能的高性能串行总线

2018-05-17 09:30:28 13758

13758

支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总线规范的重要特征之一;

2018-07-06 08:07:31 2713

2713

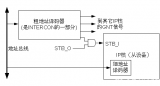

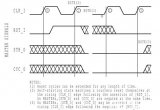

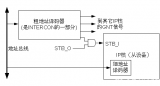

这些信号,以响应复位周期。RST_I被复位(变为0)后的第一个时钟上升沿到来后,主机接口的STB_O和CYC_O信号可以被立即置位(变为1)。

2018-07-11 09:07:14 3068

3068

注意3.30:在总线周期期间置位ERR_I信号,会立即结束该周期,意味着从机通知主机在该周期期间发生了错误。当从机逻辑电路检测到错误,便会置位ERR_I信号。例如,如果从机使用了奇偶校检,当发生错误时,从机便会通过ERR_I做出反应。

2018-07-12 08:38:51 4577

4577

可以通过用户自定义信号(即标签技术,tagging)来对Wishbone接口进行修改。标签是微处理器总线当中为人所熟知的一个概念。他允许定义与一个地址、一个数字(a data word)或一个总线周期相关的信息。

2018-07-13 09:10:15 3326

3326

所谓的小端模式(Little-endian),是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

2018-07-22 10:14:37 2762

2762

在时钟上升沿1,主设备将DAT_I()采样完成整个突发读操作,同时主设备将新地址信号放到地址总线ADR_O()上,将新数据信号放到数据总线DAT_O()上,将WE_O置为高表示写操作,CTI_O

2018-07-26 09:01:51 2959

2959

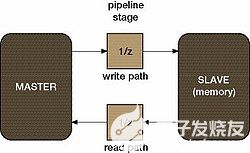

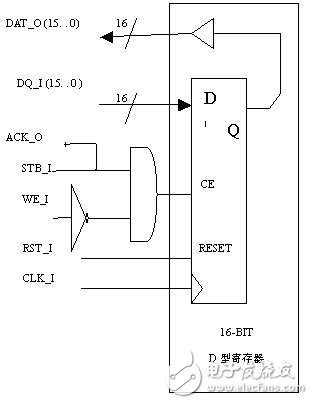

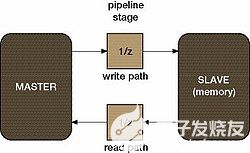

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示

2018-07-31 09:11:30 4148

4148

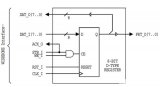

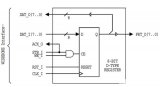

从设备是如何被选择的呢 '若系统中有M个从设备,则地址线被地址译码器分为M个部分,别代表每一个从设备的地址空间。从设备#Y对应的译码输出信号与共享总线上的STB_I信号相与,如果STB_I信号和从设备#Y对应的译码输出信号同时为高,从设备#Y才发起对主设备操作的响应。

2018-08-03 08:55:40 2981

2981

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

2018-08-05 08:44:59 3421

3421

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线,使用时钟上升沿驱图7 8-bit SLAVE输出端口动和采样信号。

2018-08-11 09:14:22 4391

4391

采用那些标准化、开放化的方案。目前,业界采用比较多的标准化、开放化的总线方案包括:IBM 公司的CoreCONnect、ARM的AMBA和Silicore公司的Wishbone。

2020-04-04 08:25:00 3694

3694

自PCI协议问世以来,PCI总线应用越来越广泛,现已成为事实上的计算机总线标准。随着PCI应用和开发的深入,往往需要在复杂的PCI系统中使用PCI桥来完成设计工作,包括使用主/PCI桥来完成整个系统的初始化配置过程。PCI桥的使用已从传统的PC机领域拓展到更多的电子应用系统中。

2020-04-21 09:47:27 1012

1012

用于便携式IP核的WISHBONE1片上系统(SoC)互连结构是一种灵活的设计方法,可用于半导体IP核。其目的是通过缓解片上系统集成问题来促进设计重用。这是通过在IP核之间创建一个公共接口来实现的。这提高了系统的可移植性和可靠性,并缩短了最终用户的上市时间。

2021-01-19 15:23:59 21

21 本文主要介绍和分析了在集成芯片设计中几种常用的片上系统总线-CoreConnect 总线、AMBA 总线、Wishbone 总线和 OCP 总线,通过比较这些总线的特性及适用范围,展望了它们的发展前景。

2021-03-28 11:02:58 16

16 ,传输信号快,接口简单,使用电缆线多)串行总线(多个信号复用少量信号线,电缆数量少,便于远距离传输,信号传输慢,接口复杂)按总线在微机系统的不同层次位置上分类:片内总线:IC内部,用于连接各功能单...

2021-12-17 18:29:11 1

1 数字接口(续)— SPI 总线

2022-11-07 08:07:31 0

0 Wishbone B.3总线。以类似的方式,Altera引入了自己的互连方案,称为Avalon Bus,SOPC Builder和Nios(II)系统就是围绕该方案制造的。Xilinx 还推出了自己的总线,称为片上外设总线与处理器本地总线 相结合。

2022-11-14 15:38:55 790

790

怎样把PCI总线速度锁定 PCI总线速度锁定是指限制PCI总线传输速度的方法。当系统中出现某些硬件兼容性问题或者不稳定性问题时,锁定PCI总线速度可能是一个有效的解决方案。在本文中,我们将详细介绍

2023-09-02 15:12:39 1194

1194 CAN总线的应用范围广,应用环境相当复杂,一些静电、浪涌等干扰很容易耦合到总线上,并直接作用于CAN总线接口。为了满足一些高等级EMC的要求,有必要添加额外的外围保护电路。CAN接口保护电路CAN

2023-09-23 08:29:45 580

580

LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484

电子发烧友App

电子发烧友App

评论