对降低地址总线功耗的编码方法研究与应用正在逐渐增多。本文在简述地址总线上的功耗来源的基础上,介绍了几种典型的地址总线低功耗编码方法,通过结合实际采用的T0编码,能有效地降低智能卡芯片的功耗。

CMOS电路中的功耗来源于两部分:一部分为静态功耗,由漏电和其它静态电流产生;另一部分为动态功耗,由短路电流和负载电容充放电产生。这两部分中共有三种最主要的消耗:跳变损耗(switching loss)、短路损耗(short-circuit loss)、漏电损耗(leakage loss)。短路损耗这部分功耗占总功耗的10-15%,而跳变损耗引起的功耗则占到总功耗的70%~80%。N位地址总线的跳变功耗表达式为:

其中,N表示地址总线宽度,Cload表示平均每位地址线的负载,VDD为电源电压,α表示一个周期内平均电容充放电的次数,f是操作频率,α×f表示翻转率。

智能卡芯片内部的地址总线,要将RAM、ROM等模块相连接,负载比较重,而且地址总线一般走线也比较长,这无疑都将增大地址总线的负载电容。同时,CPU对存储器访问频繁,也增大了地址总线的翻转频率。因此,地址总线上消耗的功耗比较大。

低功耗地址编码方法

对地址总线进行低功耗设计主要是对其进行低功耗编码,方法有BI(Bus-Invert)和T0(Zero-Transition)、格雷码、WZE编码等。它对CPU送出的t时刻与t-1时刻N位地址总线进行比较,总线上变化的位数如果大于N/2,则将总线取反外送,否则就直接外送。地址接收端收到地址后是否取反根据INV信号线来确定。例如,地址总线为4位,t-1时刻为0000,t时刻为1111,那么将1111取反后送出去。

BI编码公式如下所示:

式中的b(t)是指t时刻的实际地址,B(t)是编码后的地址,H(t)是b(t)和b(t.1)相异的位数。

BI解码公式如下所示:

其中,J(t)为解码后的地址总线。

T0码通过增加一条冗余连线INC来通知地址的接收端总线上的地址是否连续。如果INC为高,表明总线上的地址是连续的,此时所有的地址总线保持不变,地址接收端自动将上一地址加1,作为当前的地址;如果INC为低,表明前后两次地址并非连续,此时总线将正常地传送地址码。

定义b(t)为CPU计算出来的t时刻总线数据(即编码前的数据),B(t)是t时刻已放到总线上的数据(即编码后的数据),Jt是解码器解码后的数据。则T0编码的编码公式为:

与T0编码相对应的解码公式为:

将BI和T0两种方法结合起来,就形成了BI-T0方法。一般而言,地址都是比较连续的,而数据总线则是比较随机的。BI编码主要用于数据总线,用于地址总线的时候,一般都带有缓存。T0编码具有低延迟和小面积的特性,地址连续的时候,能够很好地降低地址翻转次数。在地址连续的时候,使用T0编码;在地址不连续的时候,使用BI方法,这就形成了BI-T0编码。

格雷编码对于连续变化为主的地址总线也是比较有效的。例如,从7变为0,用二进制编码是由111变为000,要引起跳变3次,而用格雷码则是由100变为000,只变化一次。对连续数据变换,用格雷码更简单有效。

WZE(Working-Zone-Encoding)编码假设每个瞬间程序只访问总地址空间的某个工作区(Working-Zone)。地址总线上传递工作区的标志和基于工作区基址的地址偏移,该偏移量采用独热编码。WZE主要用于外部地址总线,在它基础上形成了PBE编码和扩展WZE编码。

T0编码的实现与应用

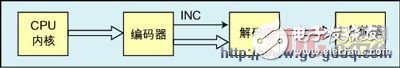

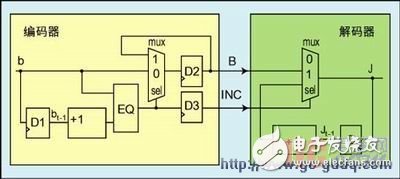

采用T0地址总线编码的示意图如图1所示,编解码器的结构如图2所示。b为CPU内核送出来的地址,B为经过编码器输出的地址,J为解码器送往存储器的地址,INC用来表示地址是否是连续的。编码器和解码器的电路规模很小,带来的额外硬件面积和功耗也很小。

图1:地址总线编码示意图。

图2:零翻转编解码器电路结构图。

我们选用一个测试激励,实际运行的波形图如图3所示。

图3:地址零翻转波形图。

从图中可以看到当CPU送出的地址总线是连续的时候,编码器和解码器之间的地址总线可以不翻转,存储器通过INC信号得到正确的地址。在FPGA仿真的时候,可以将上述激励的VCD文件输入XPOWER来分析功耗。使用T0编码,总功耗为0.467mW,不用T0编码,总功耗为0.999mW。

本文小结

结合一款8位智能卡芯片的实际情况,对地址总线采用简单有效的T0编码,有效地降低地址总线的翻转次数,从而有助于降低整个智能卡芯片的功耗。

电子发烧友App

电子发烧友App

评论