I2C总线协议

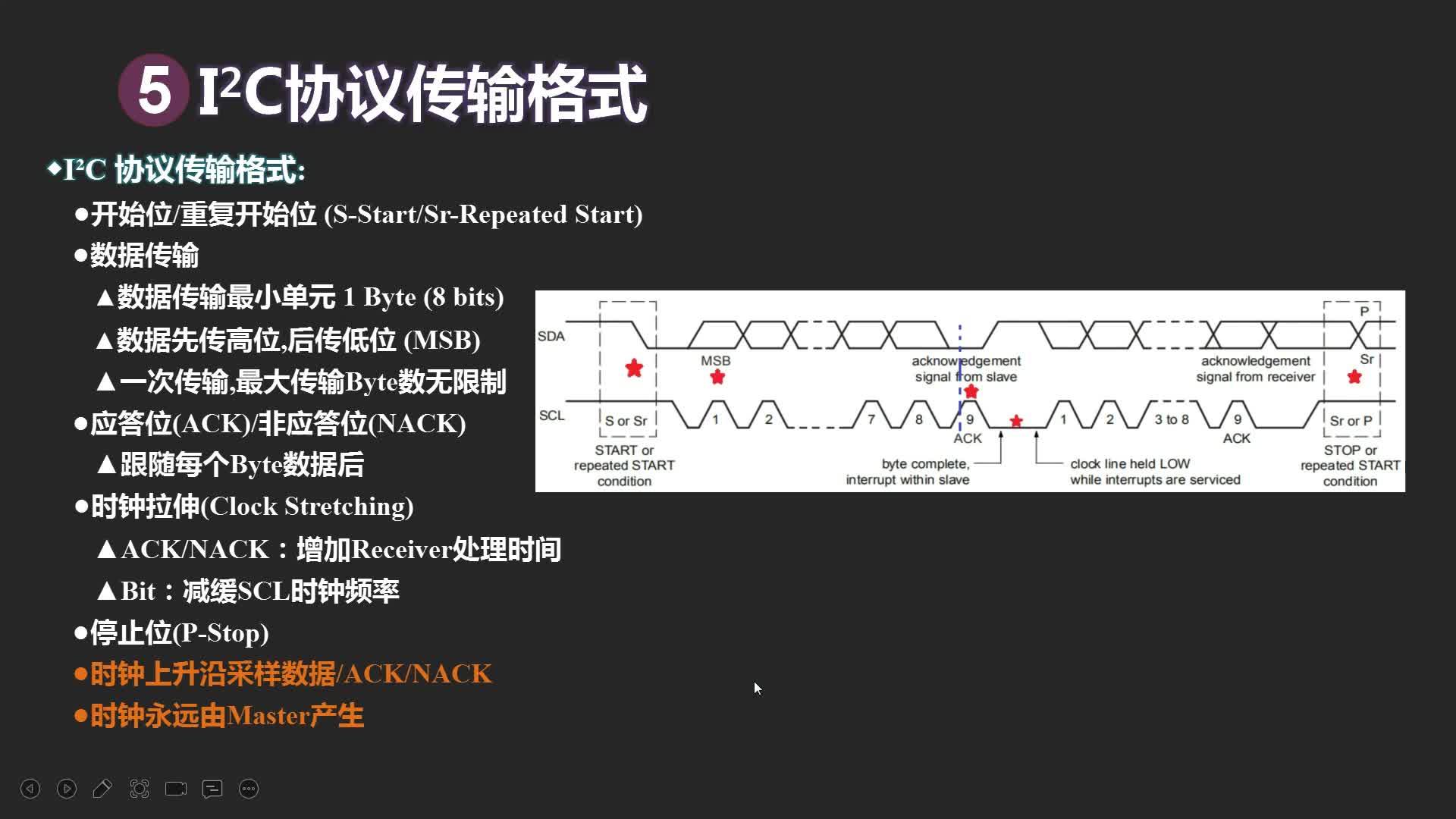

I2C协议规定,总线上数据的传输必须以一个起始信号作为开始条件,以一个结束信号作为传输的停止条件。起始和结束信号总是由主设备产生。总线在空闲状态时,SCL和SDA都保持着高电平,当SCL为高电平而SDA由高到低的跳变,表示产生一个起始条件;当SCL为高而SDA由低到高的跳变,表示产生一个停止条件。在起始条件产生后,总线处于忙状态,由本次数据传输的主从设备独占,其他I2C器件无法访问总线;而在停止条件产生后,本次数据传输的主从设备将释放总线,总线再次处于空闲状态。如图所示:

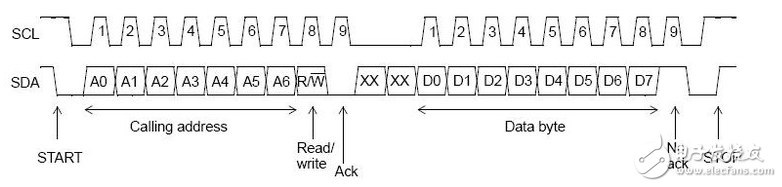

在了解起始条件和停止条件后,我们再来看看在这个过程中数据的传输是如何进行的。前面我们已经提到过,数据传输以字节为单位。主设备在SCL线上产生每个时钟脉冲的过程中将在SDA线上传输一个数据位,当一个字节按数据位从高位到低位的顺序传输完后,紧接着从设备将拉低SDA线,回传给主设备一个应答位,此时才认为一个字节真正的被传输完成。当然,并不是所有的字节传输都必须有一个应答位,比如:当从设备不能再接收主设备发送的数据时,从设备将回传一个否定应答位。数据传输的过程如图所示:

在前面我们还提到过,I2C总线上的每一个设备都对应一个唯一的地址,主从设备之间的数据传输是建立在地址的基础上,也就是说,主设备在传输有效数据之前要先指定从设备的地址,地址指定的过程和上面数据传输的过程一样,只不过大多数从设备的地址是7位的,然后协议规定再给地址添加一个最低位用来表示接下来数据传输的方向,0表示主设备向从设备写数据,1表示主设备向从设备读数据。如图所示:

I2C协议

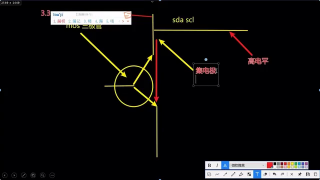

2条双向串行线,一条数据线SDA,一条时钟线SCL。

SDA传输数据是大端传输,每次传输8bit,即一字节。

支持多主控(multimastering),任何时间点只能有一个主控。

总线上每个设备都有自己的一个addr,共7个bit,广播地址全0.

系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份,细节视芯片而定,看datasheet。

1.1 I2C位传输

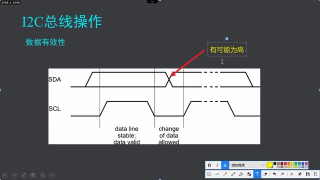

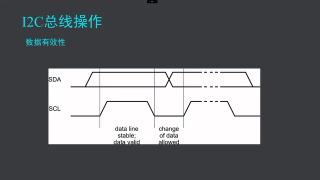

数据传输:SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据bit;若SDA发生跳变,则用来表示一个会话的开始或结束(后面讲)

数据改变:SCL为低电平时,SDA线才能改变传输的bit

1.2 I2C开始和结束信号

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

1.3 I2C应答信号

Master每发送完8bit数据后等待Slave的ACK。

即在第9个clock,若从IC发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程,如下所示:

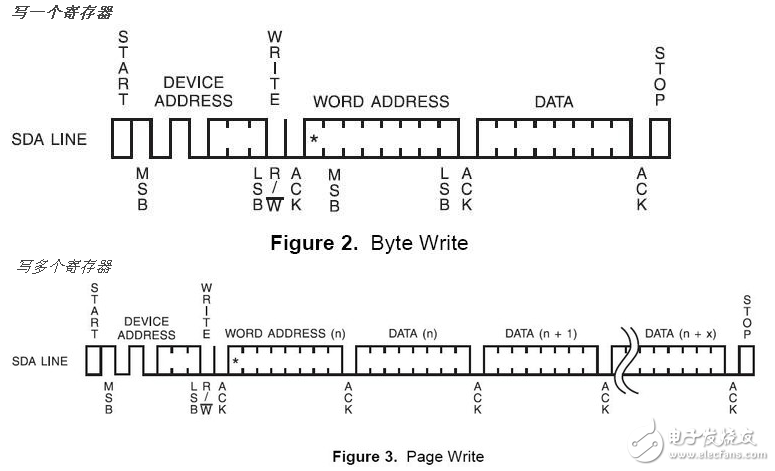

1.4 I2C写流程

写寄存器的标准流程为:

1. Master发起START

2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK

3. Slave发送ACK

4. Master发送reg addr(8bit),等待ACK

5. Slave发送ACK

6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK

7. Slave发送ACK

8. 第6步和第7步可以重复多次,即顺序写多个寄存器

9. Master发起STOP

1.5 I2C读流程

读寄存器的标准流程为:

1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK

2. Slave发送ACK

3. Master发送reg addr(8bit),等待ACK

4. Slave发送ACK

5. Master发起START

6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK

7. Slave发送ACK

8. Slave发送data(8bit),即寄存器里的值

9. Master发送ACK

10. 第8步和第9步可以重复多次,即顺序读多个寄存器

2. PowerPC的I2C实现

Mpc8560的CCSR中控制I2C的寄存器共有6个。

2.1 I2CADR 地址寄存器

CPU也可以是I2C的Slave,CPU的I2C地址有 I2CADR指定

2.2 I2CFDR 频率设置寄存器

The serial bit clock frequency of SCL is equal to the CCB clock divided by the divider.

用来设置I2C总线频率

2.3 I2CCR 控制寄存器

MEN: Module Enable. 置1时,I2C模块使能

MIEN:Module Interrupt Enable. 置1时,I2C中断使能。

MSTA:Master/slave mode. 1 Master mode,0 Slave mode.

当1-》0时,CPU发起STOP信号

当0-》1时,CPU发起START信号

MTX:Transmit/receive mode select.0 Receive mode,1 Transmit mode

TXAK:Transfer acknowledge. 置1时,CPU在9th clock发送ACK拉低SDA

RSTA:Repeat START. 置1时,CPU发送REPEAT START

BCST:置1,CPU接收广播信息(信息的slave addr为7个0)

I2C总线规范

对于面向8位的数字控制应用譬如那些要求用微控制器的要建立一些设计标准

• 一个完整的系统通常由至少一个微控制器和其他外围器件例如存储器和I/O扩展器组成

• 系统中不同器件的连接成本必须最小

• 执行控制功能的系统不要求高速的数据传输

• 总的效益由选择的器件和互连总线结构的种类决定

产生一个满足这些标准的系统需要一个串行的总线结构。尽管串行总线没有并行总线的数据吞吐能力但它们只要很少的配线和IC连接管脚,然而,总线不仅仅是互连的线还包含系统通讯的所有格式和过程串行总线的器件间通讯。必须有某种形式的协议避免所有混乱数据丢失和妨碍信息的可能性快速器件必须可以和慢速器件通讯系统必须不能基于所连接的器件。否则不可能进行修改或改进应当设计一个过程决定哪些器件何时可以控制总线。而且如果有不同时钟速度的器件连接到总线必须定义总线的时钟源所有这些标准都在I2C总线的规范中。

I2C总线的概念

I2C总线支持任何IC生产过程(NMOS、CMOS、双极性)两线。――串行数据SDA和串行时钟SCL线在连接到总线的器件间传递信息,每个器件都有一个唯一的地址识别无论是微控制器LCD驱动器存储器或键盘接口。而且都可以作为一个发送器或接收器,由器件的功能决定很明显LCD驱动器只是一个接收器而存储器则既可以接收又可以发送数据。除了发送器和接收器外器件在执行数据传输时也可以被看作是主机或从机(见表1)。主机是初始化总线的数据传输并产生允许传输的时钟信号的器件。此时,任何被寻址的器件都被认为是从机

表1 I2C总线术语的定义

电子发烧友App

电子发烧友App

评论