Altera的Cyclone V FPGA目前是业界系统总成本和功耗最低的FPGA,那我们该怎样为自己的设计选择Altera Cyclone V FPGA?参考本文...

2013-02-26 10:34:36 2469

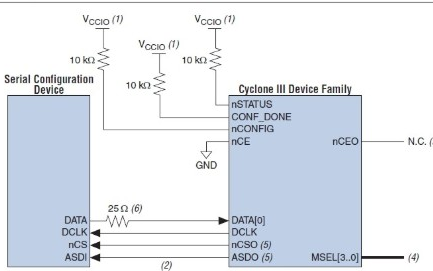

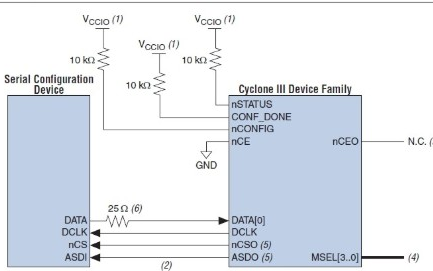

2469 CYCLONE IV FPGA 想用JTAG口编程FLASH,MSEL所在BANK被用于DDR,IO电压为1.8V,手册的配置方案表中AS模式的配置电压标准没有1.8V。是否可以理解成在JTAG方式

2019-03-21 10:24:44

Cyclone+IV+FPGA+器件系列概述

2012-08-18 00:11:05

;同时提供FPGA双机热备,高可靠性解决您的后顾之忧。2.硬件成熟 软件完备智明力强光电Cyclone V核心板基于ARM+FPGA单芯片解决方案,融合DDR3、NANDFLASH、EMMC等丰富的硬件

2017-09-19 14:30:54

Cyclone V SoC FPGA学习之路第二章:硬件篇(内部资源)前言上一章了解了《cycloneV device datasheet》,其中数据手册里重点介绍了电源要求,时序参数性能等。下面

2021-07-23 07:06:59

、振动、湿度实验,品质保障值得信赖;同时提供FPGA双机热备,高可靠性解决您的后顾之忧。2.硬件成熟 软件完备智明力强光电Cyclone V核心板基于ARM+FPGA单芯片解决方案,融合DDR3

2017-07-19 10:14:51

、振动、湿度实验,品质保障值得信赖;同时提供FPGA双机热备,高可靠性解决您的后顾之忧。2.硬件成熟 软件完备智明力强光电Cyclone V核心板基于ARM+FPGA单芯片解决方案,融合DDR3

2017-07-06 14:17:04

Altera 新的 Cyclone® IV 系列 FPGA 器件巩固了 Cyclone 系列在低成本、低功耗 FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在

2017-11-13 11:22:50

Cyclone® IV 器件具有嵌入式存储器结构,满足了 Altera® Cyclone IV 器件设计对片上存储器的需求。嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存储器模块进行配置,可以实现各种存储器功能,例如:RAM、移位寄存器、 ROM 以及FIFO 缓冲器。

2017-11-13 12:09:48

Cyclone IV 器件的 I/O 灵活性相应增加。改进了片上端接 (OCT) 的支持,另外真差分缓冲器也已消除了许多应用中所需的外部电阻,例如显示系统 接口。高速差分 I/O 标准在高速接口中已经很普遍,这是

2017-11-14 10:10:54

电子设备、通讯、系统控制、医疗和军事等领域所使用的关键应用中,要求能够做到以下两点:■ 确认存储在 FPGA 器件中的配置数据的准确性■ 使系统能够警惕配置错误的发生在 Cyclone IV 器件中使用 CRC 错误检测功能不会对布线及性能产生影响。

2017-11-14 10:49:16

本章节介绍了 Cyclone® IV 器件的存储器接口管脚的支持以及外部存储器接口的特性。除了大量供应的片上存储器,Cyclone IV 器件可以很容易地与各种外部存储器件建立连接,其中包括

2017-11-14 10:12:11

, 16-, and 64-Mbit flash memory devices that serially configure Stratix® II FPGAs and the Cyclone

2012-08-11 09:23:58

、低温、振动、湿度实验,品质保障值得信赖;同时提供FPGA双机热备,高可靠性解决您的后顾之忧。2.硬件成熟 软件完备智明力强光电Cyclone V核心板基于ARM+FPGA单芯片解决方案,融合DDR3

2017-07-18 10:28:53

DDR3的理论带宽怎么计算?用xilinx的控制器输入时钟200M。fpga与DDR的接口如下:

2016-02-17 18:17:40

为活动(已配置)状态。FPGA包括许多配置接口选项,通常包括并行NOR总线和串行外设接口(SPI)总线。支持这些总线的存储器在不同厂商的产品之间总是存在微小的不兼容性,增添了采购多款存储器件的困难程度

2021-09-03 07:00:00

大家:最近我在使用cyclone v e系列fpga完成ccd信号采集。这里altlvds_rx ip核比以前使用cyclone iv 多了rx_enable引脚(使用external PLL)。查看了handbook对这个信号不是很理解。希望有高手能指点一下这三个信号的时序关系。谢谢了

2017-07-04 11:47:31

cyclone v soc介绍资料!

2013-07-18 14:13:28

如SPI接口中,FPGA通过模拟产生时钟和串行数据与一个外部芯片进行通信,其建立和保持时间是有时序要求的,这个时序要求可以通过外部的手册上获得。那么在FPGA中模拟这个接口要如何保证这个时序要求呀

2023-04-23 11:35:02

在高清晰LCD HDTV 中使用Cyclone III FPGA引言当今的液晶显示(LCD) 技术在高清晰电视(HDTV) 领域得到了广泛应用,其挑战在于如何获得更高的分辨率,实现更快的数据速率

2008-10-16 15:44:08

。在2013年2月21日的新品发布暨媒体见面会上,Achronix率先发布具有里程碑意义的Speedster22i HD1000 FPGA芯片,凭借其强大的高带宽+联网性能,将大幅增强在有线通信、测试

2013-05-07 15:05:03

本人在做一个利用FPGA控制继电器控制的项目,选择cyclone II EP2C70F896I8N的FPGA,PCB,程序都一切正常,就使在FPGA启动过程中出现了问题,问题一是FPGA从

2020-07-06 19:45:55

`描述此参考设计提供为 Altera Cyclone V SoC FPGA 供电时所需的所有电源轨。此设计使用 LMZ3 系列模块产生用于为 FPGA 供电的电源轨。`

2015-05-11 16:49:30

易用开关稳压器和 LDO 的最优组合可提供最佳的电源分配树支持 DDR3 存储器件该设计已经过测试,可用于为 Cyclone V SoC 加电

2022-09-26 07:58:34

易用开关稳压器和 LDO 的最优组合可提供最佳的电源分配树支持 DDR3 存储器件该设计已经过测试,可用于为 Cyclone V SoC 加电

2018-09-06 09:07:37

了28-nm低功耗工艺技术进行开发,与前几代产品相比,Cyclone V功耗降低了40%。4、串联世界Cyclone V SOC核心板依托FPGA的丰富逻辑资源扩展出多种类型接口,呈现出灵活且可靠的多种适配

2017-09-29 10:53:26

开关稳压器和 LDO 的最优组合可提供最佳的电源分配树支持 DDR3 存储器件该设计已经过测试,可用于为 Cyclone V SoC 加电

2015-05-11 16:45:44

FLASH、EMMC、SD卡等),在每次上电时读取程序进行配置。2、功能分析项目中使用的FPGA型号是Altera公司(现属于Intel)的Cyclone系列。在Altera的文档[Cyclone

2021-12-27 07:32:47

器,到了Cyclone V系列的FPGA才支持DDR3存储器)。芯航线AC6102开发板作为一个高速应用型开发板,为了保证系统的存储带宽和容量,电路上设计了一组32位的DDR2存储器,接口时钟速率可达

2016-12-30 20:05:09

这是电子工程世界最近关于Cyclone V的答题活动结束了,楼主这里整理了所有答案,供大家参考。Q1.Altera Cyclone V GX开发板上的Cyclone V FPGA

2014-12-04 16:11:21

器,数字信号处理模块,高速收发器,高速IO管脚等,可以方便实现各种外围器件的配置和数字信号处理。.本文介绍采用cyclone V FPGA完成9361的配置,在 FPGA中通过SPI接口完成对 AD9361

2018-04-09 19:41:03

日前,Altera发布新系列Cyclone IV FPGA ,延续其收发器技术的领先优势。当前移动视频、语音和数据访问以及高质量3D图像对低成本带宽需求与日俱增,与此同时,终端产品市场,如智能电话等

2019-07-31 06:59:45

FPGA和HardCopy V ASIC针对高端通信应用进行了优化,并着重提供丰富的存储器,支持串行接口体系结构。 3 Cyclone V系列:低成本、低功耗不二选择 3.1 Cyclone V系列

2012-09-21 13:49:05

本帖最后由 ycq654263138 于 2012-9-6 16:50 编辑

分享快乐:Altera公司 Cyclone V 系列FPGA资料汇总(大家一起来接力上传

2012-09-06 16:37:58

12.8Gbps的带宽,如果DQ位宽变为32位,则理论带宽翻倍到25.6Gbps,这也是一个HMC所能达到的理论带宽的上限。部分CycloneV器件带有2个HMC,则整体的理论带宽上限值为51.2Gbps,已能够满足高带宽存储场合对FPGA和DDR3间接口带宽的要求。

2019-06-13 05:00:06

Cyclone III系列型号为EP3C16F484C6N的FPGA作为控制器,以Micron公司生产的型号为MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM为存储器。用一个IP核完成

2011-05-03 11:31:09

高性能系统设计师在满足关键时序余量的同时要力争获得更高性能,而存储器接口设计则是一项艰巨挑战。双倍数据速率SDRAM和4倍数据速率SDRAM都采用源同步接口来把数据和时钟(或选通脉冲)由发射器传送

2019-04-29 07:00:06

一、板级电路整体架构我接下来一段时间学习的就是“勇敢的芯”FPGA 实验平台,它是特权同学和至芯科技携手打造的一款基于Altera Cyclone IV FPGA 器件的入门级 FPGA 学习平台

2021-11-17 07:46:27

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

如何用低成本FPGA解决高速存储器接口挑战?

2021-04-29 06:59:22

大家好IAM设计一个使用CY7C68013A的应用程序,它必须支持高带宽同步传输。数据应该从CY7C68013A移出FPGA。我已经实现了设备描述符,主机识别CY7C68013A和加载驱动程序

2019-05-08 15:16:30

本文提出了基于SOPC(System On Programmable Chip)的设计方案[2],利 用其配置灵活、扩展性强、接口丰富等优点,以Altera 公司的Cyclone II 系列FPGA 为基 础,设计传感器节点数据采集存储系统,降低了设计的风险,完善了传感器节点功能要求。

2021-05-06 08:28:58

7nm工艺的Speedster 7t FPGA芯片根据未来硬件加速和网络加速的需求,在这三个方面都做了优化,消除了传统FPGA的瓶颈。下面我们重点说一说为了提高存储器带宽,Achronix通过采用硬核

2021-12-21 08:00:00

了28-nm低功耗工艺技术进行开发,与前几代产品相比,Cyclone V功耗降低了40%。4、串联世界Cyclone V SOC核心板依托FPGA的丰富逻辑资源扩展出多种类型接口,呈现出灵活且可靠的多种适配

2017-09-14 15:21:44

价格、厂家、技术参数、现货销售、长期供应、高价回收泰克TDS6604B高模拟带宽数字存储示波器收售供应热线:***/13728431276(同微)曾S供应QQ:3140751627(同微

2021-01-23 16:14:54

广东省食品药品职业技术学校 梁华英华南师范大学附属中学 高文强DDR SDRAM是Double Data Rate SDRAM的缩写,即双倍速率同步动态随机存储器。DDR内存是在SDRAM内存基础上

2019-05-31 05:00:05

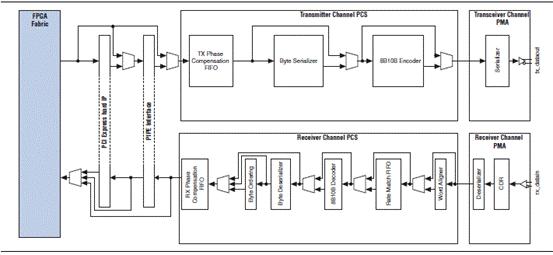

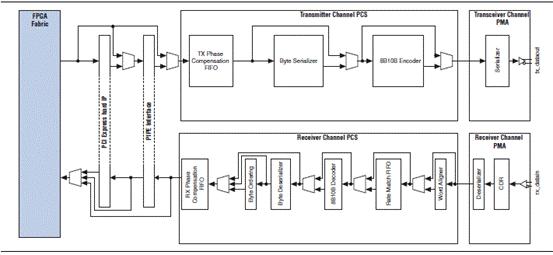

PCI Express是一种高性能互连协议,被广泛应用于网络适配、图形加速器、网络存储、大数据传输以及嵌入式系统等领域。文中介绍了PCIe的体系结构,以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

。Altera的收发器设计专长反映在高速串行接口的高可靠性和低功耗上。在早期功耗估算基准测试中,与Cyclone IV FPGA相比,Cyclone V FPGA展示出明显的低功耗优势(图1)。[/url]图

2015-02-09 15:02:06

作者:Xavier Ramus德州仪器 由于我们必须采用多个功率级,因而同时实现高增益(1000 V/V 或更高)和高带宽(数十 MHz)可能是一种挑战。除了高增益与高带宽的电路要求外,还需要重点

2018-09-20 15:06:01

作者: Xavier Ramus, TI由于我们必须采用多个功率级,因而同时实现高增益(1000 - V/V乃至更高)和高带宽(数十 MHz)可能是一种挑战。除了高增益、高带宽方面的电路要求,还需要

2018-09-21 15:18:42

基FPGA Cyclone II_EP2C5 EP2C8的频率计

基FPGA_Cyclone_II_EP2C5/EP2C8的频率计

功能描述:按4*4键盘上的1,2,3...号按键可依次测出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 脑机接口中基于VxWorks的ARM嵌入式系统

2009-03-29 12:27:20 15

15

介绍用FPGA 设计实现MIL-STD-1553B 总线接口中的曼彻斯特码编解码器。该设计采用VHDL 硬件描述语言编程,并用专门的综合工具Synplify 对设计进行综合、优化,在MAX+PLUSⅡ进行时序仿

2009-05-15 16:25:50 41

41 EP4CE10F17C8N,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA设备,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA设备,INTEL

2023-02-20 17:03:19

EP4CE6F17C8N ,Cyclone IV FPGA设备,INTEL/ALTERAEP4CE6F17C8N ,Cyclone IV FPGA设备,INTEL

2023-02-20 17:05:47

摘要:本文讨论了Cyclone系列器件的不同配置方法,提出一种单片机结合FLASH存储器的被动串行配置方案。关键词:FPGA;FLASH;PS;Cyclone

2010-08-13 12:04:09 64

64

摘要: 介绍用FPGA设计实现MIL-STD1553B部接口中的曼彻斯特码编解码器。该设计采用VHDL硬件描述语言编程,并且专门的综合工具Synplify对设计进行综合、优化,在MA

2011-04-19 21:38:56 1432

1432

Altera新Cyclone IV FPGA拓展了Cyclone FPGA系列

Altera拓展其成功的Cyclone FPGA系列并延续其收发器技术领先优势,于今天发布Cyclone IV FPGA新系列。在移动视频

2009-11-04 08:46:38 1221

1221 低功耗Cyclone IV FPGA

Altera公司宣布,开始批量发售Cyclone IV FPGA。公司还宣布开始提供基于Cyclone IV GX的收发器入门开发套件。Altera的Cyclone IV FPGA设计用于无线、固网、广播

2010-03-31 10:42:42 1431

1431 摘要:同步接口是光纤纵差保护装置的重要组成部分,本文介绍了Cyclone II FPGA 在光纤纵差保护同步接口中的应 用,详细地阐述了FPGA 实现光纤纵差保护同步通信接口的原理。大规模可编

2011-04-06 16:42:11 40

40 以Cyclone FPGA 器件为核心,设计数据交换机. 描述了Cyclone 器件中LVDS 接口、锁相环PLL 、片内M4KRAM模块、芯片配置的应用方法和技巧,给出了软件设计思路,并研制了数据下载线. 经实际测试和

2011-06-27 15:57:30 44

44 Cyclone 系列芯片是美国A ltera 公司推出的低价格、高容量现场可编程门阵列器件(FPGA ) , 本文概述了他的主要特点, 给出了其在与外部存储器接口时用到的双倍数据率输入输出接口的设计方

2011-06-27 16:27:41 45

45 以Cyclone FPGA 器件为核心,设计 数据交换机 . 描述了Cyclone 器件中LVDS 接口、锁相环PLL 、片内M4KRAM模块、芯片配置的应用方法和技巧,给出了软件设计思路,并研制了数据下载线. 经实际测试

2011-07-25 18:30:50 55

55 Altera 公司的Cyclone IV 系列 FPGA 包括两个系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元,高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供

2012-05-31 09:08:54 8725

8725

FLASH存储器接口电路图(Altera FPGA开发板)

2012-08-15 14:36:31 6269

6269

SoC FPGA使用宽带互联干线链接,在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括处理器、外设和存储器接口。Cyclone V SoC FPGA在一个基于ARM的用户可定制芯片系统(SoC)中集成了

2012-09-04 14:18:14 4604

4604

Altera的Cyclone V FPGA实现了业界最低的系统成本和功耗,其性能水平满足了您突出大批量应用优势的需求。从三种型号中进行选择: (1)只提供逻辑的Cyclone V E FPGA (2)具有3.125-Gbps收发

2012-09-04 14:34:07 13247

13247 Cyclone V FPGA功耗优势:采用低功耗28nm FPGA活的最低系统功耗(英文资料)

2012-09-05 16:04:11 40

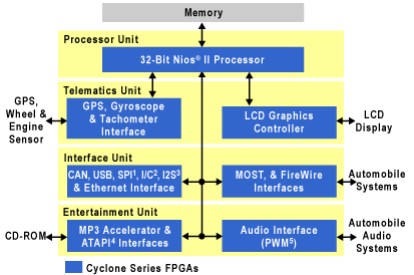

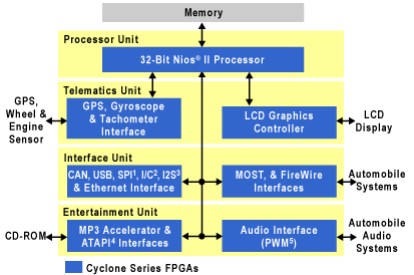

40 Altera的低成本Cyclone FPGA系列是远程信息处理系统中许多接口应用的理想选择。可编程逻辑允许对接口连接进行定制,从而满足多种不同数据类型的需要。它可以和预先设定的专用标准产品(ASSP

2013-01-23 16:24:42 1147

1147

白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

72 FPGA 设计人员在满足关键时序余量的同时力争实现更高性能,在这种情况下,存储器接口的设计是一个一向构成艰难而耗时的挑战。Xilinx FPGA 提供 I/O 模块和逻辑资源,从而使接口设计变

2013-03-14 15:16:07 71

71 Mouser Electronics正在备货Altera公司业界领先的28-nm Cyclone® V FPGA。 Cyclone V FPGA结合了高性能、业界最低的操作功耗以及系统成本,是工业、无线、有线、广播和汽车应用的理想选择。

2013-05-21 16:15:03 1102

1102 2013年11月25日 –贸泽电子(Mouser Electronics)即日起开始供应最新的Terasic Technologies FPGA开发套件,支持Altera的Cyclone V片上系统

2013-11-26 11:11:02 1083

1083 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 Cyclone FPGA系列简介

2016-12-26 22:02:46 0

0 仿真并在硬件中进行验证。 本文介绍了接口设计的性能要求、设计难题以及 Xilinx 的解决方案,从使用 Spartan-3 系列 FPGA 的低成本实现到使用 Virtex-5 FPGA 的最高带宽

2017-11-24 16:21:46 876

876 于 Cyclone EP1C6240C8 FPGA的ADS2807接口程序,主要用来使用FPGA控制ADS2807的采集。 采用FPGA来模拟ADS2807的时序来实现控制功能。 提供采样频率控制、AD通道转换、采样数据缓存等功能。

2018-01-31 16:46:54 10

10 赛灵思公司(Xilinx)宣布,采用HBM和CCIX技术的新型16nm Virtex UltraScale+ FPGA的细节。该支持HBM的FPGA系列,拥有最高存储器带宽,相比DDR4 DIMM

2018-07-31 09:00:00 2545

2545 Altera 新的Cyclone®IV 系列 FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

2018-11-19 08:35:00 9473

9473

来自OFC 2015的Xilinx Alliance成员演示,重点介绍了与Xilinx UltraScale FPGA接口的MoSys带宽引擎2高速串行存储器IC。

2018-11-29 06:37:00 2846

2846 Altera 新的Cyclone® IV 系列 FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

2018-11-22 08:00:00 46

46 继非常成功的第一代Cyclone®设备系列之后,Altera®Cyclone II FPGA将低成本的FPGA密度范围扩展到68416个逻辑元件(LES),并提供多达622个可用I/O管脚和多达

2019-03-25 08:00:00 14

14 很多人第一次接触Altera Cyclone系列FPGA的时候,可能会被其复杂的专用管脚给搞混淆,在这里我们Altera Cyclone系列FPGA的专用管脚一一列出供您参考,希望对您的设计有帮助。

2020-01-26 17:50:00 9729

9729

本文档的主要内容详细介绍的是Altera Cyclone III系列FPGA开发板的库文件免费下载。

2021-03-07 08:00:00 17

17 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 Flash存储器在单片机接口中的应用综述

2021-06-29 10:26:16 27

27 电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

2023-09-13 09:56:49 0

0

电子发烧友App

电子发烧友App

评论