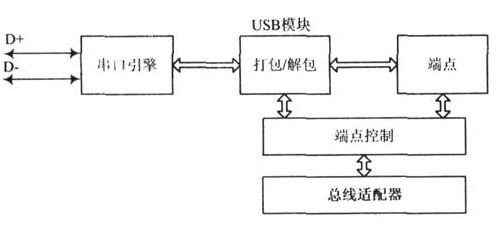

介绍了一款可配置的USB IP核设计,重点描述USB IP核的结构划分,详细阐述了各模块的设计思想。为了提高USB lP的可重用性,本USB IP核设计了总线适配器,经

2010-07-17 10:39:51 2389

2389

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 编辑

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改

2011-07-06 14:15:52

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

你好,我在使用Xilinx网站的IP核时遇到了一些问题。我已经下载了Vivado Webpack,也为此同时下载了IP-Core的许可证。Vivado Webpack工作正常,但我看不到我下载

2018-12-24 13:50:01

USB OTG的工作原理是什么?IP设计原理是什么?如何进行IP模块设计?USB OTG IP核有什么特性?如何对USB OTG IP核进行FPGA验证?

2021-04-27 06:44:33

这两种数据传输方式。相应的测试结果为:USB 2. 0 接口电路功能正确,在高速,全速和挂起状态下的功耗(包括收发器以及其他的辅助模块EPP , SDRAM 等) 分别为:584 ,254 ,102 mw

2019-04-12 07:00:12

管理,具有高带宽、高性能特性,适合于嵌入式处理器与高性能外围设备、片内存储器及接口功能单元的连接。 根据两种总线的特点和广泛支持,为了给嵌入式SoC系统提供USB接口,需要设计USB和AHB间的桥接IP核

2019-05-13 07:00:04

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

我想问一下,在quartus上直接调用IP核和在qsys中用IP核有什么区别?自个有点迷糊了

2017-08-07 10:09:03

我调用了一个ip核 在下载到芯片中 有一个time-limited的问题 在完成ip核破解之后 还是无法解决 但是我在Google上的找到一个解决方法就是把ip核生成的v文件加到主项目文件中就是上面

2016-05-17 10:28:47

Actel公司宣布Barco Silex专为Actel ProASIC3 FPGA而开发的BA511 ARINC 429 IP核已在多个安全关键性航空电子应用中通过DO-254认证。 配有

2019-07-26 07:14:05

用Quartus II 调用IP核时,在哪可以查看IP核的例程

2014-07-27 20:28:04

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

划分为几个主要模块,分别介绍各个模块的功能,用VHDL语言对其进行描述,用FPGA实现并通过了仿真验证。该IP核具有良好的移植性,可驱动不同规模的LCD电路。 关键词:LCD;驱动电路;IP 引言

2012-08-12 12:28:42

使用LabVIEW FPGA模块中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一个输入。我参考网上VHDL CORDIC IP核,说是将XY合并了,高位X低位Y。不知道在LabVIEW中如何将两个值X、Y合并成一个(X、Y均为定点数)。具体情况如下图:

2019-09-10 20:07:07

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI4

2019-12-13 17:10:42

大家好,有没有谁比较熟悉ALTERA公司的VIP系列ip核,我们用该系列IP核中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

2015-04-13 14:12:18

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

核 这里简单举一个乘法器的IP核使用实例,使用Verilog调用。首先新建工程,新建demo.v顶层模块。一、添加IP核 1. 点击Flow Navigator中的IP Catalog。2. 选择

2018-05-15 12:05:13

我写了一个缓存模块,里面包含有一个BlockRAM的IP核,现在想把这个缓存模块封装成我的一个自定义ip,但是封装完成之后仿真的时候会报错 ,我的步骤是这样的:1.写一个.v文件,里面是我的缓存控制

2018-12-11 10:25:41

本文介绍一款USB OTG IP核的设计与实现,该设备控制器可作为IP核用于SoC系统中,完成与主机控制器的通信,并能与普通的USB从设备进行通信。

2021-04-29 06:47:00

随着电路规模不断扩大,以及竞争带来的上市时间的压力,越来越多的电路设计者开始利用设计良好的、经反复验证的电路功能模块来加快设计进程。这些电路功能模块被称为IP(Intellectual Property)核。

2019-11-04 07:40:53

ddr2_controller模块例化的接口。这里可以分为三大类,第一类为系统类接口,主要是一些系统或PLL的复位、时钟等接口;第二类为带“local_*”的接口,是DDR2 IP核与用户逻辑间的接口;第三类为带

2016-10-27 16:36:58

刚刚接触IP核做FFT,现在用的是FFTV9.0,已经建立了一个IP核,但是如何仿真呢?是用quartus自带软件,还是要用MATLAB?抑或其他?我用的自带软件,但是什么也没有出来。正确的办法应该怎样呢,谢谢指点。

2011-04-21 10:22:31

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,这意味着我应该将所有ISE IP核的verilog模块导入EDK。这是可能的,如果可能的话请发送相关文件。谢谢&问候,Madhu.B

2020-03-24 08:14:50

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

本文的应用背景为某一工业测控系统,该系统采用FPGA实现测量数据的采集和控制信号的输出,通过定制PCI接口IP实现一个32位目标设备的PCI总线接口转换。PCI核选用AlteraPCI编译器所包括

2018-12-04 10:35:21

引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口

2019-06-11 05:00:07

核的性能仿真。【关键词】:IP核;;Viterbi译码器;;增信删余【DOI】:CNKI:SUN:DZGS.0.2010-02-008【正文快照】:0引言卷积编码和V iterbi译码是一种高效的前向

2010-04-26 16:08:39

和TECHNOLOGY VIEW两种原理图,有利于关键路径的寻找和分析,它还提供了许多功能强大的属性参数,但同时也增加了软件使用的复杂性。 VHDL语言中例化的FPGA IP模块(PCI核,双端口RAM等

2019-04-17 07:00:06

基于 的XC3S1OOE FPGA的USB接口IP核模块设计和验证

2020-12-25 06:48:04

。由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是

2018-11-21 11:30:06

基于FPGA的FFT和IFFT IP核应用实例AT7_Xilinx开发板(USB3.0+LVDS)资料共享腾讯链接:https://share.weiyun.com/5GQyKKc百度网盘链接

2019-08-10 14:30:03

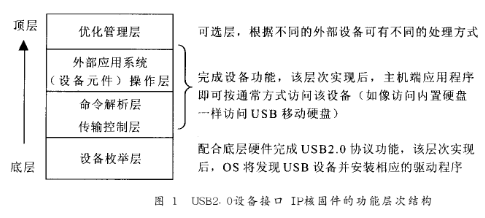

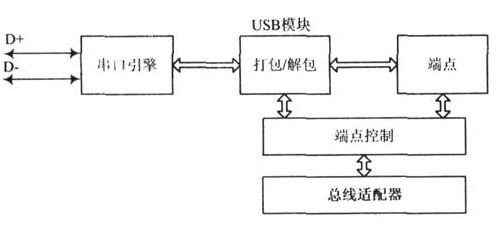

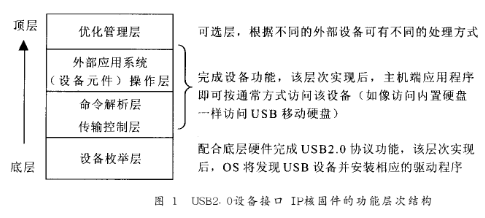

2.0协议外,还负责解释设备子类协议,并实现对具体外部应用系统(设备元件)的操作。 从硬件结构分析,基于增强型8051MCU核的 USB2.0设备接口芯片(IP核)应包括以下几个模块: (1)USB

2018-12-03 15:24:04

作为我项目的一部分,我需要将ADC与7系列FPGA接口,我有一个SelectIO™接口向导的IP核。但是,我的整个项目都在VHDL中,IPi得到的是Verilog。请指出我如何在我的VHDL顶级模块中使用该IP核的一些示例。最好的祝福

2020-05-21 12:31:59

你好, 我想实现一个带UTMI接口的Synopsis USB IP。像VC707这样的Xilinx电路板具有与外部USB收发器的ULPI接口。任何人都可以建议使用带有UTMI接口的Xilinx评估板。或者,如果有可用的USB UTMI到ULPI接口转换逻辑,我也可以使用它。专家友好的建议。问候,萨钦

2019-11-11 15:03:30

文章目录一、 项目介绍:写命令和写数据总线介绍写控制模块框图及波形代码(1)连续写(2)间隔部分测试代码一、 项目介绍:本章节将会讲解 A7 芯片内自带的 DDR3 SDRAM 的 IP 核的写时序

2022-02-08 07:08:01

HiI致力于研究在FPGA / Spartan 3E上连接打印机的研究项目。我可以获得打印机接口IP核,或者没有这样的核心。如果可能,请帮助我。感激地以上来自于谷歌翻译以下为原文HiI work

2019-07-04 06:32:58

on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点

2019-08-20 07:53:46

本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

2021-04-08 06:25:12

设计集成到单个芯片中即实现片上系统SoC。IP核的复用是SoC设计的关键,但困难在于缺乏IP核与系统的接口标准,因此,开发统一的IP核接口标准对提高IP核的复用意义重大。本文简单介绍IP核概念,然后从

2018-12-11 11:07:21

应用层。上层和下层通过确切定义的API连接的,HCI(主控制器接口)不仅定义了栈上层和下层之间的协议,而且也定义了诸如UART、RS-323和USB各种标准物理传输协议。这种模块化硬件与软件方案给SoC

2012-12-19 10:13:14

最近需要做一个调研,求问各位论坛的大神,各种接口IP:PCIE、USB3.0、serdes等等的价格区间是多少啊,硬核软核都可以,感谢不吝赐教

2020-01-20 17:59:06

经常看到各大招聘公司都会贴出有高速接口设计经验者优先,我想知道用了ddr、以太网的ip核,算是有高速接口设计经验了吗?

2017-07-16 16:47:18

核这里简单举一个乘法器的IP核使用实例,使用Verilog调用。首先新建工程,新建demo.v顶层模块。一、添加IP核1. 点击Flow Navigator中的IP Catalog。1.png

2018-05-16 11:42:55

如何实现基于IP模块的PCI接口设计?

2021-04-20 06:28:50

以SCI接口电路为例,介绍基于FPGA器件的接口电路IP核如何去设计?

2021-04-28 06:10:23

VIEW两种原理图,有利于关键路径的寻找和分析,它还提供了许多功能强大的属性参数,但同时也增加了软件使用的复杂性。VHDL语言中例化的FPGA IP模块(PCI核,双端口RAM等)应该不参与逻辑综合,可以在

2019-05-08 07:00:46

一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波

2019-06-03 05:00:05

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

这些IP的配置参数。用户还可以自己编写HDL代码模块作为用户自定义逻辑方便地添加到SOPC Builder中,设计流程如图1所示。图1 SOPC设计流程3.USB接口模块的添加 这里以常用的USB控制

2019-05-05 09:29:32

开放核协议—IP核在SoC设计中的接口技术

2019-05-27 09:52:01

控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。许多公司推荐使用现成的或经过

2019-04-12 07:00:09

基于USB接口的数据采集模块的设计与实现Design and Implementation of USB-Based Data Acquisition Module路 永 伸(天津科技大学电子信息与自动化学院,天津300222)摘要文中给出基于USB

2008-10-18 15:24:42 38

38 本文介绍了Tiger560B 处理器和w681511 音频编码器。并给出了USB 接口的IP 电话硬件设计与实现方法。关键词:USB;端点;编解码器Abstract:Tiger560B processor and w681511 codec is presented

2009-06-13 13:24:21 35

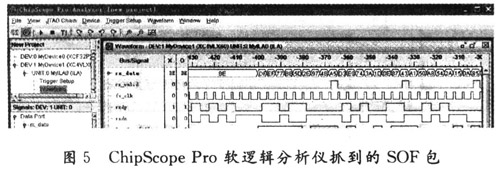

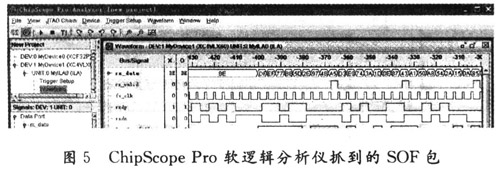

35 本文介绍一款USB 设备控制器IP CORE 的设计与实现。论文首先介绍了USB 设备控制器的设计原理,模块划分及每个模块的功能。然后介绍了该IP CORE 在ModelsimSE 中的功能仿真及FPGA 验证结

2009-08-06 11:39:00 8

8 USB设备接口IP核的设计:讨论了用Verilog硬件描述语言来实现USB设备接口IP核的方法,并进行了FPGA的验证。简要介绍USB系统的体系结构,重点描述USB设备接口IP核的结构划分和各模块的

2010-01-08 18:15:38 22

22 以AVR单片机ATmega8和USB接口器件PDIUSBD12为核心,基于标准的USB1.1协议,设计一种通用USB接口模块,以满足嵌入式系统中对USB接口的需求。对模块的硬件电路或单片机固件程序的硬件接

2010-12-16 15:30:59 139

139 USB2.0设备控制器IP核的AHB接口技术

介绍了USB2.0设备控制器IP核的AHB接口的设计。解决了双时钟域问题;实现了多事务DMA控制,减少了块传输的中断次数;

2009-03-29 15:14:15 1543

1543

USB2.0接口IP核的开发与设计

随着PC机和外围设备的发展,传统的并行接口和串行接口RS-232在易用性(即插即用) 和端口扩展等方面存在着一定的缺陷,这就使之越来越成为通信的

2009-04-22 16:34:43 1153

1153 HSD-20 USB接口微功率数传模块使用手册

2011-01-14 17:52:23 59

59 本内容提供了基于 USB接口 的指纹检测模块设计

2011-06-29 16:26:07 31

31 Wifi模块介绍:USB接口在wifi模块中充当什么角色?

实质上wifi模块上的数据传输有两端:一端是wifi芯片与wifi芯片之间,通过无线射频(RF)进行数据传输;另一端则是wifi芯片

2017-09-30 16:27:43 32

32 Wifi模块:USB接口对于wifi模块有什么作用?

在wifi模块中,USB充当什么角色呢?实质上wifi模块上的数据传输有两端:一端是wifi芯片与wifi芯片之间,通过无线射频(RF)进行数据传输;另一端则是wifi芯片与CPU之间,通过USB接口进行数据传输。

2017-10-17 15:42:13 29

29 、AP/Router 、UART WiFi模块和BLE4.0/4.2/5.0蓝牙模块。本篇SKYLAB的小编将为广大用户分析USB接口WiFi模块的选型参考方案。WiFi模块USB接口WiFi模块是高速

2018-11-22 16:39:31 1698

1698 *15*2.8(mm)应用:接USB摄像头、机顶盒、 游戏机、 打印机、 IP 摄像机 (2)USB接口WiFi模块WG211WG211是一款PHY速率达到433Mbps的高度集成双频(2.4/5G

2018-12-27 22:28:43 8343

8343 在信号层被编码成NRZI位信息后传送出去。数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

2019-01-11 15:31:25 2185

2185

在WiFi模块中,USB充当着一个重要的角色。WiFi模块上的数据传输有两端:一端是WiFi芯片与WiFi芯片之间,通过无线射频进行数据传输;另一端则是WiFi芯片与CPU之间,通过USB接口进行

2020-03-27 10:09:56 2050

2050 问题,是单频USB接口WiFi模块合适还是双频USB接口WiFi模块更好。SKYLAB WiFi模块选型表SKYLAB的WiFi模块根据支持频段分为2.4GHz单频WiFi模块、2.4/5GHz双频

2019-12-23 14:47:46 1286

1286 ,但国内对该领域的研究尚处于较初级的阶段。本文对USB IP核设计方法,提出了一种USB2.0设备接口IP核固件的实现方案,该方案采用合理定义的层次模型并已被实现,实验结果表明该方案具备良好稳定性和可扩展性的固件结构。

2020-04-04 10:48:00 1497

1497

IEEE802.11 USB接口双频WIFI模块产品下载

2021-04-24 10:50:23 14

14 MELSEC iQ-R EtherNet/IP网络接口模块用户手册(应用篇) 产品规格书

2022-08-26 10:09:40 1

1 目前wifi模块的用途是相当广泛了,USB接口WiFi模块的功能被应用各类电子产品生产制造中;通常WiFi模块系列电子元器件产品中,常用的通信接口就有USB接口WiFi模块,其中USB接口WiFi模块按照产品的功能特点多样,依照具体的功能需求是否需要,设计产品时的WiFi模块需求来确定。

2021-10-29 22:06:27 1109

1109

电子发烧友网站提供《基于NiosII的USB接口模块设计.doc》资料免费下载

2023-10-27 09:49:42 0

0

正在加载...

电子发烧友App

电子发烧友App

评论