。AXI4-Lite接口的特性如下: 1) 突发长度为1。 2) 所有访问数据的宽度和数据总线宽度相同。 3) 支持数据总线宽度为32位或64位。 4) 所有的访问相当于AWCACHE和ARCACHE

2020-09-27 11:33:02 8050

8050

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议

2020-12-23 15:32:37 2169

2169 开发基于总线的系统。 使用的板子是zc702。 AXI总线初识: AXI (Advanced eXtensible Interface),由ARM公司提出的一种总线协议。总线是一组传输通道, 是各种逻辑器件

2020-12-25 14:07:02 2957

2957

MPSoC有六个PL侧高性能(HP)AXI主接口连接到PS侧的FPD(PL-FPD AXI Masters),可以访问PS侧的所有从设备。这些高带宽的接口主要用于访问DDR内存。有四个HP AXI

2022-07-22 09:25:24 2501

2501 由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2022-08-02 12:42:17 6661

6661 IIC总线是一个双向的两线连续总线,它为集成电路之间提供通信线路。其意思是完成集成电路或功能单元之间信息交换的协议。

2023-07-23 11:45:50 5569

5569

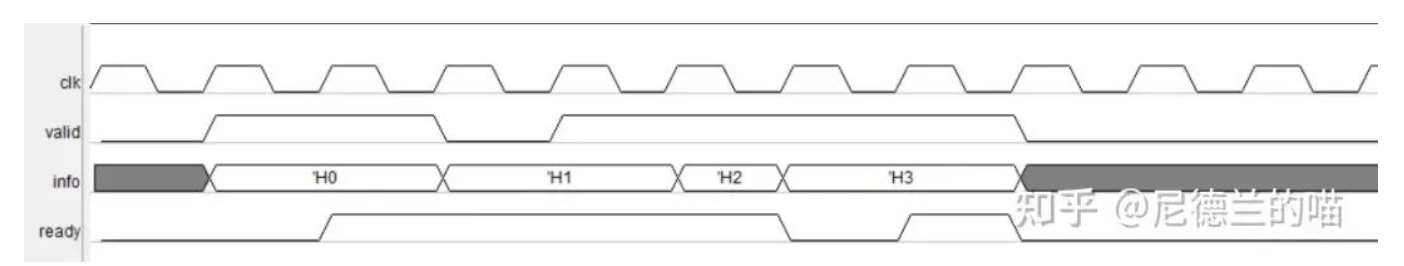

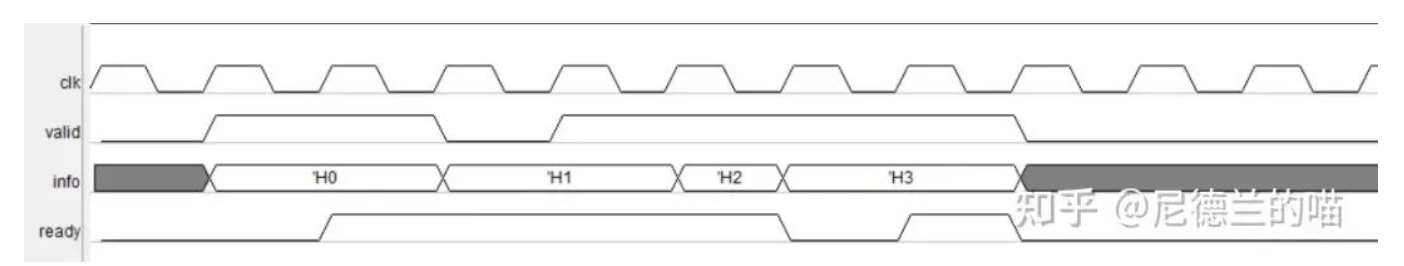

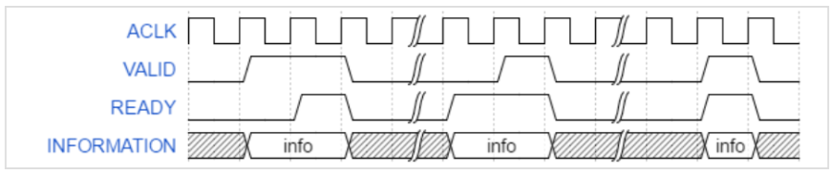

最早接触到握手协议是在校期间学习PCIe的AXI总线时,至今日虽然PCIe的结构已经忘得一干二净,但握手协议经过不断的使用还算掌握的不错。

2023-12-11 14:11:21 597

597

各位大侠, 谁有AXI总线的手册呀?如果有中文学习记录+手册就更完美了。谢谢先

2014-08-05 12:28:25

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。协议是传输数据的规则。

2021-02-05 07:30:05

AXI总线学习AXI协议的主要特征主要结构通道定义读写地址通道读数据通道写数据通道写操作回应信号接口和互联寄存器片基本传输Read burstOverlapping read burstWrite

2022-02-09 07:17:23

什么是AMBA?AMBA分为哪几种?AXI、AHB与APB的性能有什么不同?AHB总线是如何组成的?APB总线有哪些主要应用?

2021-06-18 06:55:01

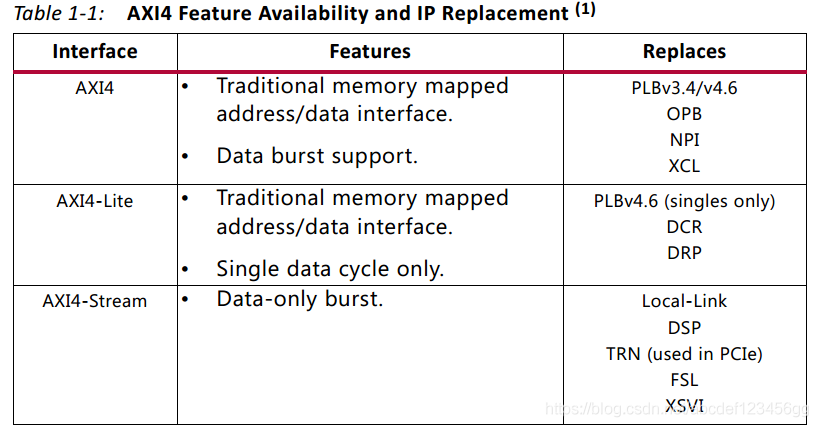

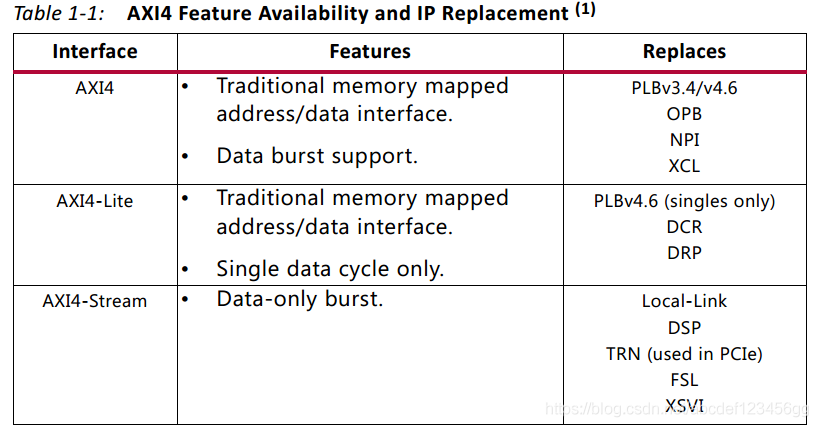

1、AXI接口协议详解 AXI 总线 上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线

2022-10-14 15:31:40

AXI 总线上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:AXI

2022-04-08 10:45:31

究竟哪一种总线将会主宰未来的测试测量领域呢?有哪几种较新的分立仪器总线技术?

2021-05-13 06:15:52

DMA内部寄存器的读写方式基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都

2022-10-14 15:23:41

市面上主流几种LED调光协议分析及具体应用场景介绍目前国内外的LED驱动已经不仅仅满足照明需求,更多是去追求各种不同场景的应用,搭配各种数字协议,实现某种特定的功能,比如在汽车大灯的应用中,未为兼容

2021-12-31 08:04:57

您可以将协议断言与任何旨在实现AMBA®4 AXI4的接口一起使用™, AXI4 Lite™, 或AXI4流™ 协议通过一系列断言根据协议检查测试接口的行为。

本指南介绍SystemVerilog

2023-08-10 06:39:57

AXI协议支持高性能、高频的系统设计,用于

管理器和下属组件。

AXI协议的特点是:

•适用于高带宽和低延迟设计。

•在不使用复杂桥梁的情况下提供高频操作。

•该协议满足各种组件的接口要求

2023-08-02 09:44:08

相干集线器接口(CHI)是AXI相干扩展(ACE)协议的演进。它是Arm提供的高级微控制器总线架构(AMBA)的一部分。AMBA是一个自由的可用的、全球采用的、开放的功能块连接和管理标准在片上系统

2023-08-02 13:40:23

本文介绍了AMBA3.0AXI的结构和特点,分析了新的AMBA3.0AXI协议相对于AMBA2.0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟设计。最后介绍了基于AXI协议的设计实例,探讨了利用IP复用技术和DesginWareIP搭建基于AXI协议的SOC系统。

2023-09-20 08:30:25

AMBA_AXI总线详解

2014-04-18 11:48:28

1、AXI协议用AxCACHE来控制事务属性来看看事务属性(Transaction Attributes),主要是对cache,buffer和memory controller的规定。按照协议,从机

2022-04-08 09:49:47

,AXI 这些。所以咱们花点时间,来好好研究一下这些总线协议都是什么。开始之前,先说一下,ACE 是 AXI Coherency Extensions 的缩写。顾名思义,ACE 就是 AXI 加上支持

2022-04-07 09:35:17

Arm AMBA协议集中,AXI协议是基于burst的吗?

2022-09-28 10:21:03

Arm AMBA协议集中,axi如何避免deadlock的,其它总线例如PCI是怎么避免的?

2022-10-20 11:07:56

文章目录I2c协议和时序I2c介绍I2c硬件连接I2c总线的信号I2c总线写时序I2c总线读时序I2c驱动框架I2C子系统软件框架常用的对象设备驱动对象i2c_client—挂在I2C总线上的I2C

2022-02-10 06:51:12

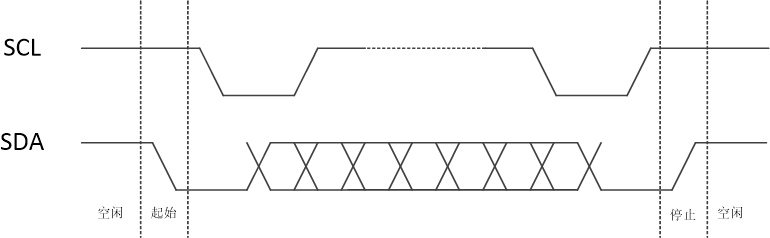

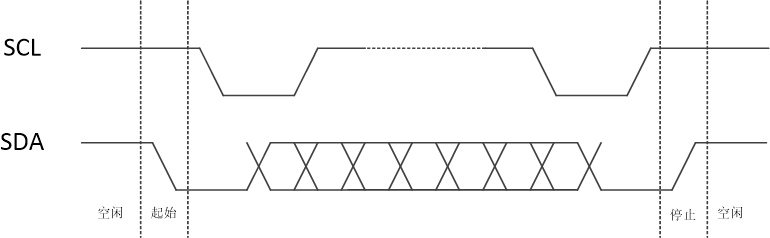

先简单介绍一下IIC总线协议。IIC总线是philips公司推出的新一代串行通信标准总线。它仅靠两根线实现全双工通信:SDA(数据线),SCL(时钟线)。 写时序如下

2016-08-07 12:43:01

SPI总线协议介绍

2012-08-18 21:26:58

SPI总线协议介绍(接口定义,传输时序)

2021-03-03 07:45:16

typora-copy-images-to: typora_picture基于FPGA与MCU通信的SPI协议设计1. SPI总线协议介绍及硬件设计1.1 SPI总线协议介绍及硬件设计SPI总线

2021-11-10 07:06:18

本帖最后由 何立立 于 2018-1-9 15:03 编辑

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

越来越多的芯片集成了这种通信协议。SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。 上升沿发送、下降沿

2018-07-06 07:24:25

一.单总线协议时序对应代码1.延时函数//单总线延时函数,约1~2usvoid Delay_OneWire(unsigned int t){static unsigned char i;while(t--){ for(i=0;i

2022-01-17 08:05:52

Arm AMBA协议集中,axi如何避免deadlock的,其它总线例如PCI是怎么避免的?求大神解答

2022-09-06 11:17:56

AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调试带来很多不必要的麻烦。为了解决这个问题,我们可以

2022-10-09 16:08:45

现在我要用block design搭建SOC,需要将总线转为AXI。按照论坛中的帖子,将e203_subsys_mems模块中的sirv_gnrl_icb2axi模块放到system层中,然后声明

2023-08-12 06:12:28

`1、在开发zynq工程时遇到多个axi_hp总线读写ddr时,总线锁死。现象就是axi_hp的wready信号一直为低。架构图: 2、应用write1、wrtie2、read1同时并行读写ddr3

2020-04-15 21:57:28

本指南介绍了高级微控制器总线体系结构(AMBA)AXI的主要功能。

该指南解释了帮助您实现AXI协议的关键概念和细节。

在本指南中,我们介绍:

•AMBA是什么。

•为什么AMBA在现代SoC设计中

2023-08-09 07:37:45

介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。3 AXI GP外设配置在zstar_ex53实例的基础上,需要对ZYNQ7Processing System(PS)配置页面做更改

2019-11-12 10:23:42

的逻辑设计。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。3Zynq PS的AXI HP配置在ZYNQ7 ProcessingSystem中,点击左侧Page

2019-11-26 09:47:20

不同通道使用情况下的数据吞吐量。大家可以在此基础上,更改不同的AXI HP总线时钟频率,以评估时钟频率对AXI HP总线的影响。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍

2019-11-28 10:11:38

`玩转Zynq连载3——AXI总线协议介绍1 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 1 AXI协议简介AMBA AXI(Advanced

2019-05-06 16:55:32

不做过多的讲解(小伙伴可以自行下载AMBA总线协议规范或者翻看网络上AXI4总线协议相关文章)。在SpinalHDL中,关于Axi4总线,包含了配置和实现两块内容,其内容均在

2022-08-02 14:28:46

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核实现基于AXI总线的双核嵌入式系统设计以及共享实现LED灯的时控.

2012-03-09 14:17:01 91

91 AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 详细介绍AXI总线

2017-02-28 21:03:54 1

1 AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 基于AXI4Stream总线协议,在Xilinx公司提供的FPGA上实现了一个具有缺陷像素校正、色彩滤波阵列插值、图像降噪实时图像采集与显示功能的视频系统。AXI4Stream总线协议由ARM公司

2017-11-17 08:58:01 4189

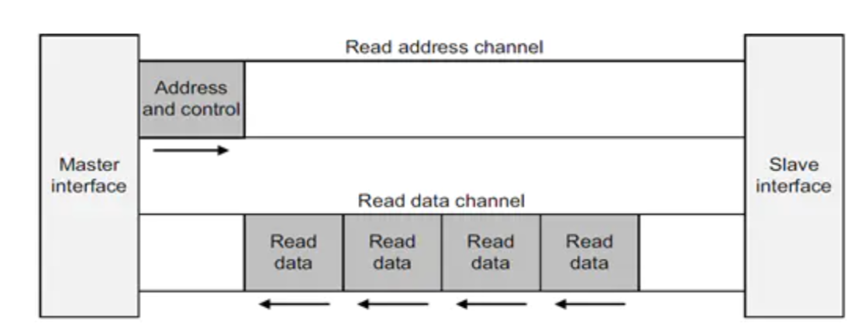

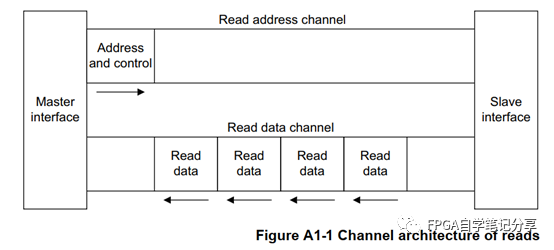

4189 1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 9601

9601

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

不同类型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 几种

2020-10-09 18:05:57 6391

6391

,进入等待触发状态。 图4‑56 等待触发 单击 SDK 中的运行按钮后, VIVADO 中 HW_ILA2 窗口采集到波形输出,可以看到 AXI 总线的工作时序。 SDK中 mian.c 程

2020-10-30 17:10:22 2040

2040

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2022-02-08 11:38:56 6550

6550

在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2021-02-04 06:00:15 10

10 在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2021-02-23 06:57:00 45

45 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 AMBA AXI 协议以高性能,高频系统设计为目标,提供了很多适合高速亚微型系统 互连的特征。

2021-03-28 09:47:04 23

23 本文介绍了AMBA3。0AXI的结构和特点,分析了新的AMBA3。0AXI协议相对于AMBA2。0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟设计。

2021-03-29 09:46:43 8

8 为实现片上系统不同P核之间的协议转换与高效通信,提出一种高效率PLB2AⅪI总线桥设计方案。利用PLB与AXI高性能总线的带宽优势,通过引入流水线传输和读写重叠传输机制,将PLB总线协议中的地址

2021-03-30 15:21:33 8

8 电子发烧友网为你提供SPI总线协议介绍(接口定义,传输时序)资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-01 08:45:43 24

24 AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 4970

4970

本文介绍了AMBA 3.0 AXI的结构和特点,分析了新的AMBA 3.0 AXI协议相对于AMBA 2. 0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟

2021-04-12 15:47:39 28

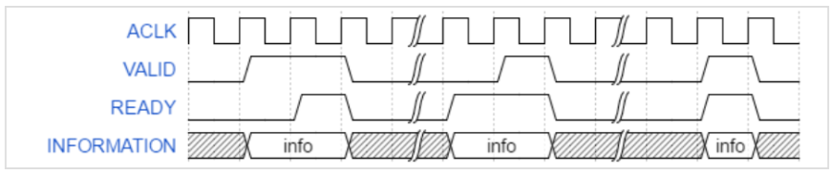

28 学习内容 学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4-Lite的相关信息,在文章后半部分对AXI读写时序进行了简要讲解,主要针对ARM公司

2021-04-30 11:22:13 2621

2621

:增加了AXI协议(了解);AMBA4.0:ACE协议(了解) 本文主要介绍AMBA2.0 (Advanced Microcontroller Bus Architecture,先进微控制总线结构),主要

2021-05-19 14:22:56 1835

1835

学习内容 学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4-Lite的相关信息,在文章后半部分对AXI读写时序进行了简要讲解,主要针对ARM公司

2021-06-01 10:57:38 2178

2178

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的区别就是AXI4-Stream去除了地址线,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时。由于AXI4-Stream协议(amba4_axi4_stream_v1_0_protocol_spec.pdf)没有时序图,

2022-06-23 10:08:47 1781

1781 本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 6846

6846 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 关于AXI总线协议的一些简单知识,通过阅读Xilinx的使用指导手册(UG1037),结合正点原子的ZYNQ视频进行梳理总结。

2022-07-15 09:16:29 2230

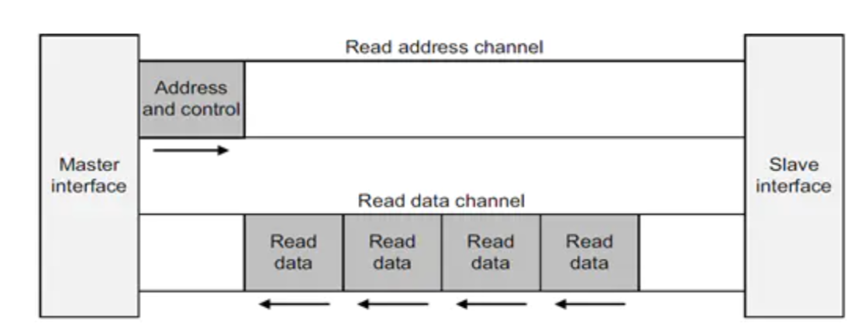

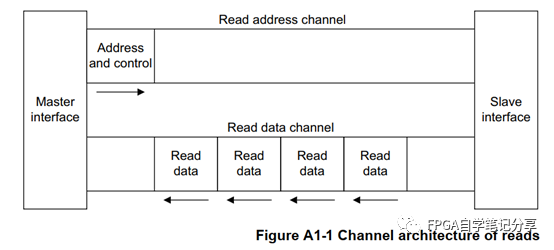

2230 本文主要介绍了AXI通道以及在每个通道下信号的概述。

2022-08-04 10:49:17 9635

9635 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能、高主频的系统设计的。AXI协议是被优化

2022-10-10 09:22:22 8632

8632 V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。

2023-04-14 10:54:54 2764

2764 AMBA AXI协议支持用于主从模块之间通信的高性能、高频率系统设计。

2023-05-04 14:35:14 1246

1246

之前文章为大家介绍了AXI的协议与架构,本篇我们接着往下讲AXI的读写传输

内容概括

2023-05-04 14:41:27 1423

1423

AXI 协议有几个关键特性,旨在改善数据传输和事务的带宽和延迟

2023-05-06 09:49:45 716

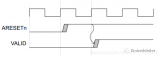

716 AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制

2023-05-08 11:37:50 700

700

AMBA AXI协议支持高性能、高频系统设计。

2023-05-24 15:05:12 688

688

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

2023-05-24 15:06:41 669

669

在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

2023-05-25 11:22:54 570

570

Arm® AMBA® 5 AXI 协议规范支持高性能、高频系统设计,用于管理器和从属组件之间的通信。AMBA AXI5 协议扩展了前几代规范,并增加了几个重要的性能和可扩展性功能,这些功能使这些协议与 Arm AMBA CHI 紧密结合。 让我们详细看一下 AXI5 协议的一些功能。

2023-05-25 16:01:21 1526

1526 AXI4协议是ARM的AMBA总线协议重要部分,ARM介绍AXI4总线协议是一种性能高,带宽高,延迟低的总线协议。

2023-06-19 11:17:42 2097

2097

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间**双向** **传输** ,且数据传输大小可以不同。

2023-06-21 15:26:43 1388

1388

可以看到,在AXI到UART中,是通过寄存器和FIFO进行中介的。因为从AXI总线往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1896

1896

LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484 LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

在介绍AXI之前,先简单说一下总线、 接口 以及协议的含义 总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般

2023-12-16 15:55:01 248

248 本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

2024-01-17 12:21:22 224

224

电子发烧友App

电子发烧友App

评论