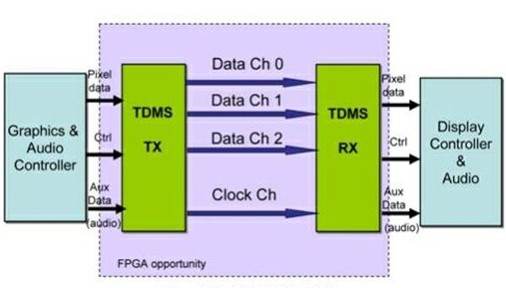

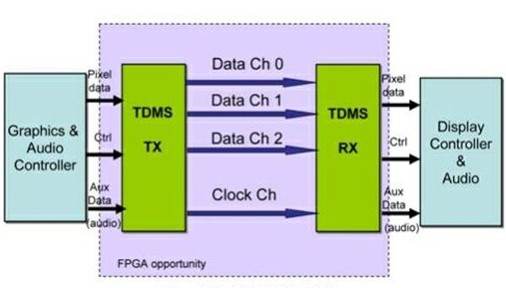

利用内置的SERDES和可以从莱迪思半导体公司得到的参考设计,ECP2M可以成功地实现接收和/或传送DVI/HDMI接口功能。通过使用FPGA技术和参考设计,设计人员能够很快地实现设计的其余部分,并无缝地连接到一个DVI/ HDMI接口,以满足他们自己的特殊要求。

2013-04-16 10:56:45 4625

4625

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2204

2204

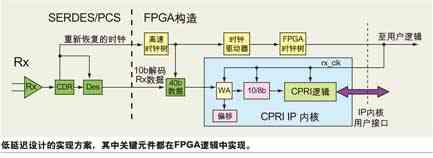

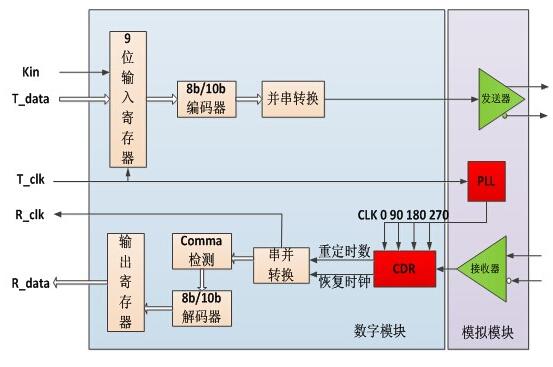

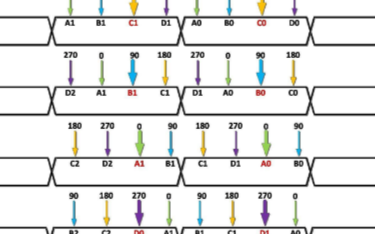

SERDES恢复出的数据进入FPGA有一个解复用和时钟域转换的问题,Stratix GX包含了专用电路可以完成8/10bit数据到8/10/20bit数据的Mux/Demux,另外SERDES收端到FPGA内部通用逻辑资源之间还有FIFO可以完成数据接口同步,其电路结构如图所示。

2018-04-08 08:46:50 9421

9421 GMII、SGMII和SerDes的区别和联系? GMII和SGMII区别,上一篇已经介绍了,这一篇重点介绍SGMII和SerDes区别。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29958

29958

及的底层输入-输出 PHY 技术是串行器-解串器 (SerDes) 技术。FPGA 作为一项技术从一开始就很复杂且具有挑战性,甚至在考虑高速接口之前也是如此。SerDes PHY 设计本身就很复杂且具有

2023-02-22 13:37:54 1151

1151 SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04:02 495

495

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

的设计者面临着一个不同以往的挑战:提供一个不仅能满足这些集成电路对互连带宽的要求,而且还能支持不同接口协议的可编程接口。解决方案是可编程硬件I/O模块。这些可编程硬件模块位于FPGA的I/O路径内。硬件模块

2018-11-26 11:17:24

本人刚入门FPGA,不知道如何实现FPGA+DSP,FPGA+ARM接口设计,网上查询有的说FPGA+DSP可以通过EMIF,IP核实现,FPGA+ARM可以通过SPI,有没有具体硬件参考的?

2016-08-27 11:30:26

后,将电路板上电运行。然后把下载电缆接到JTAG接口上,在主机中运行Quartus II软件,并打开Programmer编程器,单击其中的“Auto Detect”按钮进行FPGA下载链路自动检测。若能正确检测到FPGA,说明配置电路是正确连接的。

2012-08-12 11:52:54

,整板硬件包括FPGA电路, DDR3电路,外围接口电路,加上时钟和控制逻辑等辅助电路,形成一个完整的、一体化的数字系统硬件平台。能够快速接入FC-AE网络,实现光纤总线终端的数据通讯。课程提供项目

2021-11-17 23:12:06

类型也更多,而且内部还集成了一些特殊功能单元,包括: SERDES:高速串行接口。将来 PCI-E、XAUI、HT、S-ATA 等高速串行接口会越来越多。有了 SERDES 模块,FPGA 可以很

2020-09-08 22:43:16

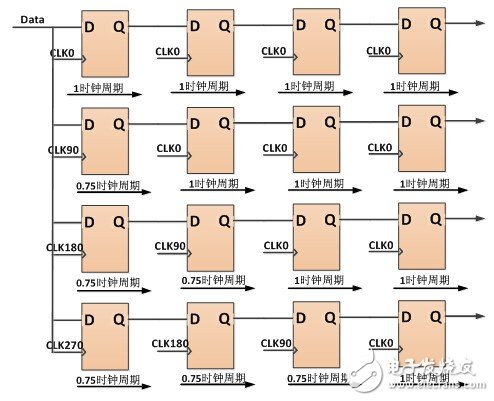

的时钟域中选择数据位,例如检测电路确定从时钟域A中采样的数据有效,那么将时钟域A中采样的数据通过输出端输出。 3 结束语: 通过对纯数字电路的CDR电路,在没有硬核的支持下,完成了FPGA上SERDES的接口设计,并通过实验的传输测试,在HR03的FPGA上,可完成100~200Mbps的数据传输。

2019-05-29 17:52:03

亲爱的Xilinx论坛,我正在实现基于SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另一个Kintex7串行化的64位字,主时钟为100MHz。将托管FPGA

2020-03-17 09:53:11

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

SerDes的发送端TX的均衡原理是什么?怎样利用高速接口SerDes去实现芯片间信号的有线传输?

2021-06-17 07:15:16

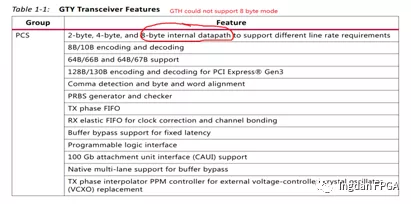

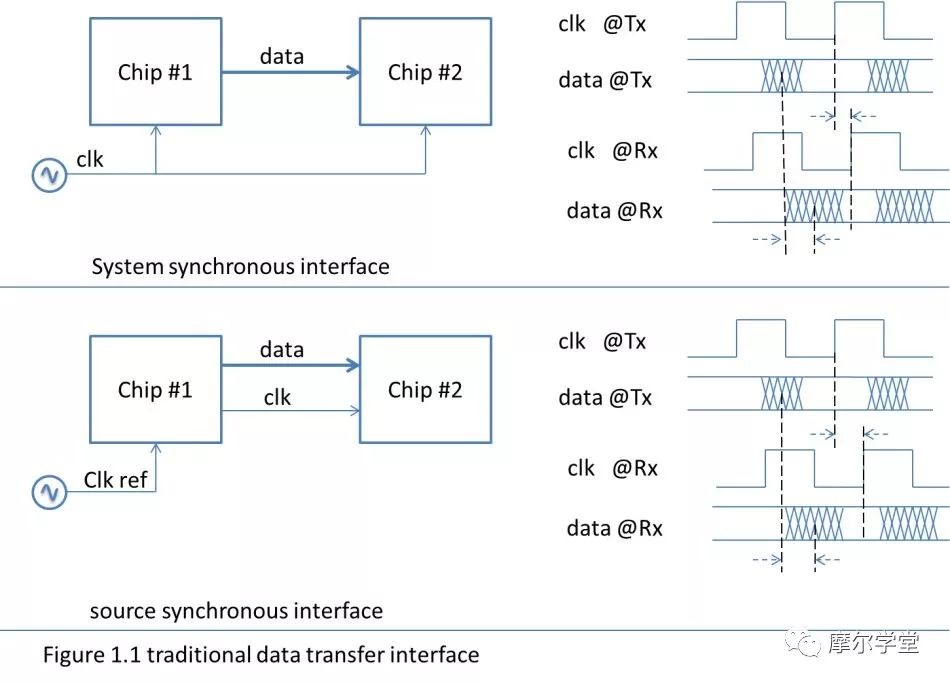

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35:42

我的印象是 Serdes 到 Serdes 10G 以太网连接是 T2080 上的一个功能选项。当尝试通过光纤或跨背板时,这会失败。memac 统计数据显示没有八位字节输出,状态寄存器指示 LI

2023-04-27 06:01:25

如题,9176DAC的PLL锁上了,证明时钟应该没问题,但是为什么DLL和serdes PLL锁不上呢?配置顺序,我是按照手册的START-UP SEQUENCE进行配置的。

2023-12-01 06:54:09

SerDes在93000平台上量产测试。本文将介绍Nautilus UDI方案是如何实现高速SerDes测试的,包括UDI结构,输入时钟设计,Load board设计,socket选型等多个测试环节。

2021-05-10 06:58:55

、MIPI接口的硬件设计注意事项。 本视频教程利用MiniStar开发板进行讲解,视频课程注重基础知识和设计思路的讲解,帮助刚接触高云FPGA的硬件工程师快速了解DDR3、HDMI、MIPI接口在硬件上的注意事项,也欢迎大家与我们交流在高云FPGA硬件设计上的问题。

2021-04-16 17:55:29

接口;能独立承担硬件FPGA设计项目,按照项目计划要求完成任务,能够独立进行FPGA需求分析、芯片评估、器件选型,并完成相关硬件系统设计,代码设计,仿真和调试;熟悉硬件设计流程,熟练应用Protel

2017-06-29 13:47:39

大家好, 在一个I / O块中有一个主serdes和一个slave serdes。如果我使用主设备,奴隶不能使用,是不是?谢谢。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

很好的应用笔记,用于在spartan fpgas中实现serdes但是对Virtex5没什么用?任何人都可以指出我使用V5 fpgas正确实现serdes(lvds)的一些资源。我将从主设备向10个从

2020-07-13 15:54:49

具有可重复的确定性延迟。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。此外,FPGA和ASIC中灵活的串行器/解串器(SERDES)设计正逐步

2018-10-16 06:02:44

CAUI电接口的转换。FPGA不仅有软件的可编程性和灵活性,同时又有ASIC高吞吐和低延时的特性。另外由于FPGA有高速SERDES等丰富的接口,而且能灵活控制实现的粒度和操作数据,因此在通信行业得到

2017-05-04 14:53:41

字信号处理、硬件数字滤波器、各种算法等,或者利用FPGA来扩展I/O接口,如实现多路PWM(脉宽调制)输出、实现PCI接口扩展等。通过合理的系统软硬件功能划分,结合优秀高效的FPGA设计,整个嵌入式

2019-05-06 09:18:16

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

如何在Serdes_0 (s32g274a) 上使用sgmii模式?

2023-05-09 07:41:26

我们在Artix-7上运行了一个1.0625 Gb / s链接进出Serdes。在接收方,如果我们拉光纤断开链路然后重新连接光纤,Serdes将不断指示rxbyterealign并且从不同步到输入

2020-08-21 11:05:45

总线的FPGA接口? FPGA必须插在服务器主板上吗?它可以与普通的服务器主板连接吗?我的问题是我只能在电路板底部表面的过孔处点击QPI信号,并需要某种连接器来连接FPGA。谢谢!

2020-03-13 10:05:34

HSDI接口的硬件结构以及接口信号的时序和功能操作基于FPGA实现HSDI接口的设计

2021-04-09 06:40:16

的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA一直支持千兆串行/解串(SERDES)收发器。然而在过去,大多数ADC

2021-04-06 09:46:23

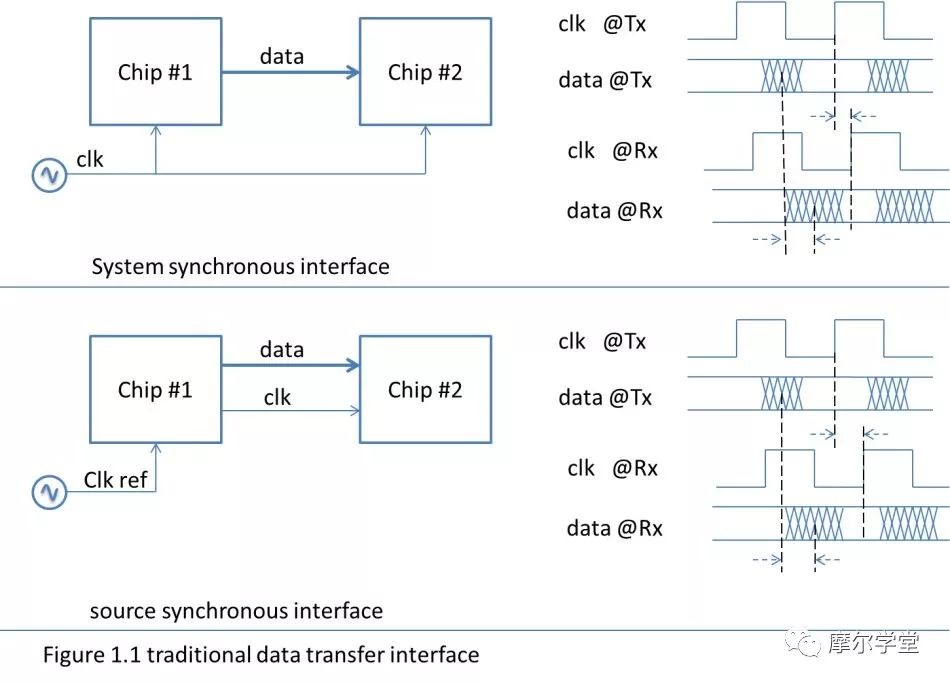

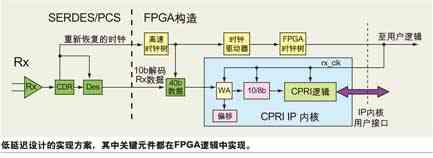

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

如果不使用FPGA自带的SERDES,可否适用LVDS接口实现其功能?

2023-05-08 17:37:48

SerDes的基本结构是由哪些部分组成的?怎样去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有传输时钟信号吗?

2021-10-18 08:53:42

新手接触fpga 硬件接口 求推荐好书

2013-04-01 21:09:25

SERDES的作用有哪些?SerDes的主要构成可以分为哪几部分?

2021-10-18 09:25:08

赛灵思 Artix-7 FPGA 是业界唯一的在低端器件上整合了高速收发器的方案,该方案提供了自适应均衡、2D 眼图以及IBIS-AMI仿真模型来简化针对成本敏感型应用的高速串行设计,观看视频,4分钟教您搞定高速SerDes端口设计。

2016-07-27 17:29:59

6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

2018-08-02 06:11:31

是整个温控系统的硬件基础,其中涉及到温度采集,与微处理器通信,串口输出,控制数模转换芯片等多个组成部分。本文提出一种高效实用的FPGA接口设计,它能够完成协调各个组成部分有序工作,准确、快速实现数据传输

2020-08-19 09:29:48

或者同时送两个接口。送往B口的数据包经过MAC帧格式拆封和B口格式封装后输出到转发模块,送往F口的数据经过数据宽度和时钟频率的变换后输出到协议FIFO。第二、线路接口卡上电初始化时,输入FPGA通过板级

2019-04-29 07:00:07

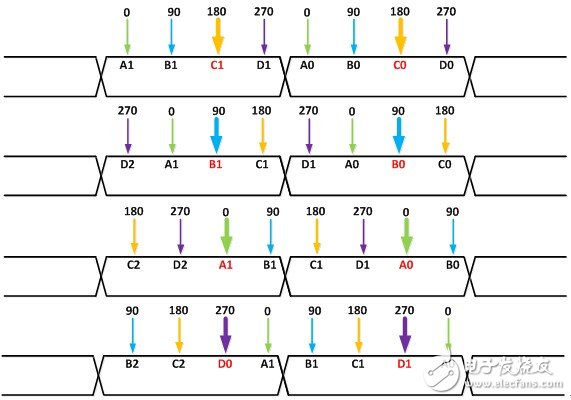

SERDES内的时钟和数据恢复(CDR)电路完成这个处理。CDR电路将每个串行的T M D S通道转换至10位,并将具有同步时钟的数据传送至FPGA接口,然后在FPGA中进行数据处理达到同步。这要求有

2019-06-06 05:00:34

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中

2020-10-28 17:15:14

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中

2020-11-01 20:21:02

Guide,能指导版图工程师进行电路版图设计;6. 具有深亚微米电路设计经验;7. 有良好的英语沟通能力,良好的团队合作。 Serdes PCS职位描述:1. 负责高速数字电路IP算法、协议、接口、控制

2017-11-13 14:46:14

SERDES结构是怎样构成的?高速SERDES接口在网络方面有哪些应用?

2021-04-28 07:19:38

概述EasyGo FPGA Solver是EasyGo开发的专门部署在FPGA 硬件上的解算器软件。根据不同的应用需求,会有不同的FPGA Solver 选择

2022-05-19 09:21:43

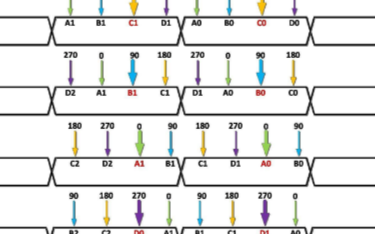

去偏移和包重组是在FPGA中实现SPI-4.2接口的核心难点,在分析偏移和包重组原理的基础上,给出基于FPGA的SPI-4.2接口的设计与实现方案,并对关键部分给出了硬件原理图,在线测试结

2009-04-10 09:43:35 32

32 当前的路由器或交换机产品都提供多端口千兆以太网接口。采用高性能FPGA 设计十端口千兆以太网接口, 阐述了系统平台的硬件设计及主要单元模块的功能,并对FPGA 内部程序设计的

2009-08-29 09:30:59 51

51 利用现场可编程门阵列FPGA 实现单片机的外设接口电路可以简化单片机系统的硬件电路,提高系统的集成度、可靠性和系统设计的灵活性。本文介绍了基于FPGA 的单片机外设接口电

2009-12-26 16:43:27 80

80 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 本文介绍了一种FPGA和IPX2805之间的SPI4.2接口模块设计的方法,对硬件设计进行了说明,着重阐述了FPGA内部SPI4.2接口模块设计。该设计简单、高效,解决了商用芯片不能满足高速转发的系

2010-07-28 16:56:32 33

33 本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信

2010-10-09 16:48:05 1165

1165

SERDES在数字系统中高效时钟设计方案,无论是在一个FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。

2012-02-16 11:23:43 5383

5383

电子发烧友网: 本文主要讲述的是 LatticeECP4 高速可配置SERDES。 LatticeECP4 FPGA系列结合了高性能 FPGA 结构、高性能I/O和多达16个通道的嵌入式SERDES,带有相关的物理编码子层(PCS)逻辑。每

2012-06-12 10:41:35 1439

1439

电子发烧友网: 本文主要介绍FPGA设计中功率计算的技巧。随着工艺技术的越来越前沿化, FPGA器件拥有更多的逻辑、存储器和特殊功能,如存储器接口、 DSP块和多种高速SERDES信道,这

2012-07-02 09:32:54 1638

1638 FPGA SERDES的应用需要考虑到板级硬件,SERDES参数和使用,应用协议等方面。由于这种复杂性,SERDES的调试工作对很多工程师来说是一个挑战。

2013-03-15 14:55:13 10359

10359

基于FPGA的SDI接口设计,學習FPGA的好資料!!!!

2016-06-06 10:00:46 29

29 随着更多的模数转换器(ADC)和数模转换器(DAC)支持最新的JESD204B串行接口标准,出现了FPGA与这些模拟产品的最佳接口方式问题。FPGA供应商多年来一直支持千兆串行/解串(SERDES

2017-11-18 01:48:02 1277

1277 。另外,用户还可以使用NI VeriStand,通过基于FPGA 的I/O接口创建用户自定义的I/O硬件。本文说明了使用基于FPGA I/O接口的益处,以及如何同NI VeriStand一起使用它们。

2017-11-18 07:47:35 8845

8845

这个文件包含执行指令(串行/ SERDES接口on the tms320c6474)基于DSP器件。包括串行RapidIO®(SRIO),天线,和串行千兆比特媒体独立接口(sgmii)接口。

2018-04-17 09:38:01 3

3 本文档的主要内容详细介绍的是FPGA教程之FPGA硬件最小系统设计的详细资料说明包括了:1.FPGA最小系统概念以及硬件系统的构成,2.FPGA主芯片电路设计,3.JTAG下载与调试接口,4.高速

2019-04-04 17:18:48 101

101 本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 4072

4072

随着通信技术的飞速发展,高速数据传输系统成为了当前研究的热点,而高速 SERDES 接口芯片的研究则是其中一个重要的组成部分。SERDES 接口芯片的主要功能是将低速的并行信号转换成为高速低压差分信号(LVDS)并通过串行链路发送,同时能够接收串行输入 LVDS 数据并正确的转换为低速并行信号。

2019-06-24 08:00:00 12

12 只要SERDES接口的高级架构是合理的,SERDES总线的成功实现就归结为“实现细节”。

2019-08-14 17:57:00 2615

2615 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

2020-05-18 10:51:18 2964

2964

总线而成为高速接口设计的主流。 如今,随着SerDes接口的广泛应用,许多高端的FPGA都内嵌有SerDes接口硬核。在FPGA中内嵌的SERDES的硬核,可以大大地扩张FPGA的数据吞吐量,节约功耗,提高性能,使FPGA在高速系统设计中扮演着日益重要的角色。 国产

2020-07-28 12:05:16 1128

1128 芯片功能的增加和数据吞吐量的要求, 促使芯片行业从较低数据率的并行连接, 转向较高速度的串行连接。SERDES(Serializer-Dese rializer ,) 是经高速差分对,而不是经较低

2020-10-09 17:25:07 18

18 因为摄像头输出的LVDS信号速率会达到600Mbps,我们将不能够通过FPGA的I/O接口直接去读取这么高速率的信号。因此,需要使用Xilinx FPGA内的SerDes去实现高速数据的串并转换。

2020-12-30 17:24:00 39

39 我在2015年底到2016年初的时候,使用7 Series FPGA Transceivers完成了TS流数据的传输,当时使用的传输速度为3.125G,SerDes选取的是8b/10b编码方式

2020-12-30 17:24:00 31

31 本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 25

25 偏移和包重组是在FPGA中实现SPI一4.2接口的核心难点,在分析偏移和包重组原理的基础E,给出基于FPGA的SPI一4.2接口的设计与实现方案,并对关键部分给出r硬件原理图,在线测试结果证明该方案可以实现SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 为了学习xilinx serdes 原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

2021-02-26 10:04:00 37

37 产品上市的速度。 如今,PCIe、HDMI以及USB这样的高速接口已变得不可或缺,但20年前的情况并不是这样,过去的20年中,串行接口应用数量经历了爆炸性的增长。 从上世纪九十年代末开始,SERDES二十年的革命之路。本文将通过一些底层技术的简单介绍,尝试解释下为什么串行接口(以SERDES为代表)

2021-07-23 11:21:19 3986

3986 SERDES的优势 引脚数量和通道优势 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。 对于现代的SERDES来说

2021-07-23 11:59:46 3794

3794 在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输

2022-08-02 11:28:14 4854

4854

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。

2022-10-31 11:28:41 1349

1349 SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

2023-01-03 16:23:35 626

626 FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-03-16 10:28:11 1915

1915

利用源同步接口,数据的有效窗口可以提高很多。通常频率都在1GHz以下。在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

2023-03-28 15:51:15 849

849 同时介绍一种采用光电集成技术的,即采用光SerDes而非电SerDes的高速收发器。

2023-04-01 09:28:58 1078

1078 首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4706

4706

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2023-07-27 16:10:01 1565

1565

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-10-16 14:50:37 558

558

尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44:59 449

449

电子发烧友App

电子发烧友App

评论