0 引言

近几十年来,集成电路事业发展迅速,设计与工艺技术不断发展,更多和更复杂的功能被集成到一块芯片上。SoC的集成度和复杂度大大提高,在IC设计中就容易引入错误,所以验证工作将变得艰巨。随着IC设计规模的增大以及设计周期的压缩,传统验证技术已经不能再满足日益增长的验证需求,验证方法学应运而生,目前,UVM验证方法学已经成为应用最广泛的方法学。

本文目的在于为数字基带处理单元中标签发送链路的编码模块搭建一个适当的、完善的验证平台,用来验证RTL代码的正确与否。运用面向对象思想的UVM验证方法学和C语言进行平台的设计与实现,它能有效地缩短验证周期,提高验证效率,加大芯片的面试可能性。

1 UVM验证方法学

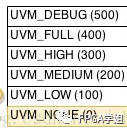

目前,主流的验证方法学有VMM、OVM和UVM。UVM基于System Verilog语言,具有VMM、OVM等诸多验证方法学的优点,是一套高效、开源的验证方法学。UVM由Accellera标准组织推出,并得到了三大主流EDA供应商支持。

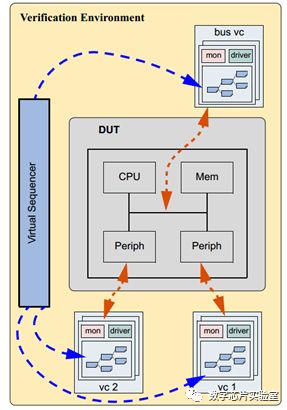

通用验证方法学(Universal Verification Methodology,UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,可以利用其可重用组件构建具有标准化层次结构和接口的功能验证环境。

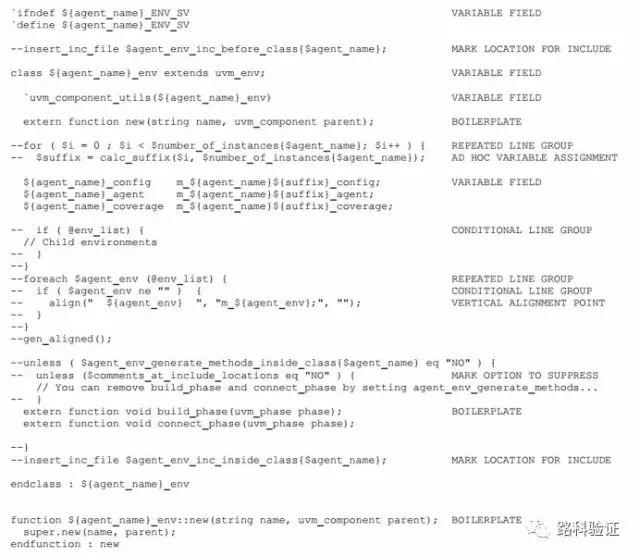

UVM平台架构主要是由通用验证组件(Universal Verification Component,UVC)构成。每个UVC都是功能完备、可配置、封装好的验证环境。根据UVC功能的不同,可分为接口UVC(Interface UVC)和模块UVC(Module UVC)等。

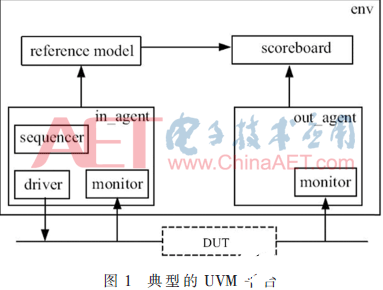

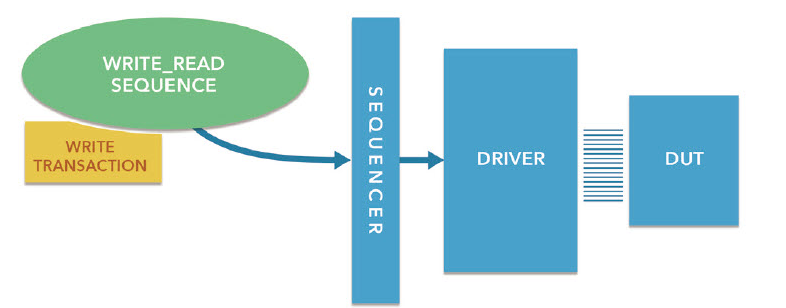

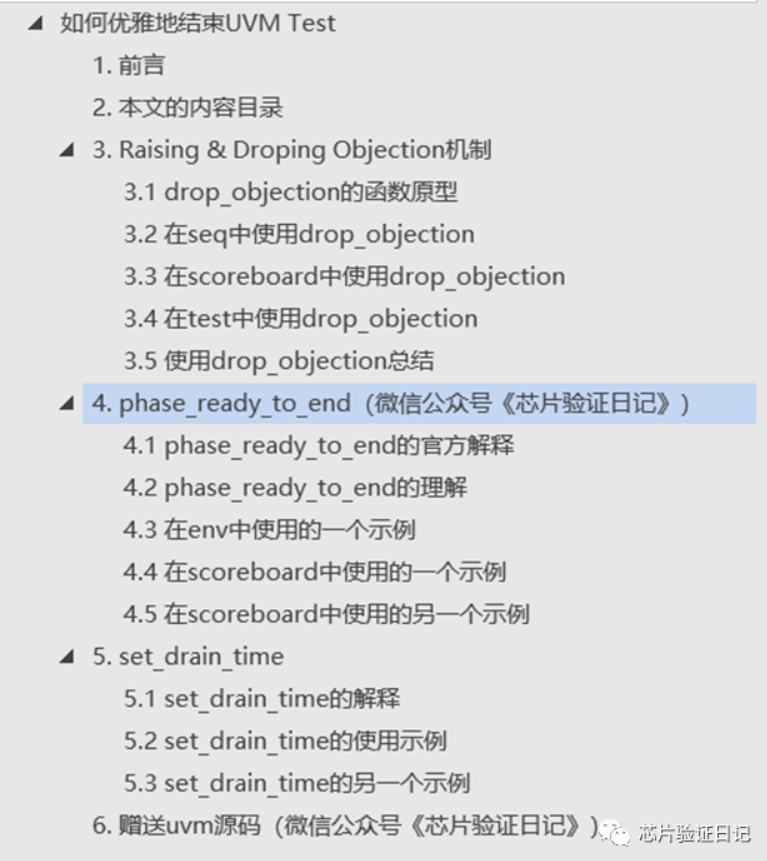

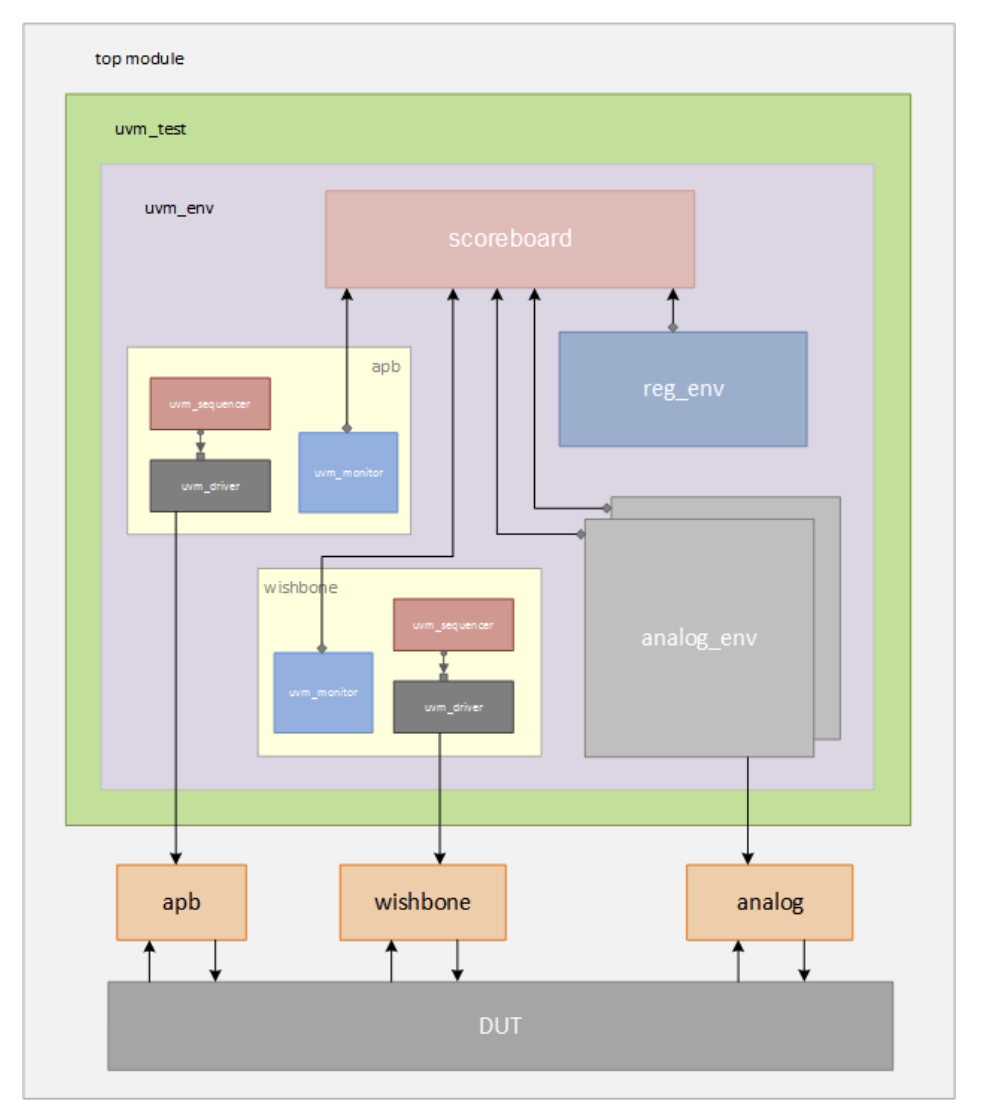

由图1可知构成UVM环境的常见组件类如下:

(1)uvm_driver类:是从uvm_sequencer中获取事务(transaction),经过转化在接口中对DUT进行时序激励。diver类与sequencer类之间的通信就是为了获取新的事务对象,这一操作通过pull方式实现:

driver.seq_item_port.connect(sequencer.seq_item_export);

driver.rsp_port.connect(sequencer.rsp_export);

(2)uvm_monitor类:用来监测数据。

(3)uvm_sequencer类:就像一个管道,从中传送连续的激励事务,并最终通过TLM端口送至driver一侧。

(4)uvm_agent类:用来封装一个driver、一个monitor和一个sequencer。

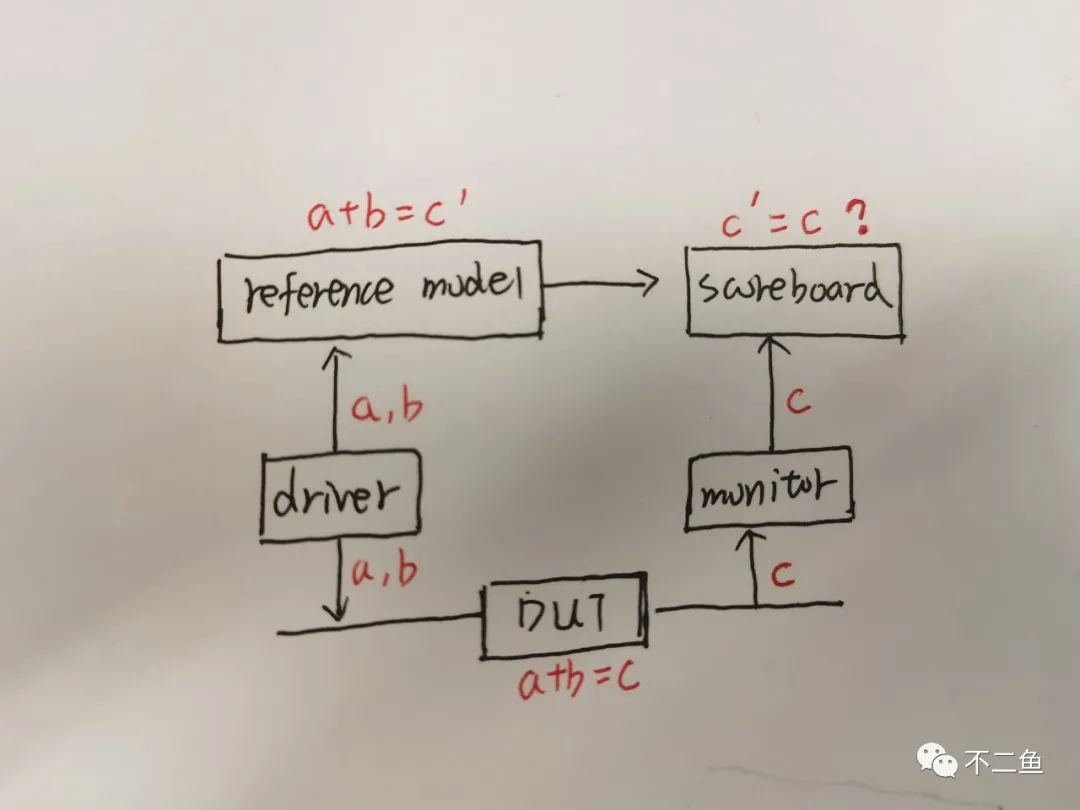

(5)reference_model:用于完成和DUT相同的功能。reference model的输出被scoreboard接收,用于和DUT的输出相比较。

(6)uvm_scoreboard:用来进行数据比对和报告。

(7)uvm_env:是一个结构化的容器,用来容纳各组件。

(8)uvm_test:是验证环境的唯一入口,只有通过它才能正常运转uvm的phase机制。

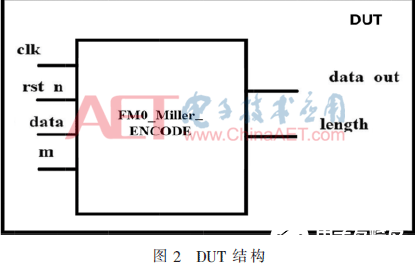

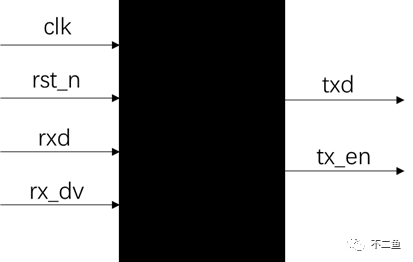

2 DUT介绍

图2中的DUT实现了FM0和Miller副载波调制编码。在ISO/IEC18000-6C协议标准中,标签发送链路主要采用是FM0编码和Miller编码。编码方式的选择由m[1:0]来决定,只有当m值为2′b00时才会选择FM0编码,m为2′b01、2′b10、2′b11时选择Miller编码。

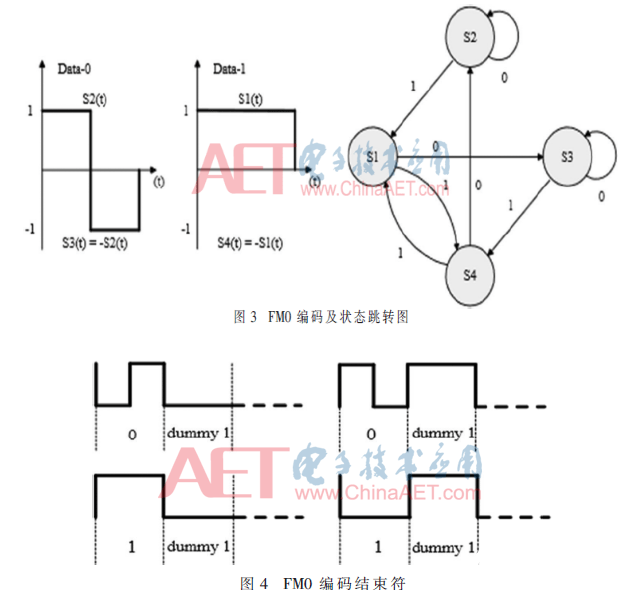

FM0编码是通过电平翻转的方式来实现编码,数据码元-0和-1翻转的次数不同。码元-0在码元周期中间会发生一次电平翻转,而码元-1只在每个码元起始处发生电平翻转。从图3所示FM0编码的状态跳转图可以看出FM0编码的码元-0和-1的波形,而且在FM0编码结束后需要在码元数据的尾端添加结束标志,结束标志会以固定码流来结束。码元波形和结束符如图4所示。

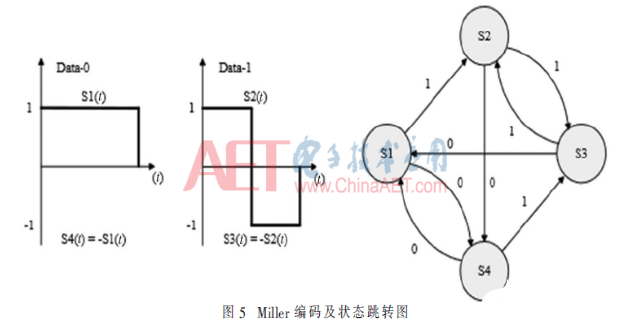

Miller编码又称为副载波调制编码,也是通过电平翻转的方式来实现编码。编码方式和状态跳转如图5所示。

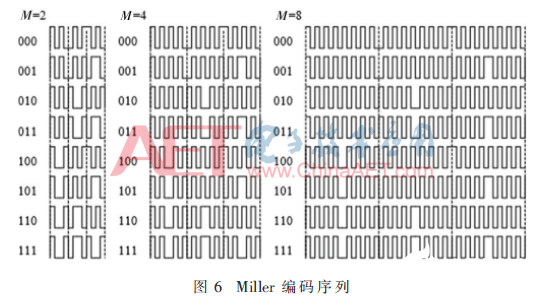

根据Miller编码规则,按照m[1:0]值不同,每个数据可能被编码成4位、8位16位码元。如果m值为01,对应M值为2,每个数据编码为4位码元;m值为10,对应M值为4,每个数据编码为8位码元;m值为11,对应M值为8,每个数据编码为16位码元。Miller编码序列如图6所示,每个编码序列分别对应M值为2、4、8。由图可知数据编码时,只有在数据-0和-0边界电平不发生翻转跳变以外其他数据边界处都会发生电平的翻转跳变。

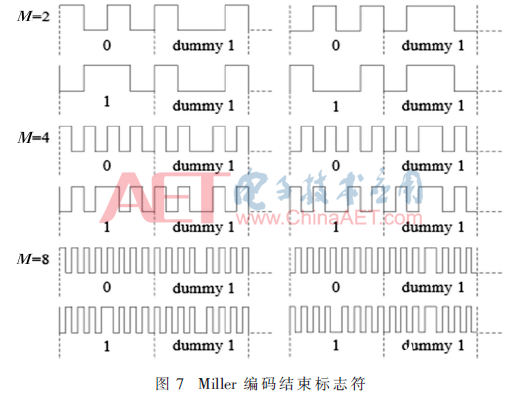

与FM0编码类似,Miller除了采用电平翻转实现编码外,编码结束后在数据的尾部同样需要添加结束标志。FM0采用固定码流作为结束标志,即保持持续码元电平。但是Miller编码的结束标志相对会复杂一些,如图7所示。

3 验证架构

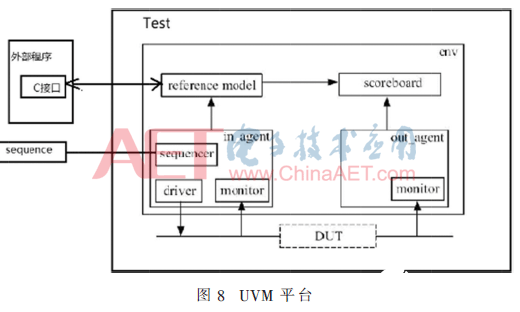

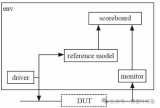

本文设计UVM平台如图8所示。

v 组件搭建描述:

(1)interface:声明接口。

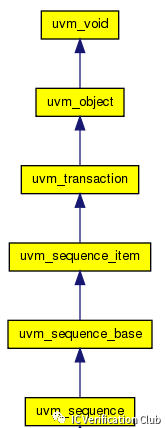

(2)transaction(数据包):继承于uvm_sequence_item,利用随机化和相关约束约束产生随机数据,创建两个transaction对象,transaction_in在DUT输入端输入,transaction_out在DUT输出与参考模型的输出相比较。

(3)sequence类:继承于uvm_sequence,加入objection机制来控制验证平台的关闭,利用repeat( )来控制执行的次数。

(4)sequencer:继承于uvm_sequencer,连接driver,实现数据的发送。

(5)driver类:继承于uvm_driver,与sequencer连接,用来请求数据。

(6)monitor类:继承于uvm_monitor,创建monitor_before和monitor_after,前者用来收集driver发送的数据,后者用来监测DUT的输出,分别在monitor_after和monitor_before中设置covergroup用来收集功能覆盖率。

(7)agent类:继承于uvm_agent,创建i_agent和o_agent,前者用来封装driver和monitor_before,后者用来封装monitor_after,声明并例化sequencer、driver、monitor,利用端口将它们连接起来。

(8)reference_model:继承于uvm_component,将外部C_Model通过DPI调入,并将数据存储,用来与monitor监测到的DUT的输出做比较。

设计FM0编码的C_Model。模型输入包括了m参数、data,输出编码后数据及编码后的数据长度。首先需要将数据读入模型,根据数据电平编码。编码算法主要设置一个变量data_tmp,在编码开始时设置为1,如果是编码-0,则输出码元~data_tmp和data_tmp,data_tmp值保持不变。如果是编码-1,则输出码元~data_tmp和~data_tmp,data_tmp值取反。通过不断更新data_tmp值来实现数据的编码输出,编码完成后添加结束标识符。

设计Miller副载波调制编码的C_Model,模型输入包括了m参数、data,结合副载波调制类型和数据类型,将编码后的数据及长度输出,另外,由于Miller前同步码最后一位码元电平为低,因此其初始data_tmp应为0,结合m的值进行编码,编码完成后添加结束标识符。

(9)Scoreboard类:继承于uvm_scoreboard,将monitor_after检测到的输出与reference_model得到的输出做比较。

(10)env类:继承于uvm_env,声明并例化agent,reference_model,scoreboard,利用端口将它们连接起来。

(11)Test类:继承于uvm_test,声明并例化env,设置default_sequence来启动sequence。

(12)Top模块:声明接口,实现DUT和平台互连,设置时钟信号。

4 仿真结果

环境搭建完毕后用QuestaSim进行仿真验证,根据输出的波形和验证信息比较DUT功能的正确与否,并查看输出的功能覆盖率来检测各功能点的实现状况。

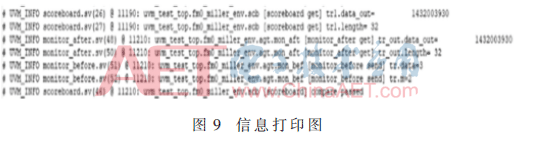

由图9所示可以发现,UVM计分板中显示验证通过,DUT的输出和模型的输出是一致的,DUT的设计满足功能实现。

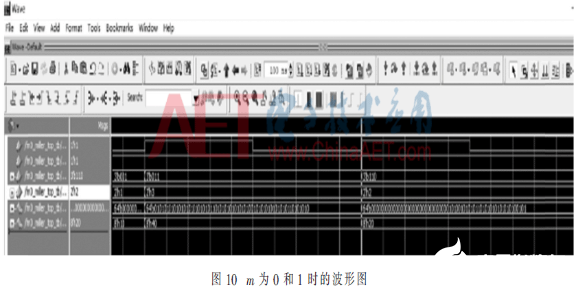

由图10可知,m=0时,执行FM0编码,m=1时,即执行miller编码,每个数据分别编码为2和4个码元,由图可知:m=0,data=3′b000,得到编码后的数据为01010100,数据长度为8位,最后2位是结束标识符00,根据FM0编码原则结果是正确的;而m=1,data=3′111,得到的编码后数据为1001_0110_1001_0110,数据长度为16位,最后4位0110是结束标识符,根据miller编码原则结果是正确的。

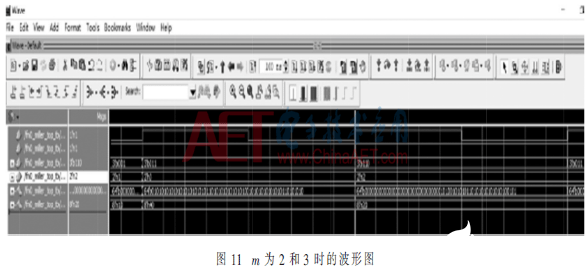

由图11可知,m=2和3时,即执行miller编码,每个数据分别编码为8和16个码元,由图可知:m=2,data=3′b110,得到编码后的数据为1010_0101_0101_1010_1010_1010_1010_0101,数据长度为32位,最后8位是结束标识符1010_0101,根据miller编码原则结果是正确的;而m=3,data=3′011,得到的编码后数据为0101_0101_0101_0101_0101_0101_1010_1010_1010_1010_0101_0101_0101_0101_1010_1010,数据长度为64位,最后16位0101_0101_1010_1010是结束标识符,根据miller编码原则结果也是正确的。

图12是一个由覆盖率驱动并且受约束的随机分层测试平台所产生的整个FM0、Miller编码仿真波形图,由图可见,平台跑了很多个testcase。

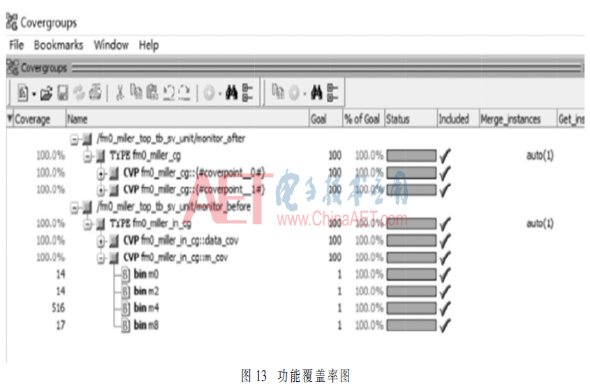

图13描述此DUT的功能覆盖率,FM0编码以及Miller编码的3种模式都覆盖到了,各功能点的覆盖率达到了100%。

5 结论

UVM验证方法学作为目前主流的IC验证方法学,尽管在前期搭建验证平台的的时间较长,但是执行效率很高,可以缩短整个研发的验证时间。本文介绍了基于DPI-C接口和UVM相结合的验证环境,实现了C程序与基于UVM环境的接口对接,使用受约束的随机激励以及覆盖率驱动,使验证平台中程序开发方便且调试方便,缩短了验证周期,保证了验证的完备性,有效地缩短了验证周期,提高了验证效率,加大了芯片的面试可能性。

参考文献

[1] 张强.UVM实战[M]。北京:机械工业出版社,2014.

[2] 刘斌。芯片验证漫游指南[M]。北京:电子工业出版社,2018.

[3] 程刚,蔡敏。基于SystemVerilog的SoC功能验证方法研究[J]。科学技术与工程,2009(22):6814-6818.

[4] 克里斯·斯皮尔.SystemVerilog验证[M]。张春,译。北京:科学出版社,2009.

[5] 徐伟俊,杨鑫,陈先勇,等。针对功能覆盖率的验证过程[J]。中国集成电路,2007(7):58-62.

[6] 克里斯·斯皮尔.SystemVerilog验证:测试平台编写指南[M]。张春,麦宋平,赵益新,译。北京:科学出版社,2009.

[7] 李璐,周春良,冯曦,等。基于DPI-C接口的可扩展SOC验证平台[J]。电子设计工程,2018,26(4):136-140.

[8] Michael Keating.Reuse methodology manual for system-on-a-chip design[M].Third Edition.Kluwer Academic Publishers,2002.

电子发烧友App

电子发烧友App

评论