本文介绍了一种基于NIOS II软核处理器实现对LCD-LQ057Q3DC02控制的新方法。在设计中利用FPGA的Altera的SOPC Builder定制NIOS II软核处理器及其与显示功能相关的“软” 硬件模块来协同实现显示控

2011-11-09 11:30:07 2000

2000

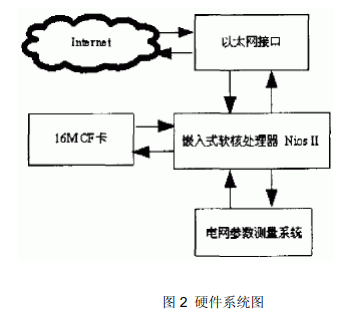

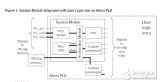

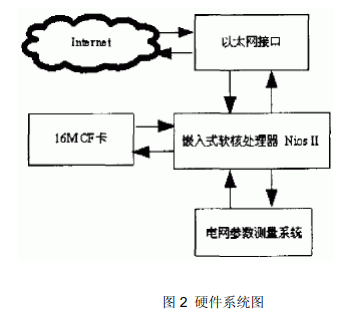

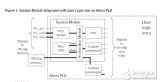

系统的硬件结构如图2所示。硬件系统的核心是构建于Ahera Cyclone FPGA中的Nios II嵌入式软核处理器。Nios II系列嵌入式处理器是一款通用的RISC结构的CPU,它定位于广泛

2020-06-28 14:49:45 540

540

基于μC/OS-II实时操作系统实现多任务管理运行模式,采用Nios II 32位处理器作为LED显示屏控制系统的核心,控制单屏幕多窗口任意显示。整个控制系统在一片FPGA上实现,使用SOPC Builder软

2011-10-02 16:00:21 2366

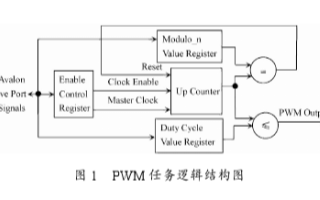

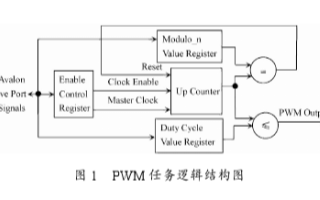

2366 SoPCBuilder环境下加载使用,方便了用户开发一个自定制的片上系统。本文通过在NiosⅡ嵌入式系统内部集成了基于Avalon总线的脉冲宽度调制(PWM)从外设,介绍了自定制Avalon设备的过程。将其应用在嵌入式智能小车监控系统,为采用NiosII处理器的开发者提供了一些方法和建议。

2019-08-21 08:20:09

: not responding.Resetting and trying again: FAILEDLeaving target processor paused这是什么问题?NIOS II 里的C代码下载不下去?

2015-02-18 12:13:54

我用EP3C16F芯片搭建了一个图像采集、处理和显示系统,sdram设计为一个输入两个输出,一个输出送给vga控制器,另外一个输出送到nios上的图像处理模块。vga没有挂在sopc builder上,我想问一下,从sdram中输出的数据在nios上处理后,怎样再让它显示到vga上?

2015-05-19 16:43:49

用Quartus II 12.0 和Nios II 12.0 Software Build Tools for Eclipse做一个led流水灯,硬件开发已经成功,但在软件这部分是发现不能识别

2020-05-31 22:57:07

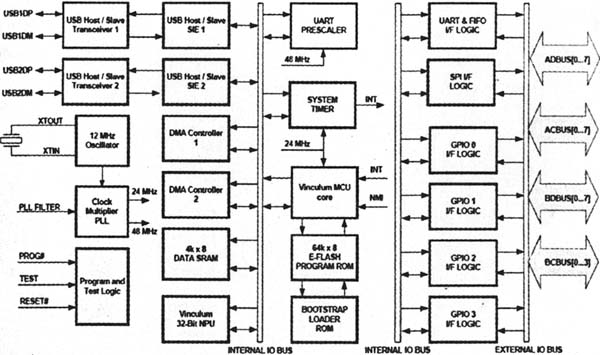

(Intellectual Property Core)。本文介绍USB 2.0设备控制器IP中的AHB接口部分设计。1设计概述1.1协议概述 设计前首先需要了解USB和AHB数据传输的特点

2019-05-13 07:00:04

为了更好的将USB的通用性和CAN的专业性结合起来,通过计算机的USB接口接入CAN专业网络,实现系统控制的便利性和应用的高效性,本文讲述了一种基于ARM7处理器实现USB接口与CAN总线的实例,通过其可以在PC实现对CAN总线上设备的监控。

2020-03-25 07:18:31

USB的总线结构是由哪些部分组成的?USB的工作原理是什么?USB外设控制器的实现方式有哪几种?

2021-10-14 15:32:16

如何与AD采集融合。 查询了一下,发现可以使用Avalon总线,将AD的verilog功能描述封装成一个IP核,挂到Avalon总线,实现verilog与NIOS II的通讯。 但是不知道这种方法速度够不够

2017-11-21 10:11:22

nios ii 编程出现 altera_avalon_pio_regs.h:no such file怎么办

2017-04-14 11:27:50

nios ii双核例子nios ii双核例子NIOS II 双核构建的简单例子,希望对大家有所帮助。 1、 实现简易功能 Cpu_0控制pio_cpu_0(输出),令其输出为1。此输出和cpu_1

2012-08-12 15:18:48

最近在学习nios,想知道nios与外面fpga的数据怎么通过avalon协议传输?我在搭建mcu的时候怎么搭建地址线与数据线?是用i2c slave to avalon-MM master bridge这个核还是直接放PIO?哪位大神指点一下

2019-06-17 14:34:10

摘要:讨论了CAN总线控制器与DSP之间的接口,介绍了流行的CAN控制器芯片SJA1000和TMS320系列DSP芯片的接口时序,并给出了它们的接口方法和电路。关键词:CAN控制器 DSP 时序

2018-12-03 15:22:37

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

当前日益繁忙的航道运输所提出的高质量安全航行的需求。Nios II是Altera公司推出的基于RISC技术的软核CPU,作为一种用户可随意配置和构建的32位总线嵌入式系统微处理器软核,它的硬件设计方面

2015-01-30 11:05:50

这是我的毕设,上位机用的是黑金动力社区的USB调试助手,下位机是Nios II+MCP2515+MCP2551,截图是示波器上CANH和CANL信号,是差分信号。

2012-05-20 08:52:15

`附件为小梅哥SOPC公开课第二课NIOS II自定义IP的设计与使用的建随堂工程。小梅哥SOPC公开课第二课主要讲解如何使用Verilog自己编写一个符合NIOS II Avalon MM接口总线

2016-08-13 11:04:32

论文以Compaq、Microsoft 等公开的 USB 主机控制器接口规范为基础,遵循USB 主机的协议规范,开发了独立于操作系统的USB 主机底层驱动程序,并在S3C2410 平台上得到了验证。下面详细论述主机控制器接口规范及 驱动程序实现。

2020-03-31 06:57:20

,添加了一个自定义的NAND Flash控制器组件,如图6.1所示,这个组件也是挂在Qsys系统的Avalon-MM总线上。NAND Flash复杂的底层驱动时序都由这个控制器内部产生,无需NIOS

2016-11-21 17:41:21

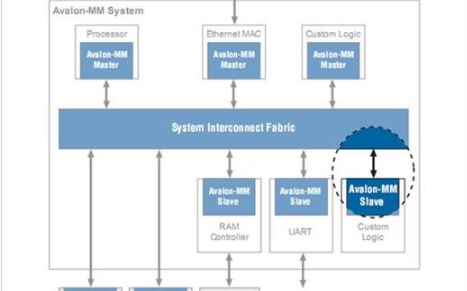

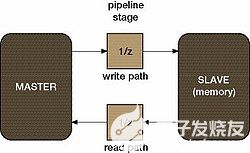

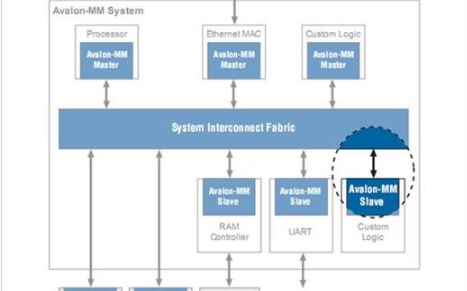

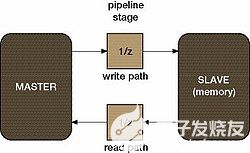

Altera公司主推的应用于其软核处理器NIOS II上的总线,主要包括Avalon-MM总线和Avalon-ST总线,下面我们就去认识他们。基于NIOS II处理器的片内系统互连主要靠的就是

2016-11-26 17:10:43

简单的NIOS II处理器与外设互联接口那么我们可能还会更关心这个硬件连接的具体实现细节,也就是Avalon-MM总结的控制时序。如图6.9所示,打开工程管理窗口中的pio_led模块代码,这个代码

2016-11-28 18:05:13

让Avalon-ST总线派上用场。假设这个实例系统中NIOS II处理器负责将前端采集的图像进行解码或是其他处理,然后再送给显示终端。那么在图像采集的前端就会产生大量的数据吞吐量,而在图像显示刷新

2016-12-01 17:56:04

、iic_avl_driver.v模块和iic_protocol.v模块三个模块为IIC控制器组件。iic_controller模块是顶层模块;iic_avl_driver.v模块实现Avalon-MM总线的从机接口

2017-04-16 22:50:28

所示。以NIOS II处理器为主构建一个基本的嵌入式系统。IIC控制器外设为自定义组件,通过Avalon-MM总线连接到NIOS II处理器,NIOS II处理通过对IIC控制器的访问实现HDMI

2017-04-24 19:27:08

在FPGA系统中,实现对外部A/D数据采集电路的控制接口逻辑,由于其逻辑功能不是很复杂,因此可采用自定义的方式。采用这种方法进行设计有两种途径。①从软件上去实现。这种方案将NIOS处理器作为一个主控制器

2019-04-17 07:00:01

在FPGA系统中,实现对外部A/D数据采集电路的控制接口逻辑,由于其逻辑功能不是很复杂,因此可采用自定义的方式。采用这种方法进行设计有两种途径。①从软件上去实现。这种方案将NIOS处理器作为一个主控制器

2019-04-25 07:00:02

基于NIOS II 软核处理器的SOPC 技术摘要:介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II

2009-10-06 15:05:24

的状态。SOPC Builder中没有相应的FIFO接口控制器,因此需要自己定义FIFO接口。可首先在Quartus II的界面中新建一个.bdf文件,在下拉菜单中选择MegaWizard

2018-12-07 10:27:46

II软核来完成,Nios II处理器将片上存储器中的数据逐一读取并进行处理之后显示在LCD上,Avalon总线负责各个控制器模块的数据传输。FPGA选用Altera公司的EP3C5E144C8。1.2

2019-06-03 05:00:06

CMOS传感器件,本指纹采集系统采用传感器的微处理器总线(MCU)模式,传感器的8位数据线直接与DE2开发板的扩展口相接,采用Nios II自定义外设的接口形式来对FPS200指纹图像传感器进行初始化控制

2019-04-29 07:00:08

目录一、基于Nios II的hello world1、NiosII实现hello world1.1硬件设计1.2软件设计1.3下载硬件和软件一、基于Nios II的hello world1

2021-12-27 08:13:55

瓦隆大师--[tr]AD 7091R外围设备[tr]0x00000120-[tr]表1系统组件Nios II处理器包含实现与DUT通信协议的外围设备。外设分为三个逻辑模块:与Avalon总线接口和与片上

2020-10-20 21:39:59

和外部总线对存储器访问之间的仲裁。PL则实现USB的数据I/O和控制。接口有三种:一种是与微控制器之间的功能接口;一种是与单口同步静态存储器(SSRAM)之间的接口;另外一种是与物理层之间的接口。这里

2021-06-29 07:30:00

接口规范为基础,遵循USB 主机的协议规范,开发了独立于操作系统的USB主机底层驱动程序,并在S3C2410平台上得到了验证。下面详细论述主机控制器接口规范及驱动程序实现。2 USB体系结构USB体系

2019-05-29 05:00:03

应用较 多的OHCI 为例,介绍接口规范和驱动程序实现细节。3 HCD 的实现USB 主机控制器驱动程序(HCD)是USB 软件协议栈最底层一部分。HCD 向上仅对 USBD 提供服务,HCD 提供一个

2018-11-20 11:14:56

这类文章中很少见对控制器各个模块进行仿真验证内容。 文中提出一种针对TFT-LCD 触控屏控制器IP 核的设计方法。该控制器具有Avalon 总线接口,与其他标准IP 核一起构成以NiosⅡ为核心

2018-11-07 15:59:27

目前,USB接口的使用越来越广泛,许多设备上都提供了USB接口。传统的USB控制器需要使用包括数据线和控制线在内的十多根线,占用了大量的CPU资源。而现代设备正在向体积小、功能强的方向发展,CPU

2018-11-20 11:13:59

SoPC与Nios Ⅱ嵌入式系统的原理与组成是什么?如何实现AD7329与Nios Ⅱ接口的设计?

2021-04-07 06:07:13

一种基于OHCI的嵌入式USB主机控制器接口实现

2021-06-02 06:50:43

本文利用Altera公司的Quartus开发工具设计了一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。

2021-04-08 06:25:12

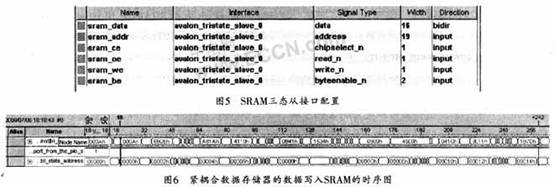

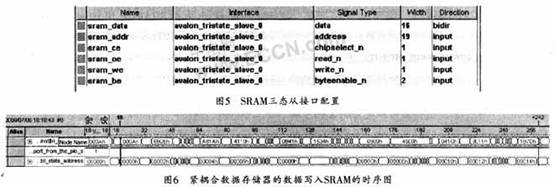

SOPC中的Avalon总线是什么?Nios II系统中的紧耦合存储器该如何去设计?怎样去设计一种SRAM的接口?

2021-05-28 06:44:01

大神你们好:小弟目前遇到一个问题,想自己设计一个IP模块集成到Qsys中,利用avalon的突发读写传输来读写这个模块,但是接口必须满足什么条件,就是必须有什么信号,另外,nios来访问的时候,是通过什么函数来控制呢,这一点一直不清楚,求教

2016-03-27 10:52:08

本文设计实现了一个简单的基于Avalon总线的TFT LCD控制器。

2021-06-04 06:39:27

/nios2/emb-nios2_ide.html)Nios II集成开发环境(IDE)是Nios II系列嵌入式处理器的基本软件开发工具。所有软件开发任务都可以Nios II IDE下完成,包括编辑

2015-09-08 22:35:45

一个基于Avalon总线接口的UPFC控制器IP核,以便于和NiosII组成一个完整的控制系统。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波

2019-06-03 05:00:05

和拆分用自定义指令来实现。4)在FPGA内完成NIOSⅡ与HS3282接口模块、NIOSⅡ与PCI总线的接口模块及复位电路等。5)系统编译完成后使用QuartusⅡ 5.0软件和ByteBlaster

2019-04-29 07:00:06

。另外本文在此平台之上,移植了嵌入式操作系统,并在此环境下实现了SD卡的接口设计,因此包括了整个的硬件和软件设计。在系统设计的过程中,分析了Nios II 的Avalon总线的系统架构、SD 卡的通信协议。

2019-05-29 05:00:04

上rom、内部定时器、uart串行口、sram、flash接口等系统部件。这些部件均以可编程逻辑部件的形式实现,芯片内部部件结构图如图3所示。cpu和所有部件通过avalon总线连接在一起。sopc

2019-04-18 07:00:07

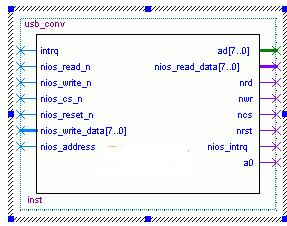

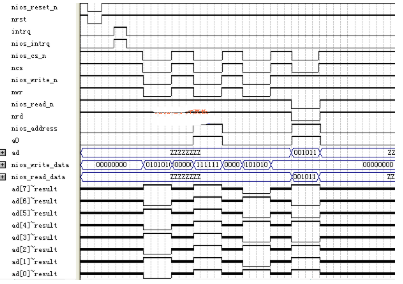

到外设插入、拔出或者数据发送错误、超时、数据溢出等异常情况时,通过将intrq置高电平通知Nios II。3.2 USB接口模块设计 AVALON总线为用户提供了非常友好的接口,使得系统搭建时的一些

2019-05-05 09:29:32

实现。3 VGA数据缓存模块设计 数据缓存模块式通过Altera提供的SOPC工具中,Avalon总线上挂的一个SRAM控制器来实现数据的读写功能,Avalon总线与SRAM的接口对用户是透明的。只需

2019-06-21 05:00:08

介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II 的SOPC 技术的方案设计。该设计增强了系统功能,改善

2009-07-22 15:35:35 0

0 本文以Nios II 嵌入式软处理器为核心,利用USB 控制芯片CH372,设计了基于Nios II 嵌入式软处理器的USB 通信接口。本文重点介绍了USB 接口的硬件实现方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 介绍了基于NIOS II 软核处理器的SOPC 技术,分析了传统方法和基于SOPC 技术的方法实现扩频收发机的优劣,详细说明了嵌有双NIOS II 的SOPC 技术的方案设计。该设计增强了系统功能,改善

2009-11-27 14:23:43 15

15 本文讨论了基于Avalon 总线流传输的配置LCD 显示控制器IP 核的设计,根据自顶向下的设计思想,将IP 核进行层次功能划分设计,并对IP 核的仿真验证,最后加入到NiosII 系统中。该I

2009-11-30 14:33:46 16

16 本文详细介绍了USB 总线的光隔离接口的隔离原理、硬件组成及控制程序的设计。该实现方案采用先进的高速光隔离技术和CPLD 控制技术,对基于USB 的测试与测量的设备、人体起保

2009-12-23 15:04:38 25

25 在NIOS-II 系统中A/D 数据采集接口的设计与实现摘要:进行 SOPC 开发,很有必要学习一下定制NIOS 外设的方法和技巧。本文就是基于这种目的,详细的论述了在NIOS 系统中A/D 数据

2010-02-08 09:55:43 23

23 基于Avalon总线的可配置LCD 控制器IP核的设计

本文讨论了基于Avalon 总线流传输的配置LCD 显示控制器IP 核的设计,根据自顶向下的设计思想,将IP 核进行层次功能

2010-02-09 09:34:44 27

27 Avalon 总线是一种将片上处理器和外设连接成片上可编程系统(SOPC)的一种简单总线结构。Avalon总线是一种接口方式,它规定了主从设备之间的接口方式及其通信时序。Avalon 总线

2010-07-09 18:39:41 0

0 本文详细介绍了USB总线的光隔离接口的隔离原理、硬件组成及控制程序的设计。该实现方案采用先进的高速光隔离技术和CPLD控制技术,对基于USB的测试与测量的设备、人体起保护作用

2010-07-21 17:26:16 19

19 NIOS II软核处理器是Altera公司推出的一款灵活高效的嵌入式处理器。该处理器的应用常见于控制和通信领域。本文描述了在NIOS II系统上实现平台直方图均衡算法(Plateau Equalization ,PE)

2010-08-06 15:48:40 24

24 研究基于Avalon-ST接口帧读取的IP核设计应用,通过Avalon-ST接口将外部存储中不同格式的帧数据转化为视频流进行输出。根据Avalon总线协议及Avalon-ST视频协议研究设计方案,使用Verilog H

2010-08-12 15:58:32 0

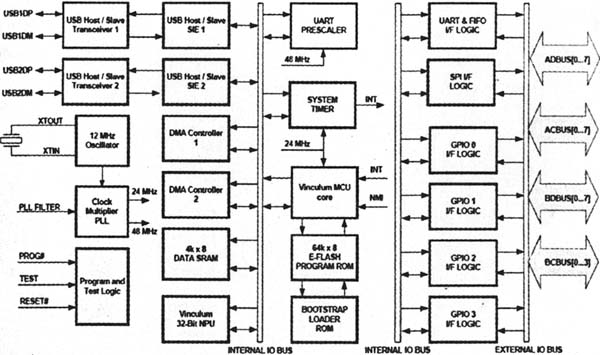

0 基于PIC微控制器和Vinculum USB接口芯片的硬件设计及其编程,使USB闪存驱动可做为各种嵌入式应用中

2009-04-22 18:43:42 1113

1113

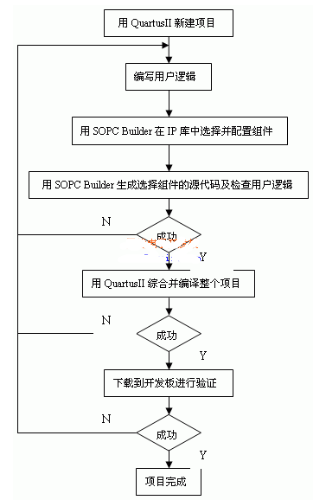

NIOS II的特性及开发设计流程

NIOS的主要特点NIOS II是一个用户可配置的通用RISC嵌入式处理器。Altera推出的NIOS II系列嵌入式处理器扩展了目前

2010-02-08 14:47:31 1430

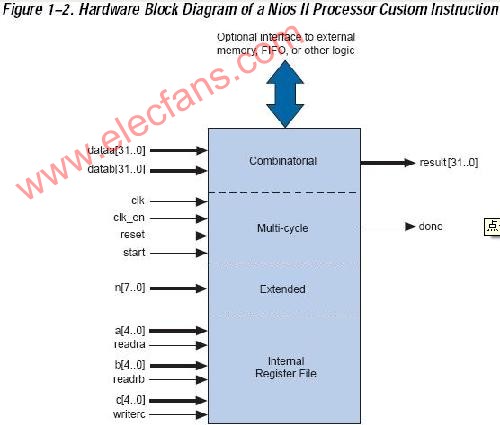

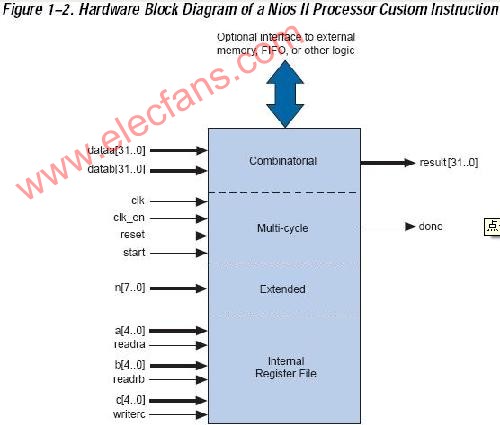

1430 NIOS II前哨计划step by step 1(NIOS II用户指令)

可编程软核处理器最大的特点是灵活,灵活到我们可以方便的增加指令,这在其他SOC系统中做不到的,增加用户指令可以把

2010-03-27 09:52:23 1040

1040

NIOS II的SOPC中存储器型外设接口的设计

0 引言随着微电子设计技术与工艺的发展,数字集成电路由最初的电子管、晶体管逐步发展成专用集成电路(ASIC,Application S

2010-04-13 09:54:39 944

944

利用SOPC Builder 可以在短时间内把Nios II CPU、Avalon 总线、外围设备、片内调试模块等集成在一起生成系统需要的Nios II 处理器, 然后用Quartus II 软件把NIOS II 处理器其它外部设备接口结合在

2011-09-13 17:24:32 58

58 I2C 总线的实现关键是SDA,他是双向线,如果对与一个芯片只写而不读,I2C 实现起来很容易.使用NIOS 实现I2C 总线的关键是处理好SDA 双向线的问题.

2011-11-01 14:28:50 37

37 根据Nios II处理器的Avalon总线规范,设计了一款面向步进电机的控制器IP核。该定制IP核采用软、硬件协同设计的方法,功能符合Avalon总线的读写传输时序,具有完备的步进电机驱动能力。仿

2011-12-23 14:02:32 44

44 Nios II内核详细实现

2012-10-17 13:59:49 83

83 Nios II 系列处理器配置选项:This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 Nios II定制指令用户指南:With the Altera Nios II embedded processor, you as the system designer can

2012-10-17 14:18:49 37

37 使用Nios II紧耦合存储器教程 Chapter 1. Using Tightly Coupled Memory with the Nios II Processor Reasons

2012-10-17 14:43:25 48

48 电子发烧友网核心提示 :当您采用Nios II 嵌入式处理器进行设计时,您所使用的将是由Altera及其合作伙伴提供的可靠的软件开发工具和软件组件。 Nios II 嵌入式设计包 Nios II嵌入式设计

2012-10-17 15:31:13 1704

1704

为了实现对嵌入式系统中大量数据存储的需求,提出了一种基于NIOS II的SD卡存储系统设计方案,并完成系统的软硬件设计。该存储系统使用SPI模式对SD卡进行读写访问,SPI时序由NIOS II的

2013-07-25 16:19:49 66

66 NIOS II 常见问题总结,如果你想要Altera的FPGA做嵌入式设计,肯定要涉及到NIOS II的使用,本文总结了一些NIOS II的常见问题与解决方法

2015-12-01 15:43:34 14

14 在 Nios II 中根据需求定制基于 Avalon 总线的 IP 核模块,并使用定制的模

块实现对数码管的控制。通过本章,你能学到

(1)在 Nios II 中定制基于 Avalon 总线的 IP 核模块。

(2)在 Nios II 中控制数码管。

2015-12-14 15:39:39 3

3 NIOS_II各种性能表格对NIOS_II内核在各种型号的FPGA上的实现的性能说明

2015-12-21 17:19:15 22

22 基于Avalon总线的非标准以太网控制器IP核设计_薛毅

2017-03-19 11:33:11 1

1 Avalon 总线是一种将片上处理器和外设连接成片上可编程系统(SOPC)的一种简单总线结构。Avalon总线是一种接口方式,它规定了主从设备之间的接口方式及其通信时序。

2017-11-21 09:10:05 3414

3414

Nios系统的所有外设都是通过Avalon总线与Nios CPU相接的,Avalon总线是一种协议较为简单的片内总线,Nios通过Avalon总线与外界进行数据交换。

2018-01-27 22:03:12 4565

4565 )中,在SoPCBuilder环境下加载使用,方便了用户开发一个自定制的片上系统。本文通过在NiosⅡ嵌入式系统内部集成了基于Avalon总线的脉冲宽度调制(PWM)从外设,介绍了自定制Avalon设备的过程。将其应用在嵌入式智能小车监控系统,为采用NiosII处理器的开发者提供了一些方法和建议。

2020-03-18 08:00:00 1672

1672

AVALON总线,其实是一种交换架构的协议,在自定义外设挂在AVALON总线上时,一定要注意地址对齐。

2019-02-11 17:15:26 1473

1473

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线

2019-08-06 06:01:00 2879

2879 Nios系统的所有外设都是通过Avalon总线与Nios CPU相接的,Avalon总线是一种协议较为简单的片内总线,Nios通过Avalon总线与外界进行数据交换。

2019-10-08 07:05:00 1288

1288 Nios系统的所有外设都是通过Avalon总线与Nios CPU相接的,Avalon总线是一种协议较为简单的片内总线,Nios通过Avalon总线与外界进行数据交换。

2019-09-30 07:04:00 1232

1232

USB设备-USB接口(1-N)-USBROOTHUB-USB控制器-PLB/PCIE总线-CPU/内存/DMA控制器。

2020-07-16 16:41:21 4031

4031 电子发烧友网为你提供NiOSⅡ处理器的Avalon总线架构资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-27 08:54:47 9

9 Wishbone B.3总线。以类似的方式,Altera引入了自己的互连方案,称为Avalon Bus,SOPC Builder和Nios(II)系统就是围绕该方案制造的。Xilinx 还推出了自己的总线,称为片上外设总线与处理器本地总线 相结合。

2022-11-14 15:38:55 790

790

电子发烧友网站提供《基于NIOS II的SD卡读写控制设计.pdf》资料免费下载

2023-11-06 10:06:43 1

1

电子发烧友App

电子发烧友App

评论