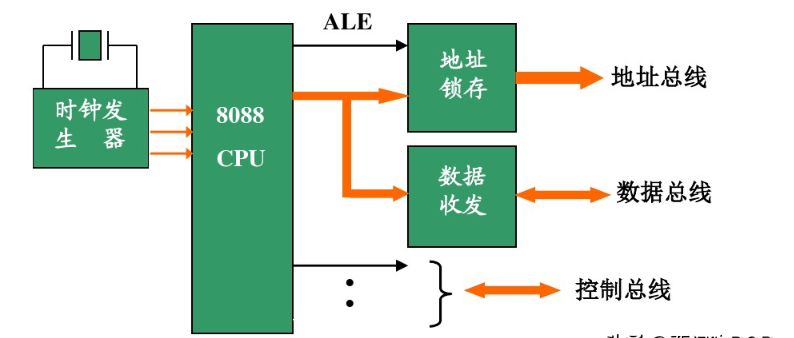

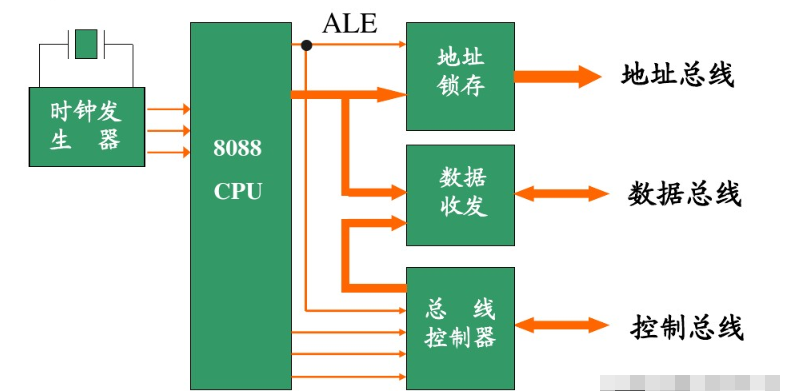

51 系列单片机具有完善的总线接口时序,可以扩展控制对象,其直接寻址能力达到64k( 2的16次方) 。

2012-03-22 10:27:54 6788

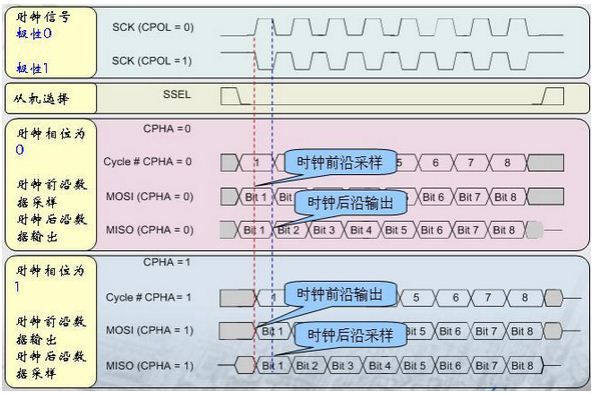

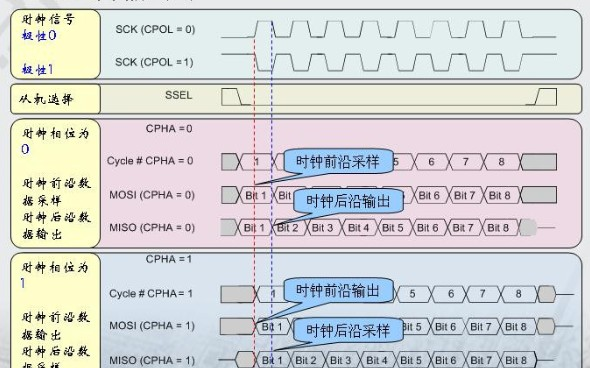

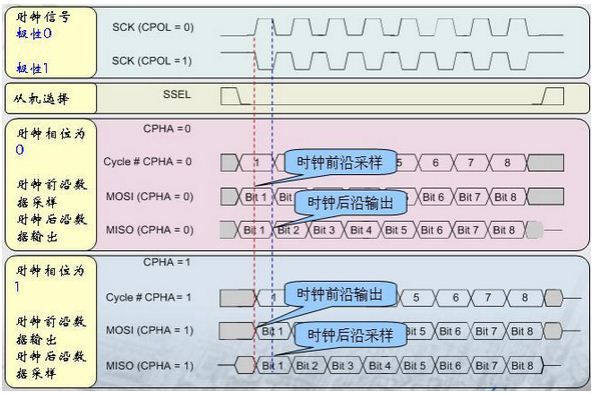

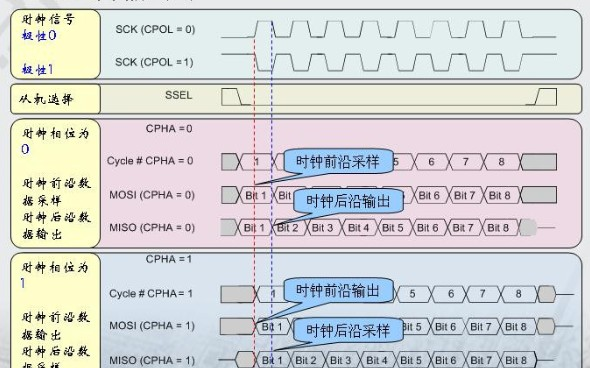

6788 SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

2016-01-25 13:54:56 7000

7000

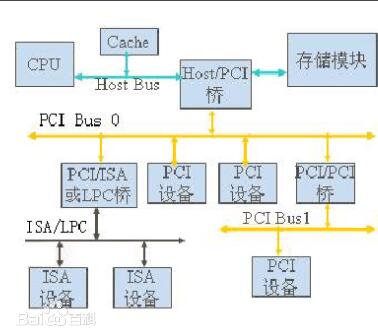

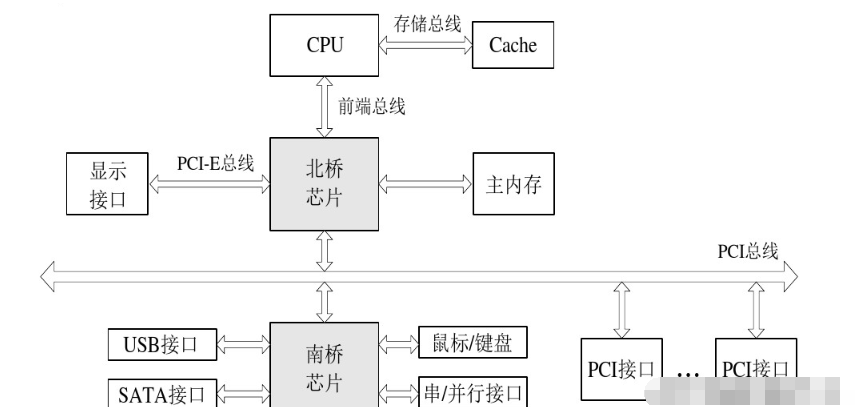

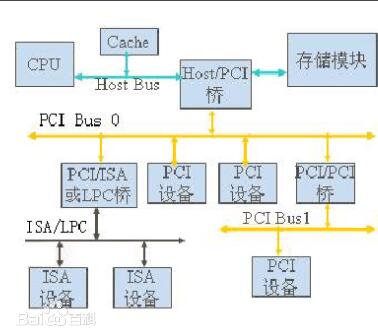

本文主要详解PCI总线与PXI总线有什么区别,首先介绍了PCI 总线结构图、特点及PCI总线性能,其次阐述了PXI总线的特性,最后介绍了PCI总线与PXI总线的区别。

2018-05-24 09:15:23 13958

13958

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2022-08-02 12:42:17 6661

6661 reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的路径。

2023-06-26 14:28:01 604

604

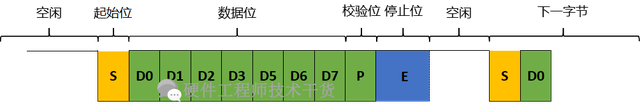

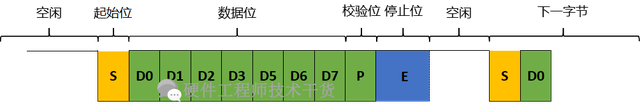

如上图所示,串口时序由起始位、数据位、校验位、停止位组成。

2023-09-12 15:42:04 1098

1098

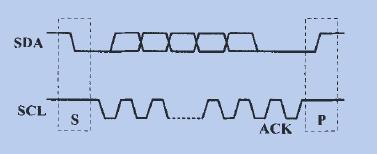

I²C总线在嵌入式系统中很常见,今天就来给大家讲讲I²C总线的时序。

2024-02-23 09:47:10 523

523

1、2、3、ARM嵌入式开发之ARM指令与ARM汇编入门4、ARM嵌入式开发之ARM汇编高级教程与APCS规范详解视频下载地址:内容:01_ARM嵌入式开发之ARM基础概念介绍...

2021-12-23 06:45:18

DC/DC开关电源中接地反弹的详解

2021-01-28 06:17:31

Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年

2021-01-07 17:11:26

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

的写法是一致的,后文将详细明。3.寄存器-寄存器的时序约束寄存器-寄存器的约束,在同步时序电路中,就是周期的约束。对于完全采用一个时钟的电路而言,对这一个clk指定周期约束即可。但是如果采用了多个时钟

2019-07-09 09:14:48

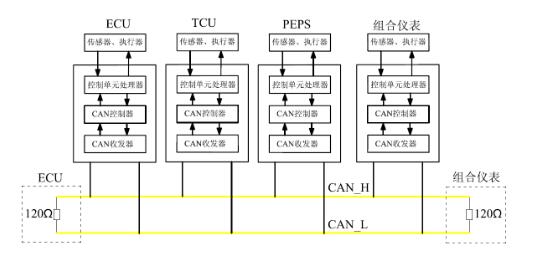

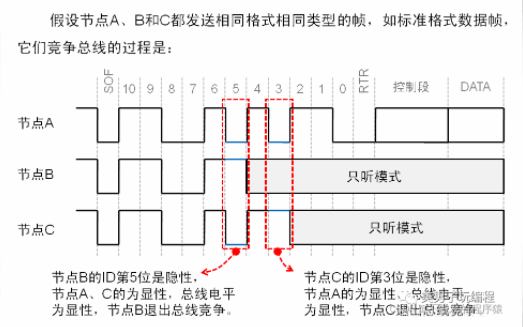

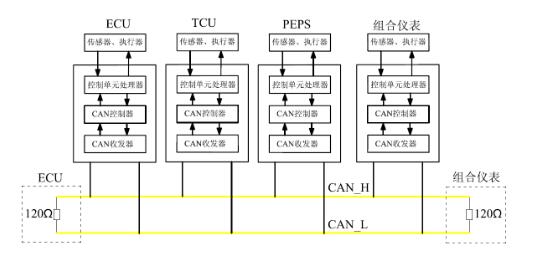

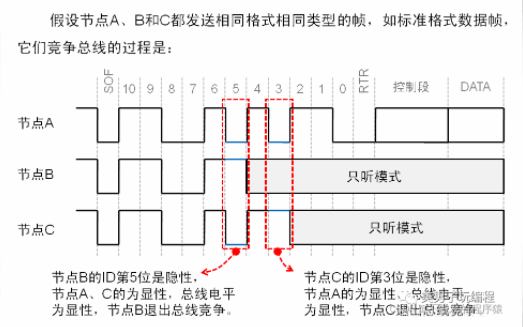

作者:Xiaomin 概述 CAN(Controller Area Network)总线协议是由 BOSCH 发明的一种基于消息广播模式的串行通信总线,它起初用于实现汽车内ECU之间可靠的通信,后

2019-07-26 08:33:27

1、AHB传输的时序图分析正文1:AHB章节最后再复习一遍多主机的概念:总线是被总线上所有的部件所共享的一组通路(连线),对于支持多主机的总线,如果某一个主机想要与其他的部件进行通信(获得

2022-06-09 17:45:33

AMBA_AXI总线详解

2014-04-18 11:48:28

在PCB设计中,绘制原理图时避免不了要用到总线,但是在我们使用Altium Designer绘制总线时总是出现一些问题,导致总线无法使用。下面就来绘制出一条的总线,总结一些方法及注意事项,希望能够对大家有所帮助。1. 准备绘制总线,选择准备绘制总线的器件,这里就随便选择两个器件;(图文详解见附件)

2019-11-12 10:25:31

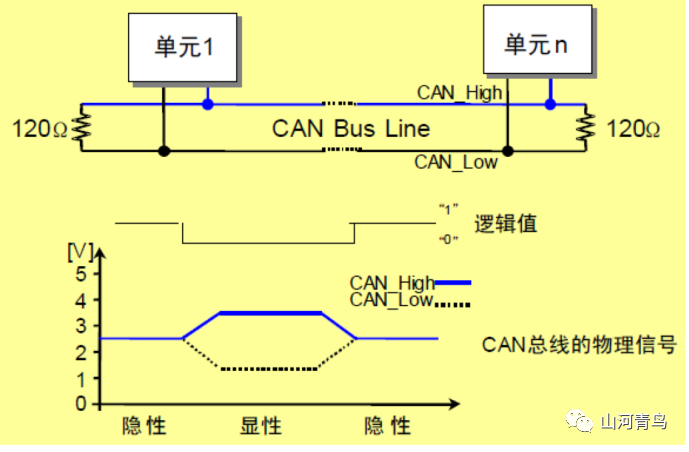

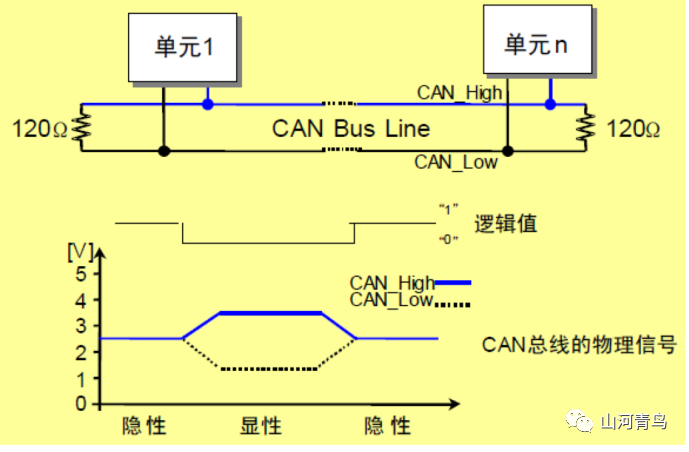

总线技术3.运行流程:4.显性隐性:一、 CAN帧结构CAN-bus通信帧:数据帧、远程帧、错误帧、过载帧和帧间隔1.数据帧由7个段组成,其中根据仲裁段ID码长度的...

2021-08-20 07:03:16

电子通信协议之CAN总线协议篇

2020-12-28 06:30:02

转载DDR3内存详解,存储器结构+时序+初始化过程2017-06-17 16:10:33a_chinese_man阅读数 23423更多分类专栏:硬件开发基础转自:首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其...

2021-07-27 07:10:34

关于对DHT11单总线时序图的理解最近上网买了一个单总线的DHT11温湿度传感器,看了一些代码,这是自己的理解,并记录。DHT11数字温湿度传感器资料DHT11数字温湿度传感器是一款含有已校准

2022-02-16 07:03:14

以前调试DS18B20的时候在网上找到的,感觉解释的很详细,又像是英文资料的中文对照,对英文不是很好的我来说是个福音。不管怎样现在贡献出来供大家交流学习。附件DS18B20时序详解.docx156.4 KB

2019-03-04 12:39:02

FAT32文件系统详解

2016-08-17 12:34:56

基本的时序分析理论1本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 何谓静态时序分析(STA,Static

2015-07-09 21:54:41

。启动信号 在时钟线SCL保持高电平期间,数据线SDA上的电平被拉低(即负跳变),定义为I2C总线总线的启动信号,它标志着一次数据传输的开始。启动信号是一种电平跳变时序信号,而不是一个电平信号。启动信号

2018-06-14 15:00:51

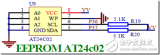

看了郭天祥的I2C总线这一节,发现他在编写向AT24C的E2PROM时时序有问题。原始部分程序为:typedef unsigned char uchar;uchar read_byte

2016-08-25 21:35:07

I2C总线概述及时序,看完你就懂了

2021-05-24 06:42:06

。一根是数据线 SDA,另一根是时钟线 SCL。0x02:iic通信时序在一个标准I2C时序中,下面所介绍的通信时序中,一般以SCL为低电平开始,中间为SDA状态,然后SCL拉高开始通信,通信固定

2022-07-04 11:23:01

1. IIC描述上图说明了在IIC总线拓扑中应该含有至少一个微控制器。该控制器通过IIC总线的SCL和SDA线与其他关联设备进行通信。基于传统的串行总线通信机制,IIC总线通信也是通过SDA与SCL

2021-11-29 06:20:06

IIC总线和SPI总线通信介绍

2020-12-23 07:02:22

IIC总线的特点IIC总线协议详解IIC总线的读写过程

2021-01-04 07:30:58

ISA(PC/104)总线信号时序简介 1.0 ISA概况2.0 ISA文献2.1 ISA规范2.2 ISA书籍3.0 ISA结构形式4.0 PC/104结构形式5.0 ISA信号描述6.0 ISA

2009-05-25 01:13:56

NE555中文资料详解

2012-08-20 13:49:07

NE555中文资料详解

2012-08-21 09:27:19

NE555中文资料详解

2012-11-23 22:08:18

SPI,是英语 Serial Peripheral Interface 的缩写,顾名思义就是串行外围设备接口。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片

2023-09-22 08:10:04

一、SysTick使用详解1. SysTick简介SysTick是一个24位的系统节拍定时器system tick timer,SysTick,具有自动重载和溢出中断功能,所有基于Cortex_M3

2021-08-12 06:32:31

越来越多的芯片集成了这种通信协议。SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。 上升沿发送、下降沿

2018-07-06 07:24:25

9-7 所示。• 同步段:在这段时间内,完成总线上各个节点的同步,需要一个跳变沿。• 传播段:这个时间段是指网络上传输的延迟时间,它是信号在总线上传播时间、输入比较器延迟和输出驱动器延迟之和的两倍

2018-12-17 11:13:33

spurious scl transition detected at有人知道这是什么问题么?仿真的时候全是这个 用的pcf8563。还有,一样的方式,读取秒分时,到小时没有发送,时序有偏移什么的??实在是无从下手啊? 大家有建议类的书籍么?

2017-01-06 09:32:34

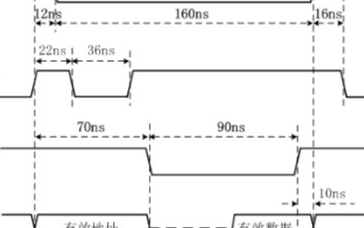

当其为16位或8位局部数据总线时,单周期读写是怎样进行的。还是数据手册中前面那个总的单周期读写时序吗?

2009-11-23 12:14:55

一.单总线协议时序对应代码1.延时函数//单总线延时函数,约1~2usvoid Delay_OneWire(unsigned int t){static unsigned char i;while(t--){ for(i=0;i

2022-01-17 08:05:52

1、一文了解解决大位宽效率问题的分段总线的前世今生 当以太网接口的速率提升到100G以上后,用传统FPGA来实现对应的数据处理时,一定会遇到总线效率的问题。 分段总线的格式 随着不断提升

2022-10-11 14:27:34

使用STM32的GPIO模拟I2C总线时序,GPIO设置为开漏模式,SDA和SCK外部必须使用上拉电阻,一般是4.7K。开漏模式的好处是,可以同时读取输入电平,而无需切换输入/输出模式。注意事项:在

2022-02-22 06:48:21

CAN总线的位时序与参数设置@ [TOC]CAN的位时序构成CAN总线的每个位(Bit)的周期 Tbit = 1 / Baudrate。根据CAN规范,每个位的时间内又可细分成4段:同步段

2021-08-20 06:38:55

有人可以详解一下下图中,imx6q的eim时序图嘛

2022-01-07 07:22:00

我已经了解到proteus中VSM Logic Analyser 可以同时分析多个端口的电平变化,但总线周期时间太短,即便只有一条指令,也包含许多总线周期,如何才能 记录下总线周期内各个端口的电平变化,得到时序图?

2015-03-13 19:42:47

PCI总线是什么?PCI总线的功能有哪些?怎样去测量PCI总线的I/O写时序波形?如何去测量夏华状元一族主板PCI写周期的时序波形?

2021-04-15 06:22:17

设计就好了。其实现在很多系统还会采用CPCI的构架,PCIX的总线还在通讯、工控等行业大量采用。并且共同时钟系统,到了133M以上,时序设计非常困难,可以说如果没有真正理解时序设计的原理,你可能做一

2014-10-21 09:35:50

微处理器8086的总线结构和时序.pdf

2006-06-29 13:46:00 146

146 FI1256MK2是被广泛应用的电视信号前端处理器,可使用I2C总线对其进行编程控制.当用在计算机扩展板中时,可由计算机总线通过硬件电路模拟I2C总线的时序.文章给出了用可编程逻辑器件G

2009-04-24 15:29:01 39

39 FI1256MK2是被广泛应用的电视信号前端处理器,可使用I2C总线对其进行编程控制。当用在计算机扩展板中时,可由计算机总线通过硬件电路模拟I2C总线的时序。文章给出了用可编程逻辑器

2009-04-27 16:02:05 33

33 ISA总线信号时序简介:1.0 ISA概况2.0 ISA文献2.1 ISA规范2.2 ISA书籍3.0 ISA结构形式4.0 PC/104结构形式5.0 ISA信号描述6.0 ISA时序图7.0 ISA信号用法8.0 ISA连接器引脚

2009-05-21 11:06:54 242

242 美国ALLEGRO文丘里风机,气动风机,气动通风机,文丘里风机应用于:炼油厂、发电厂、造船厂、造纸和纸浆厂、海洋舰船、钢铁工业以及人孔(沙井)的通风换气。文丘里风机特别适用于有毒烟雾

2022-10-18 16:30:36

时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 ARM I2C总线接口电路和时序

AR M 12C 总线由一根数据线SDA( se riald ataline)和一根时钟线SCL(serial clock line)构成,每个电路模块挂在12C总线的SDA

2009-03-14 17:57:08 2436

2436

OrCAD中创建总线及用法详解,如何创建总线,菜单place->bus或者右侧快捷按钮

2011-12-02 10:18:21 24809

24809 本文给出了用可编程逻辑器件GAL配合ISA总线模拟I2C总线时序来对FI1256 MK2进行控制的方法。该方法与PCI总线进行模拟的方法相类似。

2012-03-27 11:33:15 2687

2687

spi协议介绍,通过文档形式说明spi总线时序

2015-11-19 15:12:49 55

55 24C02中IIC总线的应答信号(ACK)时序图分析,很好的单片机学习资料。

2016-03-21 17:30:06 93

93 汽车CAN总线基础详解与基本应用情况与实例分享

2016-03-22 15:50:11 0

0 CAN总线通信详解。

2016-03-30 16:46:10 0

0 温度传感器DS1820使用资料最全版,含读写时序图。主机总线在T0时刻发送一复位脉冲(最短为480US低电平信号),接着在T1时刻释放总线并进入接收状态。 DS18B20在检测到总线的上升沿后,等侍15-60US,接着 DS18B20在T2时刻发出存在脉冲(低电平,持续60-240US)

2017-10-18 17:45:00 59

59 Xilinx FPGA工程例子源码:用FPGA模拟VGA时序PS_2总线的键盘接口VHDL源代码

2016-06-07 15:11:20 32

32 DS18B20中文手册主要介绍其工作原理(时序图).主机总线从T0时刻从高拉到低电平时,总线只需要保持低电平 7US。之后在T1时刻将总线拉高,产生读时间隙,在讯时间隙在T1时刻后T2时刻前有

2017-10-18 16:39:00 31

31 [第11讲] SPI总线(85分钟),由何强主讲.本课主要讲解:(1).SPI总线介绍;(2).SPI总线的通讯时序;(3).STM32中的SPI控制器;(4).FLASH AT45DB161D的操作;(5).STM32中的SPI控制器的寄存器详解;(6).SPI的库函数详解;

2016-10-09 16:08:12 1380

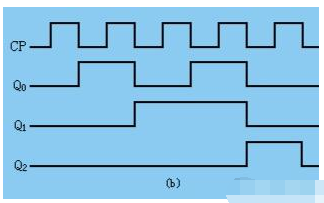

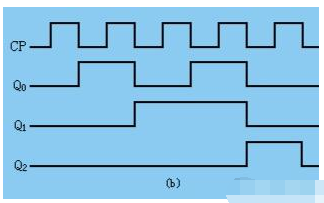

1380 时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。如电子技术中的触发器、定时器、计数器等均用时序图来描述其工作原理。在plc顺序控制设计法编制梯形图程序时往往是先画出时序

2017-10-23 08:40:45 84666

84666

I2C总线的结构、工作时序和模拟编程

2017-10-24 14:34:20 13

13 《Linux设备驱动开发详解》第15章、Linux的I2C核心、总线与设备驱动

2017-10-27 11:19:25 8

8 时序信号监测设备主要用于飞行器火T品信号、时序指令等信号的监测,是飞行器地面测试的重要组成部分。针对该设备对便携性、可靠性要求较高的特点,采用基于PXI总线的测试技术的一体式设计,充分考虑各种故障

2017-11-07 10:10:07 13

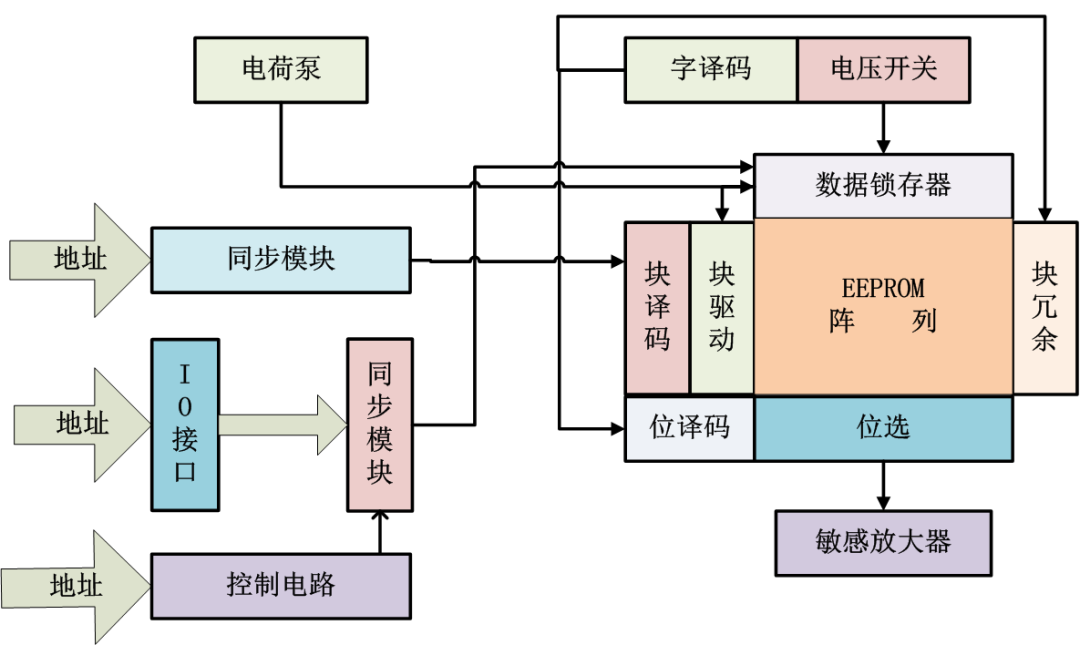

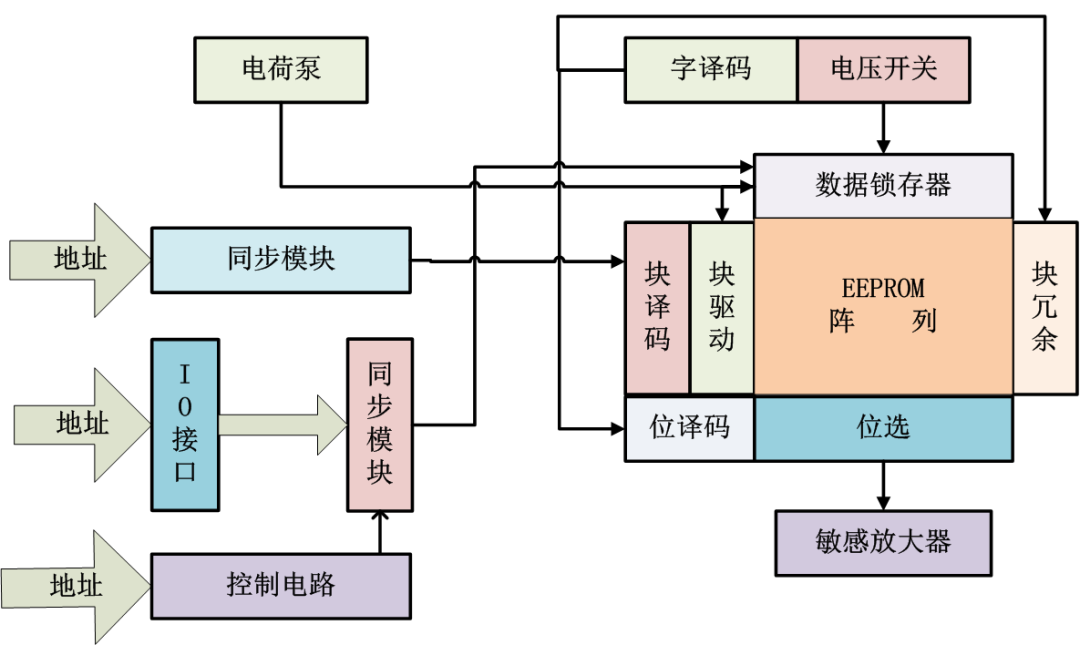

13 AT24C02是由ATMEL公司提供的,IIC总线串行EEPROM(electronic eraser programmer read only memory),其容量为2kbit(256B),工作电压在2.7v“5.5v之间,生产工艺是CMOS。

2017-11-16 14:29:04 11599

11599

本文首先介绍了CAN总线的总体结构,其次介绍了汽车CAN总线数据传输系统构成及工作原理,最后介绍了汽车CAN总线故障产生的原因以及用万用表测量诊断CAN总线方法详解。

2018-04-25 08:54:18 145063

145063

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2019-05-12 09:10:33 10860

10860

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片

2019-06-16 10:42:15 13406

13406

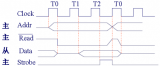

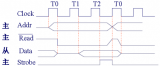

操作时序(timing):各信号有效的先后顺序及配合关系

2019-06-24 16:21:45 10207

10207

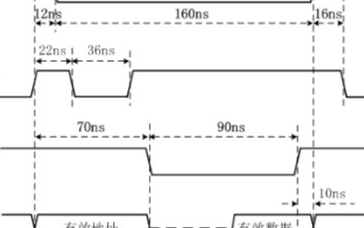

的数据读写周期。 EM335x总线周期读写时序如下: EM335x精简ISA总线读时序 EM335x精简ISA总线写时序 从上面的总线时序可知,可用ADV#信号对数据地址总线进行锁存,从而分离出单纯的地址总线信号。具体的实现电路如下: 由此我们就获得了精简ISA总线的所有信号: 8位数

2020-01-17 10:20:40 1108

1108

CANOpen系列教程04_CAN总线波特率、位时序、帧类型及格式说明

2020-03-06 16:18:58 7113

7113 在分布式测温系统中应用了大量的新型传感器DS18B20,DS18B20是单总线数字温度传感器其硬件接线简单,但时序非常复杂。要实现温度的正确读取,既要有对DS18B20的ROM操作命令,又有一些功能

2020-04-28 09:43:27 4366

4366 实上计算机的标准总线。其所以能在各类总线中脱颖而出,是因为其具有传输速度快、支持无限猝发读写方式、支持并行工作方式、独立于处理器、提供4种规格、数据线和地址线采用了多路复用结构、支持即插即用功能等特点。本文重点介绍了PCI总线的写周期的时序波形的测量技术及分析方法,给出了时序波形的分析结果。

2020-08-03 10:17:51 1541

1541

这里说的这个时间是以后学习中的关键,在时间的理解上,要考虑到另一个事情——先后,或者专业一些,叫作时间顺序——时序。

2021-02-07 17:52:00 4376

4376

RS总线集成电路在航空航天及工业控制领域具有广泛的应用,随着集成电路硬件木马的检测成为研究热点,作为总线硬件木马研究领域的分支,其设计越来越受关注。在常规时序型硬件木马的基础上,针对RS232总线

2021-03-19 17:19:26 34

34 书接上回-《串行总线技术(一)-串行总线结构(以PCIe为例)》《串行总线技术(二)-串行总线中的先进设计理念及SerDes/PMA介绍》,今天详解SATA协议。 简介SATA(Serial

2021-11-01 10:53:58 8354

8354 IIC的使用IIC总线简介IIC通信时序IIC总线寻址IIC总线简介1、IIC总线是一种由PHILIPS公司开发的两线式串行总线2、IIC在硬件上是时钟总线SCL和数据总线SDA两条线构成3、器件

2021-12-04 16:06:09 12

12 的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,...

2022-02-11 15:41:09 28

28 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 3462

3462

在详解CAN总线:CAN总线报文格式—数据帧文章中,讲解到仲裁段。仲裁段用于写明需要发送到目的CAN节点的地址、确定发送的帧类型(当前发送的是数据帧还是遥控帧),并确定发送的帧格式是标准帧还是扩展帧。

2022-10-25 14:00:18 1632

1632

本篇介绍了UML时序图的基础知识,并通过visio绘制一个物联网设备WIFI配网的UML时序图实例,来介绍UML时序图的画法与所表达的含义。

2023-05-16 09:09:22 1229

1229

时序:字面意思,时序就是时间顺序,实际上在通信中时序就是通信线上按照时间顺序发生的电平变化,以及这些变化对通信的意义就叫时序。

2023-07-26 10:06:03 1644

1644 CAN控制器根据两根线上的电位差来判断总线电平。总线电平分为显性电平和隐性电平,二者必居其一。发送方通过使总线电平发生变化,将消息发送给接收方。 显性电平对应逻辑 0,CAN_H 和 CAN_L

2023-10-27 14:55:28 1008

1008

电子发烧友App

电子发烧友App

评论