总线空闲状态 I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器

2017-11-21 15:09:05 24156

24156

上一篇文章简单讲解了什么是AMBA总线,简单来说,AMBA总线是一系列协议。定义了适用于不同场景的总线家族。今天我们就来将AMBA总线中最简单的APB总线。

2024-01-02 11:37:04 773

773

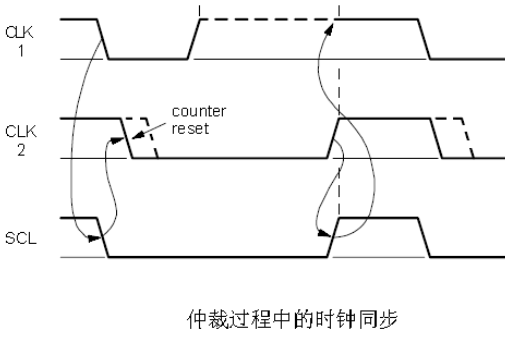

I²C总线在嵌入式系统中很常见,今天就来给大家讲讲I²C总线的时序。

2024-02-23 09:47:10 523

523

本帖最后由 mr.pengyongche 于 2013-4-30 02:59 编辑

16550兼容的UART,可以连接APB总线[url=www.0404.cc]

2012-08-10 18:10:18

APB (advanced peripheral bus) 外围设备总线一、DMA介绍1、DMA传输主要特性具有12个独立的可配置的通道(请求)。支持存储器及存储器间的传输,外设与存储器、存储器

2021-08-20 07:05:32

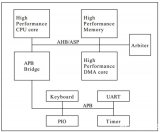

一、概括 首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。 南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率高

2021-08-20 06:18:24

一、概括首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率高

2021-08-23 07:34:30

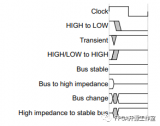

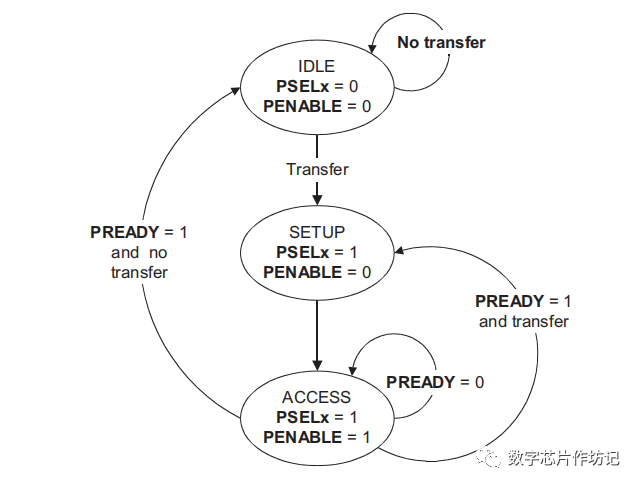

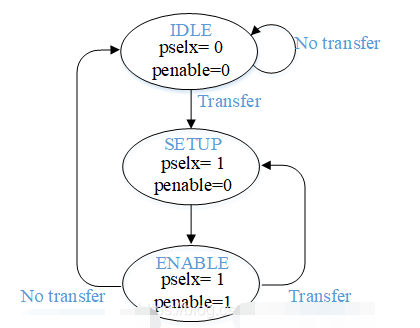

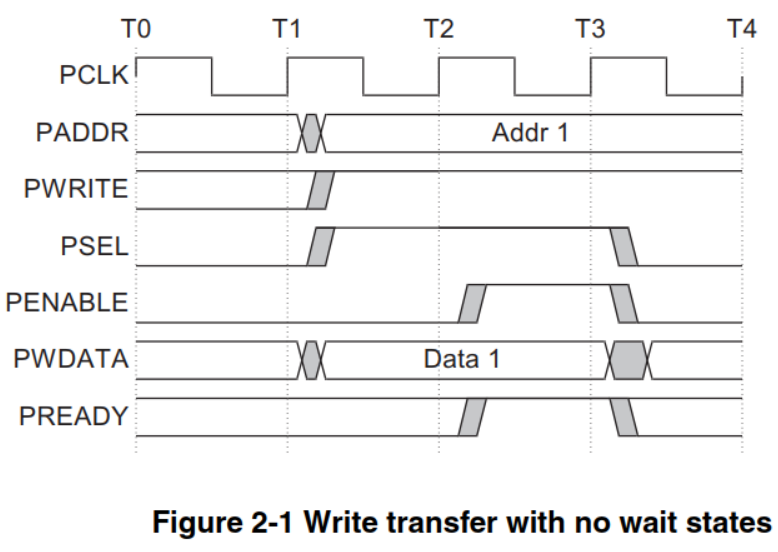

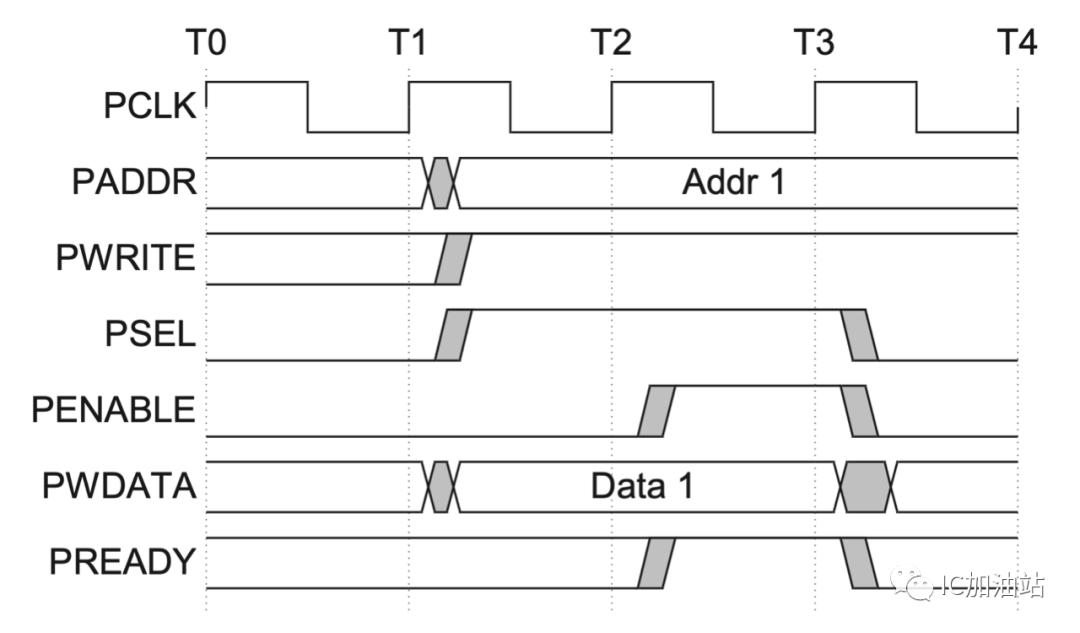

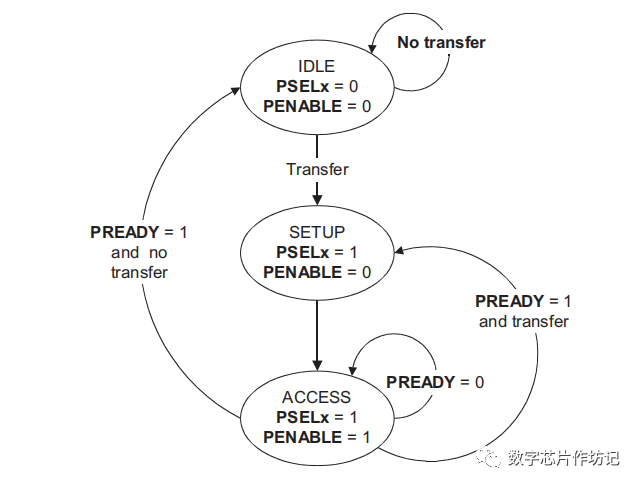

PREADY拉低,则读传输会延长。下图是AMBA APB的工作流程IDLE - 这是APB的默认状态。SETUP- 当需要传输时,总线进入SETUP状态,其中相应的选择信号PSELx被置位。 总线仅在

2022-04-07 10:18:24

信号传输总线技术分类按传输信息种类:总线可分为数据总线DB(DataBus),地址总线(AddressBUs),控制总线(ControlBus)按数据传输方式:并行总线(每个信号都有自己的信号

2022-02-16 07:53:28

1、AHB传输的时序图分析正文1:AHB章节最后再复习一遍多主机的概念:总线是被总线上所有的部件所共享的一组通路(连线),对于支持多主机的总线,如果某一个主机想要与其他的部件进行通信(获得

2022-06-09 17:45:33

HBUSREQ 信号为高一直到突发传输中的最后一次传输的地址传输相位发起之后。这将意味着如果倒数第二次传输是一个零等待状态,那么主设备可能会在未定义长度突发传输之后还被授予总线都多一次额外的传输。对于定长

2022-06-08 16:20:29

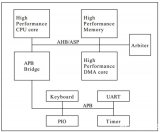

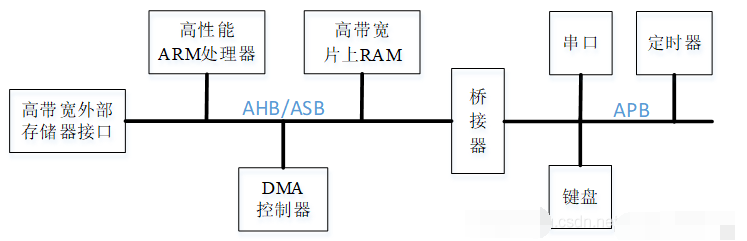

AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

2019-10-17 08:05:22

1、AHB系统总线分为APB1(36MHz)和APB2(72MHz),其中2>1,意思是APB2接高速设备;2、Stm32f10x.h相当于reg52.h(里面有基本的位操作定义

2021-08-05 07:13:06

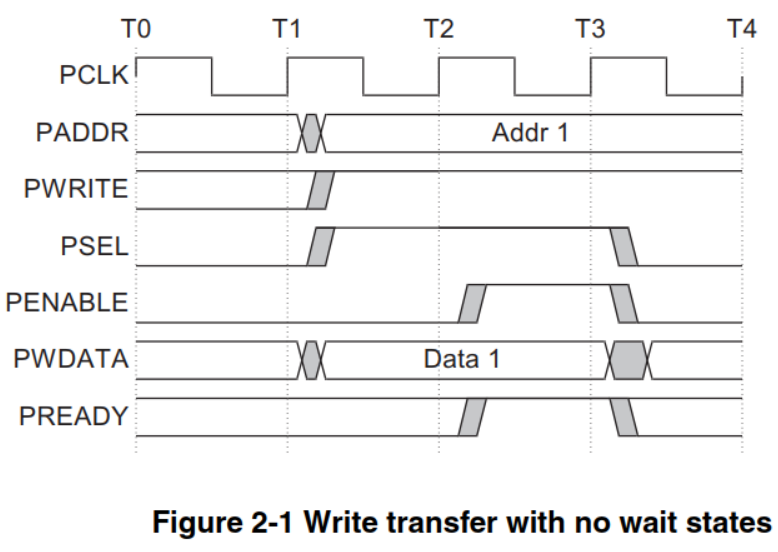

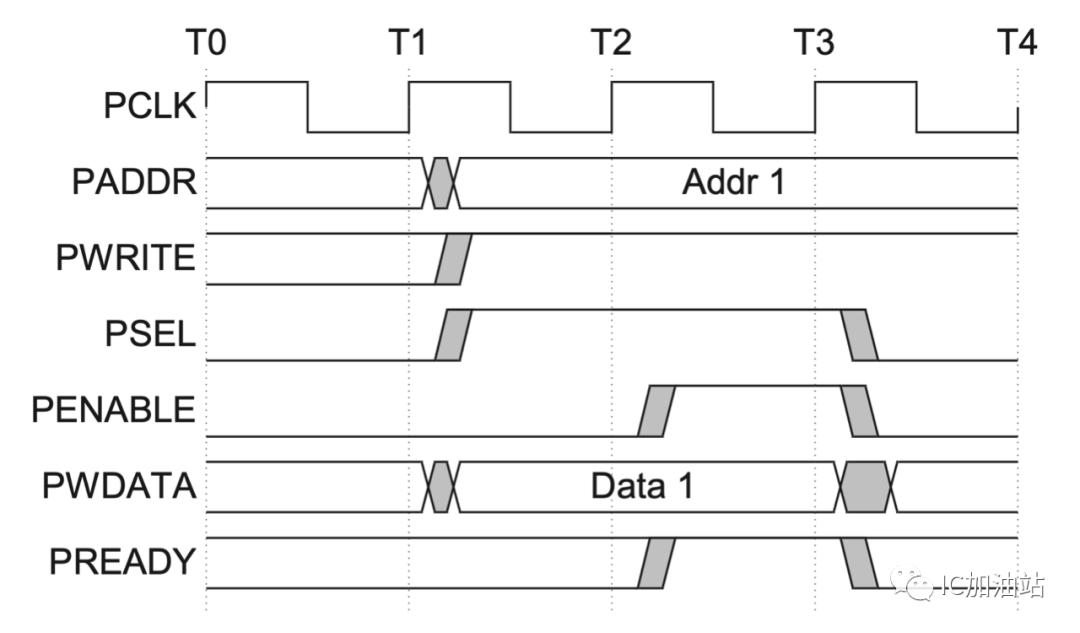

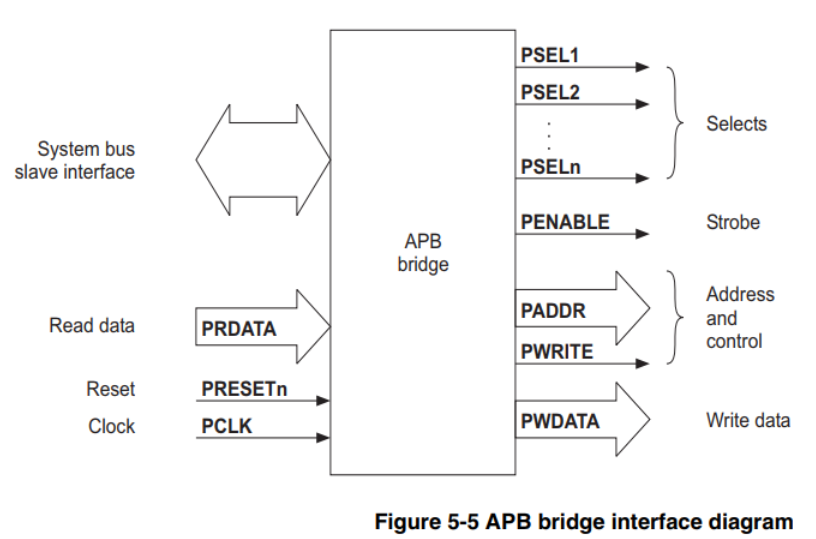

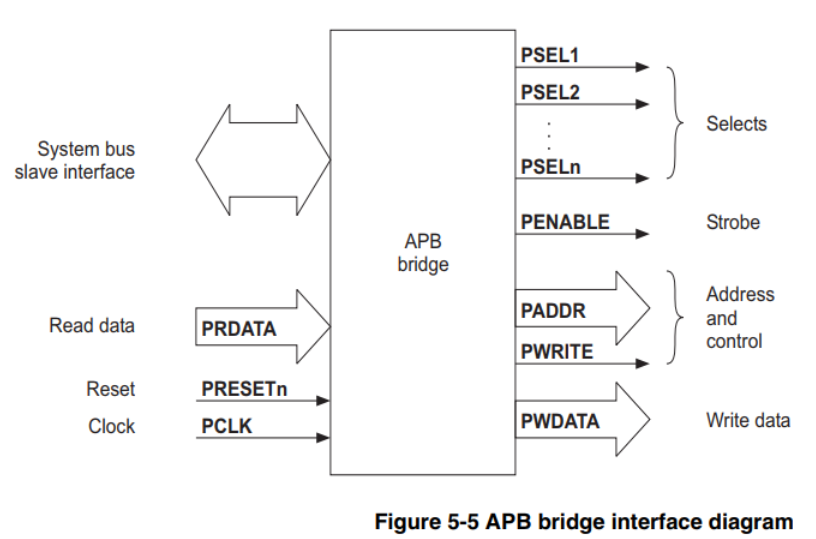

有效。 PADDR 地址总线。 PSELx 从设备选择。 PENABLE APB传输选通。 PWRITE 高为写传输,低为读。 PRDATA 读数据总线。 PWDATA 写数据总线。 接口信号定义如下:

2022-04-07 10:03:19

STM32菜鸟学习手册——1、AMBA、APB、AHB简介芯片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构

2022-02-17 07:18:33

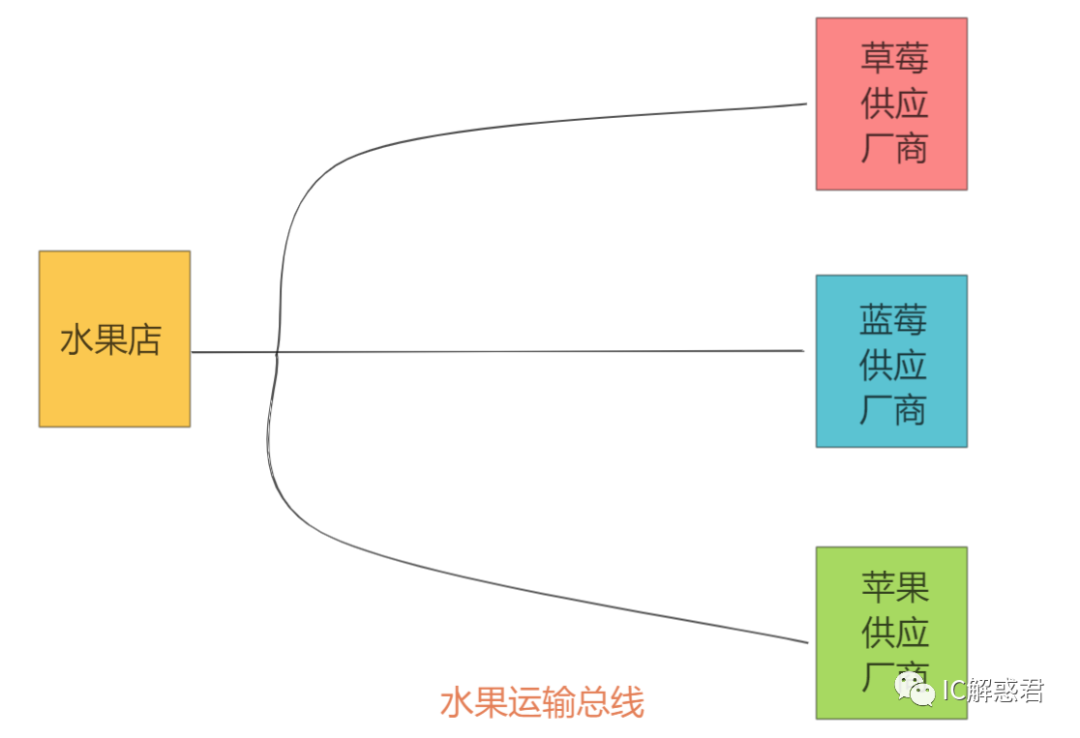

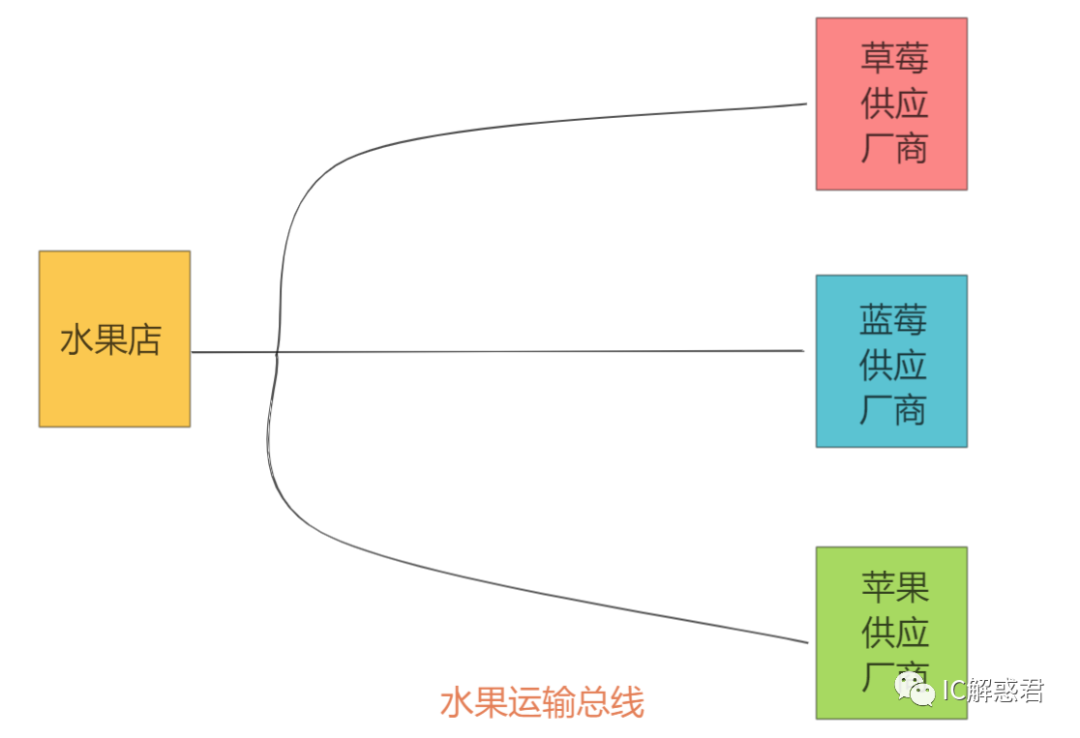

1、漫谈AMBA总线-APB首先考虑一下以下的场景:概念1: 主机(Master)订单的发起只能由水果店发起,所以水果店在这条水果运输总线里面运输水果占有主动地位。类比:在APB总线里面,数据的传输

2022-06-07 16:14:15

, ASB, APB);Qchannel文章目录1 AMBA总线2 AHB2.1 一个典型的基于AHB的微控制器2.2 AHB总线互联结构:中心选择器连接master与slave2.3 AHB的特性3 APB4 AHB和APB的区别与联系4 Q-channel1 AMBA总线内容来源:维基百科词条-Ad.

2022-02-09 07:46:07

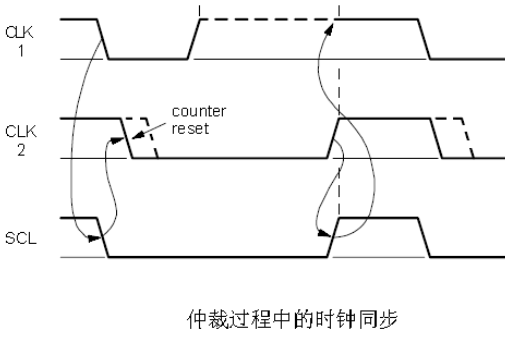

通过足够的空闲时间(“相位缓冲段”)来补偿。 由于CAN协议使用非破坏性的位总线仲裁和显性应答位,信号从发送器传输到接收器再返回到接收器必须在一个位时间内完成。因此除了保留用于同步的时间外,还需要

2016-08-15 15:59:45

CS1237无法正常读配置和写配置问题。图1读配置时序图,如附件所示。图2单片机管脚未连接AD芯片,时序图。通过对比两个时序,发现数据总线被AD芯片强制拉低了。这种芯片使用时,需要主控芯片有推挽输出模式强制拉高总线,弱上拉类型芯片该如何使用这个芯片??

2020-11-27 10:18:20

关于对DHT11单总线时序图的理解最近上网买了一个单总线的DHT11温湿度传感器,看了一些代码,这是自己的理解,并记录。DHT11数字温湿度传感器资料DHT11数字温湿度传感器是一款含有已校准

2022-02-16 07:03:14

。启动信号 在时钟线SCL保持高电平期间,数据线SDA上的电平被拉低(即负跳变),定义为I2C总线总线的启动信号,它标志着一次数据传输的开始。启动信号是一种电平跳变时序信号,而不是一个电平信号。启动信号

2018-06-14 15:00:51

物理层的连接可以说是非常简单,这也是它最大的优势,原理就是通过控制SDA和SCL线的高低电平时序,来产生I2C总线协议所需要的信号进行数据传输。在总线处于空闲状态时SCL和SDA被上拉电阻拉高,保持高电平

2020-08-25 11:16:05

0x01:iic简介I2C(Inter-Integrated Circuit)总线是由 PHILIPS 公司开发的两线式==串行总线==,用于连接微控制器及其外围设备。I2C 总线只有两根双向信号

2022-07-04 11:23:01

配合实现,传输速率包含标注准(100kps)、快速(400kps)、高速(3.4Mbps)三大类。2. IIC总线时序启动时序:当SCL为高电平时,SDA下降沿,表示启动。...

2021-11-29 06:20:06

IIC时序理解IIC 的特征:两条总线:串行数据总线(SDA)和串行时钟总线(SCL)数据有效性规定:IIC总线在进行数据传输时,SCL在高电平区间,SDA上的电平必须保持稳定SDA的数据的高或者

2022-01-07 06:05:52

时序图7.0 ISA信号用法8.0 ISA连接器引脚9.0 PC/104总线连接引脚[hide][/hide]

2009-05-25 01:13:56

IN:复位信号。用来迫使所有PCI专用的寄存器、定序器和信号转为初始状态。2.地址和数据信号 AD[31::00]T/S:地址、数据复用的信号。PCI总线上地址和数据的传输,必需在FRAME#有效期间进行

2012-04-06 14:37:24

了可连到总线上的器件数量。3、SPI时序分析在SPI传输中,数据是同步进行发送和接收的。数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。然而,最常用的时钟设置

2011-10-18 10:27:05

的128*64的OLED显示屏为例。下图为OLED的外观图。二、SSD1306芯片的IIC时序图这里我们需要看清楚START信号和STOP信号。关于时间,芯片的数据手册也有说明。...

2022-02-18 07:09:46

/APB1桥后就可以访问APB1各类外设,而TIM5就是挂在APB1总线上的外设之一。咨询者的问题基本上靠看上面几幅图可以得到答案。这些图很重要,很多信息用图描述也很直观明了。各技术手册里的插图往往大有

2021-05-16 06:00:00

以下是USB底层信号的一些定义及时序图,虽然很简洁,但能理解后,对后续的USB学习是很有帮助的,特推荐给大家!BTW,本月(4月20号周六)在深圳有一场很接地气、很容易入门的USB线下、小型技术交流

2019-04-08 16:30:26

详解-SPI接口在模式0下输出第一位数据的时刻 SPI接口在模式0下输出第一位数据的时刻 SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。图1中表现了这四种时序, 时序

2018-07-06 07:24:25

9-7 所示。• 同步段:在这段时间内,完成总线上各个节点的同步,需要一个跳变沿。• 传播段:这个时间段是指网络上传输的延迟时间,它是信号在总线上传播时间、输入比较器延迟和输出驱动器延迟之和的两倍

2018-12-17 11:13:33

是APB2总线(2)通用定时器timer2timer5,通用定时器timer12timer14以及基本定时器timer6,timer7的时钟来源是APB1总线从STM32F4的内部时钟树可知,当

2021-08-12 07:46:29

LCD1602的数据控制时钟信号,利用该信号的上升沿实现对LCD1602的数据传输。7~14脚:8位并行数据口,使得对LCD1602的数据读写大为方便。现在来看LCD1602的操作时序:在此,我们可以先

2017-12-13 14:47:53

,即执行一条指令所需的机器周期。三、时序单片机时序是指单片机执行指令时应发出的控制信号的时间序列。这些控制信号在时间上的相互关系就是CPU的时序。它是一系列具有时间顺序的脉冲信号。CPU发出的时序有两类

2018-07-21 16:38:31

是INTEL总线,6800总线也就是MOTOROLA总线。从这两个时序图上,我们看到的区别恐怕主要是读写选通的区别。INTEL总线分别使用读选通信号RD#和写选通信号WR#两个信号的低电平状态来表示当前处于

2016-11-26 17:10:43

,然后开始传输。解码器对放置在总线上的地址进行解码,并选择一个从机。从站将响应发回主站,然后进行数据传输。图3.AHB信号与ASB信号的比较先进的外围总线APB是用于低频系统组件的简化接口。修订版2通过

2020-09-28 10:16:11

APB slave模块只是对一些控制和状态寄存器进行读写,是无等待传输,同时不生成传输错误信号。对不同的寄存器做了地址分配,其中status32寄存器只读然后我们在Testbench里例化APB slave和一个APB master 模型,对该APB slave模块进行验证。

2022-04-07 10:10:03

十分严重注意的是,时序图里各个引脚的电平变化,基于的时间轴是一致的。一定要严格按照时间轴的增长方向来精确地观察时序图。要让器件严格的遵守时序图的变化。在类似于18B20这样的单总线器件对此要求尤为严格

2014-05-05 21:04:09

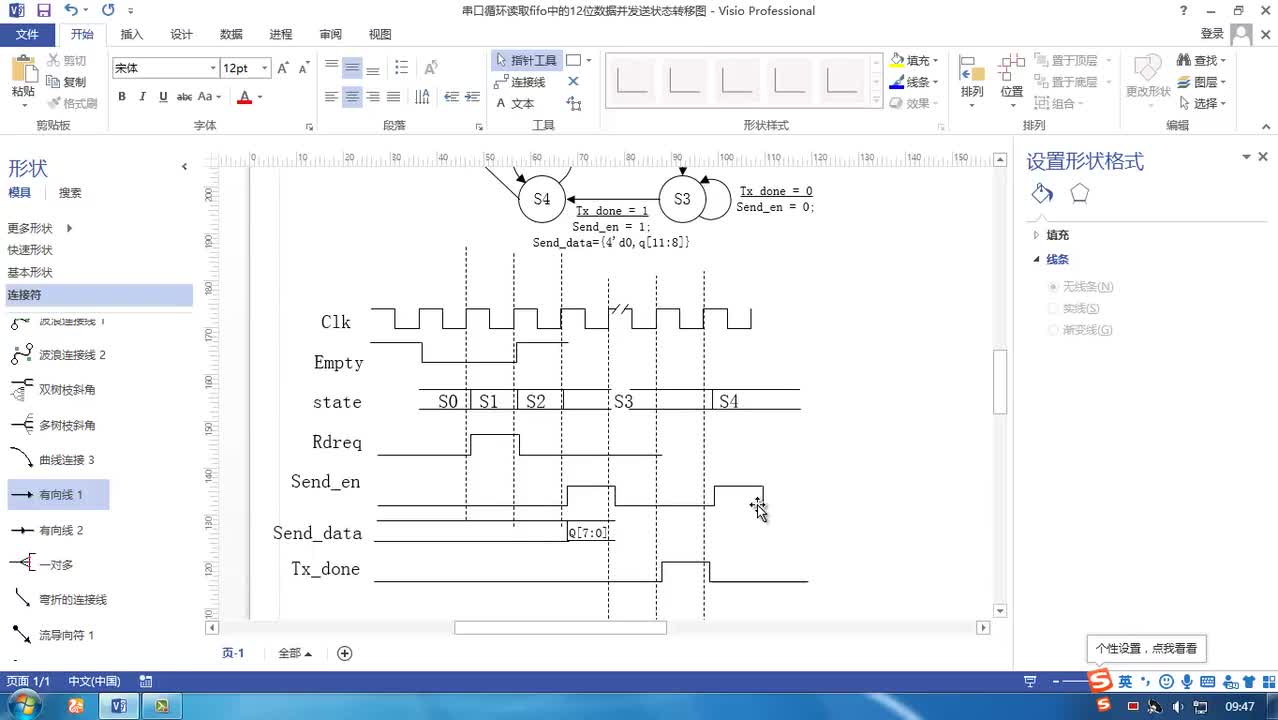

UART内部可划分为哪几个模块?这些模块有什么功能?基于APB总线的UART接口软核该如何去设计?

2021-06-18 08:20:15

访问不支持突发传输,总线时序和情形(3)一致;而内存访问支持突发传输,情形(3)和(4)的时序均会出现。用户应用可以通过Ready和Term信号不同的输入组合来控制状态机的状态转移,如表4所示。但是在

2019-05-29 05:00:02

实时信号处理的需要,用FPGA实现了多DSP信号处理模板局部总线和基于标准VME总线的计算机进行通信的接口设计。 2 VME总线的功能特点 VME总线系统的功能结构可以分为4类:数据传输总线(DTB

2019-04-15 07:00:07

问个问题,拿过来一个芯片datasheet,怎么由它的时序图把程序写出来? 我看过一些芯片的时序图,懂是可以懂得,但再看程序,里面定义了很多函数,向I2C总线结构的程序,还有开启和关闭I2C,类似这种。。。能否只从时序图直接写出它的程序? 路过的朋友可以探讨下并留下你的宝贵建议,谢谢。

2013-12-17 10:10:57

对Bank进行预充电,在此期间所有的Bank处于空闲状态。预充电之后会有至少两个自刷新,完成自刷新便可以对SDRAM进行模式寄存器配置。图1 SDRAM初始化时序 SDRAM模式寄存器所控制的操作参数:地址

2020-01-04 19:20:52

信号的上升沿实现对LCD1602的数据传输。7~14脚:8位并行数据口,使得对LCD1602的数据读写大为方便。LCD1602的操作时序这有两个写时序:① 若要写指令字,设置LCD1602的工作方式

2019-01-01 22:29:38

想写一个apb总线模型,时序也已经完成,就是读操作task这块,给定义成输入信号的prdata信号赋值时出错,根本无法驱动该信号。写了一个apb_bfm.v文件,外面没有挂接任何设备。

2019-03-07 12:30:53

要用verilog写一个APB总线,在这个上面挂载一个串口,现在有个疑问,APB总线时钟比较快,而串口的发送速率比较慢,那么在APB总线完成一次执行的话,两个的速度要怎么匹配呢?例如:APB三个状态

2019-01-22 23:57:10

我已经了解到proteus中VSM Logic Analyser 可以同时分析多个端口的电平变化,但总线周期时间太短,即便只有一条指令,也包含许多总线周期,如何才能 记录下总线周期内各个端口的电平变化,得到时序图?

2015-03-13 19:42:47

数据,是不是肯定会出现fifo为空的情况,这时候需要等待一段时间,直到fifo给APB总线发送了可读信号,APB总线才能够读取数据。那么问题是:APB执行过程只有两个周期,只要APB总线发生读操作,fifo很快就会空了,那么fifo要如何工作,才能最大的优化uart和APB总线之间的连接呢?

2019-02-12 00:43:19

高速电路信号完整性分析与设计—时序计算引入:在数字电路中,从一个芯片发信息A到另一个芯片变成信息B,那么这个数字系统失败;如何保证信息不变?关键点,就是在传输过程的任意点都保持时序的正确性。时序概念

2009-09-12 10:28:42

ISA总线信号时序简介:1.0 ISA概况2.0 ISA文献2.1 ISA规范2.2 ISA书籍3.0 ISA结构形式4.0 PC/104结构形式5.0 ISA信号描述6.0 ISA时序图7.0 ISA信号用法8.0 ISA连接器引脚

2009-05-21 11:06:54 242

242 PCI总线传输的终止方式探析:探讨了PCI 总线传输的终止方式。PCI 总线的主设备和目标设备都可以终止PCI 传输。主设备和目标设备在终止一次传输的同时还以信号的电平组合告知主

2009-06-28 19:32:07 22

22 同步时序机状态加全模拟是同步时序机反设计的关键步骤。因时序机状态出现的频率不同,模拟分析的时间不等,有的太长,难以满足要求。本文在长期实践基础上提出了一种同步

2009-08-29 10:06:40 19

19 本文针对干涉成像光谱仪,详细分析了干涉成像光谱信号特征及其时序关系,研究了干涉成像光谱数据传输系统的关键技术,提出了使用CPLD 技术,设计基于微机PCI 总线的干涉成像

2009-09-01 08:21:37 17

17 介绍一种通过光纤传输USB(通用串行总线)信号的电路。电路将USB(通用串行总线)信号D+、D一的三种状态转换为发射激光的三种强度全亮、半亮、暗,并且通过光纤传输到对方激光

2010-12-13 16:05:22 27

27

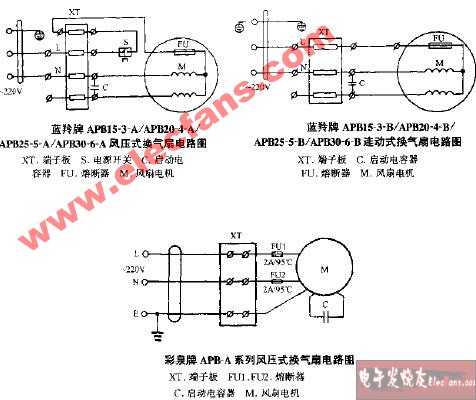

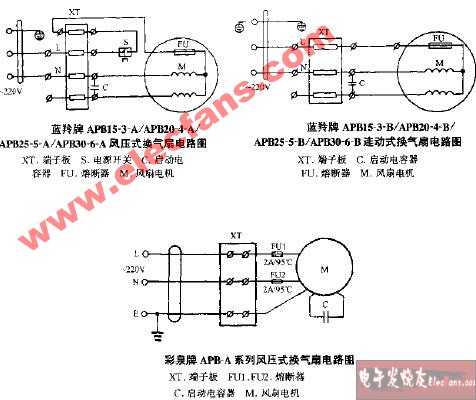

蓝羚牌APB15-3-A APB20-4-A APB25-5-A APB30-6-A风压式换气扇电路图

2009-02-27 21:22:22 1068

1068

蓝羚牌APB15-3-B APB20-4-B APB25-5-B APB30-6-B连动式换气扇电路图

2009-02-27 21:22:54 1128

1128

探讨了PCI 总线传输的终止方式。PCI 总线的主设备和目标设备都可以终止PCI 传输。主设备和目标设备在终止一次传输的同时还以信号的电平组合告知主设备其不同的终止状态。主设备启

2011-05-18 16:43:46 28

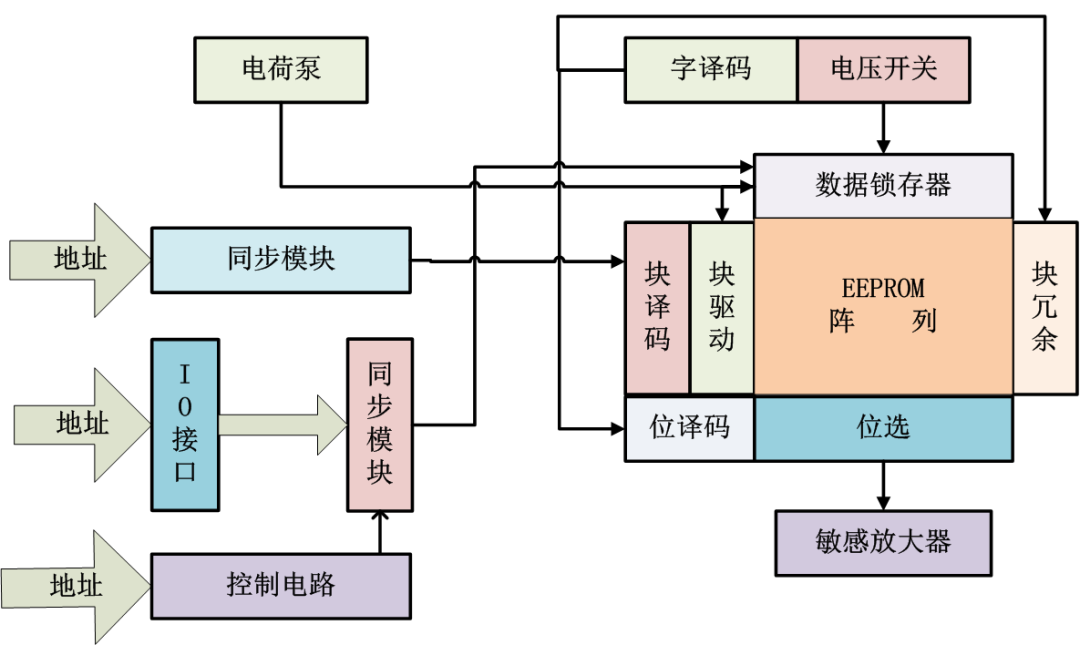

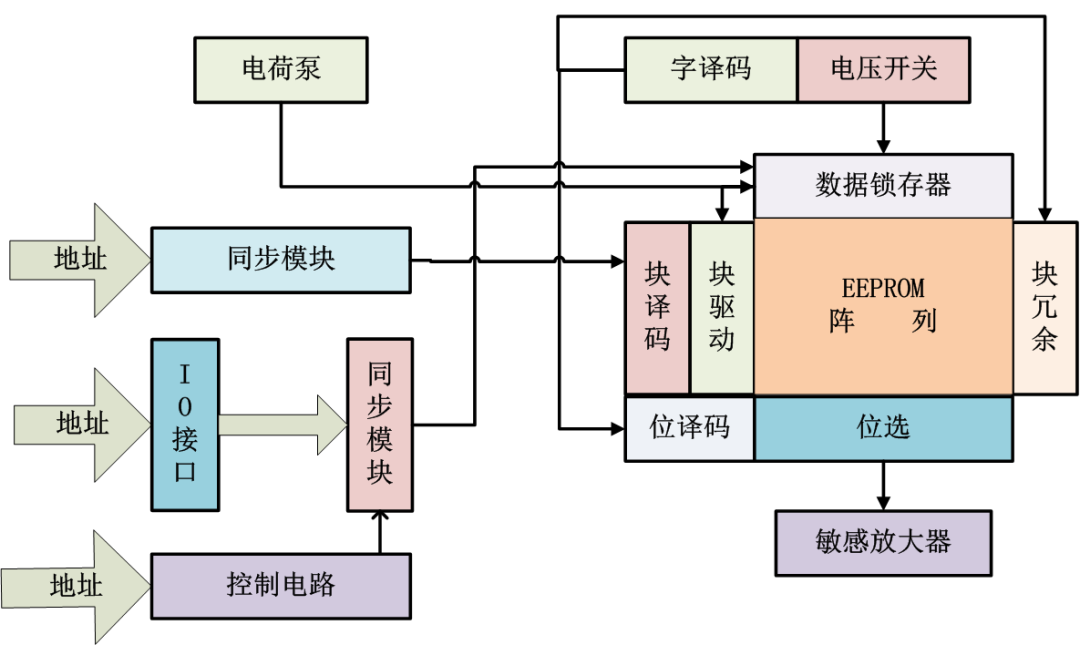

28 介绍了基于AMBA APB总线NandFlash控制器的设计,首先简单介绍了NandFlash的一些特点,然后详细介绍了NandFlash控制器的整体框架、具体功能及其内部的数据通路。该控制器通过ModelSim进行了仿

2011-11-03 15:22:06 54

54 24C02中IIC总线的应答信号(ACK)时序图分析,很好的单片机学习资料。

2016-03-21 17:30:06 93

93 I2C总线的结构、工作时序和模拟编程

2017-10-24 14:34:20 13

13 时序信号监测设备主要用于飞行器火T品信号、时序指令等信号的监测,是飞行器地面测试的重要组成部分。针对该设备对便携性、可靠性要求较高的特点,采用基于PXI总线的测试技术的一体式设计,充分考虑各种故障

2017-11-07 10:10:07 13

13 介绍一种通过光纤传输USB(通用串行总线)信号的电路。电路将USB(通用串行总线)信号D+、D一的三种状态转换为发射激光的三种强度全亮、半亮、暗,并且通过光纤传输到对方激光接收器再经相应电路恢复D+

2017-11-14 16:26:33 12

12 由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

2017-11-14 16:36:43 17155

17155

总线空闲状态:I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

2017-11-23 11:23:05 24558

24558

总线空闲状态 I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

2017-12-23 10:12:02 9395

9395

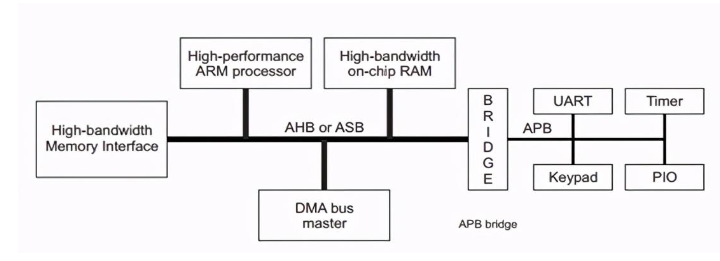

一个典型的基于AMBA 的微控制器同时集成AHB(或ASB )和APB 接口,如图2 所示。ASB总线是旧版的系统的总线,而新版的AHB 总线增强了对性能、综合及时序验证的支持。APB 总线通常用作的局部的第二总线,作为AHB 或ASB 上的单个从属模块。

2018-08-10 09:45:10 6975

6975

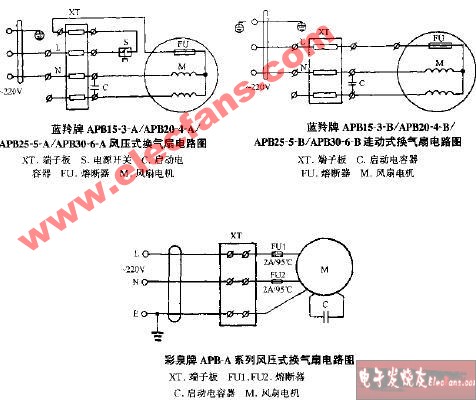

如图所示的电路为一能根据音频信号的强弱控制八路时序输出闪光状态变化快慢的灯饰电路。

2019-12-22 10:15:58 2727

2727

由于CAN协议使用非破坏性的位总线仲裁和显性应答位,信号从发送器传输到接收器再返回到接收器必须在一个位时间内完成。

2020-03-21 11:23:39 2224

2224 总线就像一条公路,公路上的车好比总线上的电信号;公路的大小和车流量就决定了公路的车流量,故总线的位宽大小和传输频率决定了一次传输中能够提供的最大速度。常见的总线类型有:

2020-07-21 17:38:18 4526

4526 APB(AdvancedPeripheralBus)是AMBA(AdvancedMicrocontrollerBusArcheticture)总线体系的一部分。相较于AMBA总线体系中的其他总线,APB总线具有低功耗,低复杂度的特征。APB总线主要应用于对性能要求不太高的低带宽外设接口。

2020-11-17 11:54:04 12017

12017

集成电路,设计一种基于可逆计数器的时序型总线硬件木马。采用Xiix公司的ISE软件在RTL层设计相应的RS232总线 Verilog代码,并在常规和可逆时序型硬件木马触发阈值呈等差递增的条件下进行 Modelsim仿真分析结果表明,在总线功能需求复杂和传输数

2021-03-19 17:19:26 34

34 电子发烧友网为你提供SPI总线协议介绍(接口定义,传输时序)资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-01 08:45:43 24

24 电子发烧友网为你提供STM32 APB1总线时钟配置问题资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-19 08:51:53 7

7 的,使用它连接到不需要 AXI 协议高性能的低带宽外设。 APB 协议将信号转换与时钟的上升沿相关联,以简化将 APB 外设集成到任何设计流程中的过程。每次传输至少需要两个周期。APB 可能相连的接口: • AMBA 高级高性能总线 (AHB) • AMBA 高级高性能总线精简版 (AHB-

2021-07-23 10:04:10 1911

1911

一、概括首先,说点不靠谱的,APB和AHB总线,我个人感觉这个类似于个人PC系统里的北桥和南桥总线。南桥总线上挂接的都是鼠标、键盘这些慢速的设备,北桥上挂接显卡等高速设备。南桥频率低,北桥频率

2021-11-26 10:51:04 10

10 连接到总线都是SCL连到一起,SDA连到一起4、任何器件都可以拉低总线的电平IIC通信时序IIC通信时序可分成4个部分:1、开始信号:在SCL为高电平时,SDA产生一个下降沿2、数据传输:在SCL为低电平时,SDA可以变化;在SCL为高电平时,读取SDA的状态3、应答信号:先拉高SDA,然后拉

2021-12-04 16:06:09 12

12 的低带宽外围设备需要AXI协议的高性能。APB协议将信号转换与时钟上升沿相关联,以简化将APB外围设备集成到任何设计流程中。每次传输至少需要两个周期。

2022-04-28 17:45:53 0

0 APB3是一个低功耗低成本接口。所有信号在时钟上升沿传输,每次传输需要两个时钟周期。

2023-03-31 17:26:21 1397

1397

V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。

2023-04-14 10:54:54 2764

2764 在APB总线里面,数据的传输只能由主机发起,其他部分响应主机操作。

2023-05-04 11:40:42 644

644

之前老李问过大家想看哪方面的知识,有不少同学提议老李写写总线,特别是AMBA的总线,所以老李决定从这期开始开始一个AMBA总线介绍的系列文章。AMBA总线主要包括三种最常见的协议APB, AHB

2023-05-04 14:53:12 1843

1843

实现一个在ARM中通过APB总线连接的UART模块(Universal Asynchronous Receiver/Transmitter),包括设计与验证两部分。

2023-06-05 11:48:38 953

953

APB(Advanced Peripheral Bus),外围总线的意思。该总线协议是ARM公司提出的AMBA总线结构之一,几乎已成为一种标准的片上总线结构。

2023-06-05 15:10:39 1036

1036

高级外设总线 (APB) 是高级微控制器总线架构 (AMBA) 协议系列的一部分。它定义了一个低成本接口,该接口针对最低功耗和降低的接口复杂性进行了优化。

2023-09-07 09:55:35 607

607

CAN总线是数字信号?还是模拟信号? CAN总线是一种数字通信协议,因此可以说是传输数字信号的。下面详细介绍CAN总线是如何以数字信号进行数据传输的。 CAN(Controller Area

2023-11-22 18:18:25 1294

1294 AMBA APB总线可以用在低带宽和不需要高性能的外设上(即低速且低频率的外设);可以将APB视作AHB的二级总线;

·低功耗(APB总线信号端口比较简单,复杂度低,低频工作环境等因素都可以

2023-11-29 15:19:38 265

265

之前的两篇文章给大家介绍了APB协议相关的知识点,并结合实际的代码给大家讲解了一下APB slave的设计。并说明了一下APB slave mux这个模块。 上一篇文章提到:通常而言,APB

2024-01-13 10:09:05 215

215

IC设计的时候,都应该像这样规划好各个模块的连接关系,确定好以后再写代码。该模块是一个 基于APB协议完成寄存器配置或读取的设计实例 。设计相对比较简单,但不失为一个很好的学习资料。 上面APB相关的信号都介绍过,这里不再重复介绍,其中的ECOREVNUM的意思是ECO revisi

2024-01-13 10:15:41 248

248

APB(Advanced Peripheral Bus) 作为高级外设总线是AMBA协议之一,也是最基本的总线协议。按照ARM官方定义,APB是一种低成本的接口协议,可以实现低功耗以及精简的接口设计,降低接口设计的复杂度。

2024-01-17 17:35:09 158

158

电路,并探讨时序电路中可能存在的状态循环。 首先,同步时序电路是指时序元件按照整个系统的时钟信号进行同步操作的时序电路。常见的同步时序元件有锁存器和触发器。锁存器可以将输入信号“锁定”,在时钟上升沿或下降沿将输入信

2024-02-06 11:22:30 291

291

电子发烧友App

电子发烧友App

评论