这里以Renesas提供的RZ/T2M工程样例“RZT2M_EtherCAT_RSK_rev0100”为例对PHY驱动的软件配置流程进行说明。

2024-02-20 12:18:21 852

852

本文主要介绍以太网Drive Side接口(MAC和PHY之间的接口),也被称为MII(Media Independent Interface),支持从10M到100G的不同应用场合,主要包括MII

2020-10-08 00:09:00 8774

8774

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-09-07 09:28:10 1263

1263

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-09-08 09:46:51 557

557

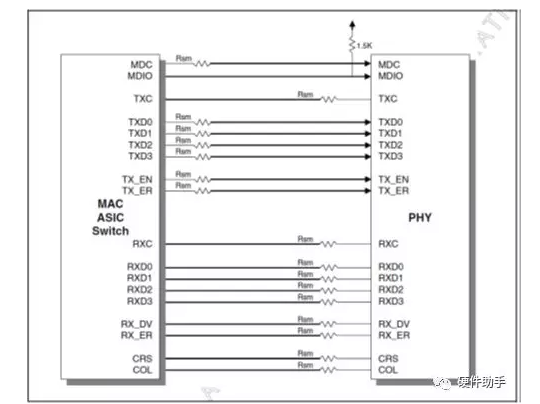

MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准."媒体独立"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作.它包括一个数据接口,以及一个MAC和PHY之间的管理接口.

2024-02-19 10:47:43 372

372

MII/RMII接口 100M以太网PHY SR8201F设计资料

2019-04-09 14:00:44

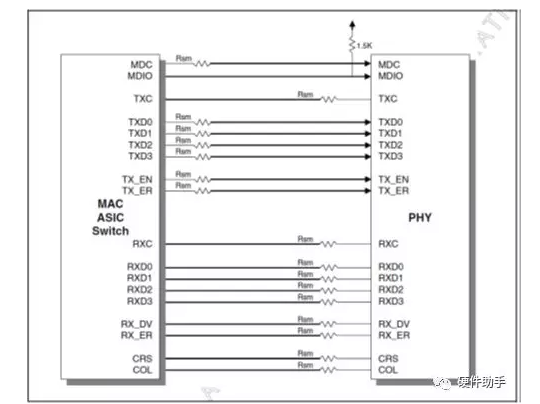

IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共

2018-05-12 12:50:21

了SR8201F,一颗和RTL8201F的管脚兼容的产品,针对原使用RTL8201F的客户,工程师不需要做硬件改版的动作就可以使用到我们性价比更高的SR8201F。SR8201F是一颗MII/RMII

2018-06-29 15:55:36

MII接口有何功能?RMII接口有何功能?MII接口和RMII接口对应的引脚有哪些?

2021-10-26 06:12:11

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到

2019-10-18 09:11:36

开发板使用MII接口,但是由于我们要使用串口,所以LAN8720接到6748的RMII接口。那么问题来了,开发板中初始化EMAC_initialize()函数内使用EMACPinMuxSetup

2019-08-27 11:12:07

以太网接口硬件设计中,现在CPU集成度越来越高,都会集成MAC,而对于硬件设计来说,只需要外接PHY Transceiver IC即可实现以太网通信,而PHY芯片(以百兆为例)外围电路基本如下所示

2021-11-11 08:38:40

作者:一博科技上周我们把MAC到PHY、PHY到PHY这两个子层之间的通信框架拎出来,把它们放在一个框图下,如下图所示:图1 MAC与PHY框架今天来讲讲这个PHY的内部、及其内部各个模块间的接口协议。具体内容可查看附件。

2018-01-19 18:45:29

作者:刘丽娟 一博科技高速先生团队队员PHY与PHY之间进行通信的接口称为MDI(Medium Dependent Interface,媒介专用接口)。媒介(Medium)有背板、Cable、光纤

2019-07-26 08:40:50

开发板的原理图:通过电路原理图可以看到接线方式是使用RMII接口模式接线的,因此接下来我们在配置PHY的时候注意要是用RMII。我们知道DP83848,以及任何一个PHY芯片,都是有5个bit...

2022-01-19 08:28:40

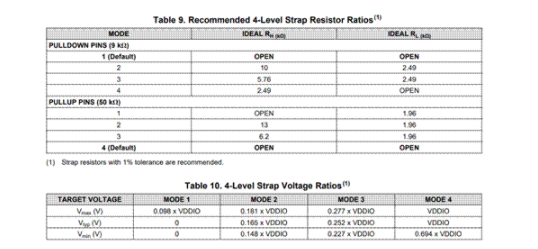

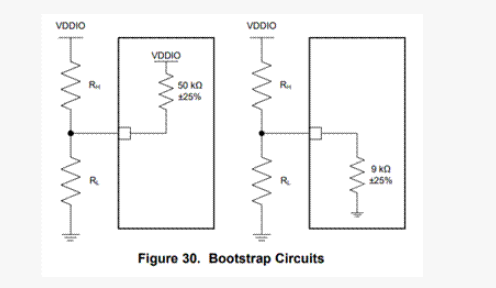

导语PHY芯片的初始化配置有硬件配置和软件配置两种途径,当系统上电之后默认采用硬件配置的模式,如需要更改配置,可以通过软件写寄存器的方式来更改模式。此处主要说明...

2021-07-23 06:19:34

各位好,最近有个研发产品需要用到PHY芯片,需求是连接 内置10/100M Ethernet MAC,接口是RMII和MII兼容的,但是市面上PHY芯片很多,应该怎样选型来选到合适的啊,还需要注意哪些参数?谢谢大家

2016-12-14 16:03:38

细说电流隔离低压差分信号传输 (LVDS)接口,涉及到串行数据传输的既有接口标准 (TIA/EIA-644)

2020-12-18 06:01:32

一文读懂接口模块的组合应用有哪些?

2021-05-17 07:15:49

, uboot 修改完毕,重新编译即可。 二、kernel里如何修改phy(单网络,rmii1接口)1.内核配置Device Drivers ---> Network device support

2018-04-04 10:17:43

基本概念在MIPI目前公布的协议中,有3类基于摄像头的接口,一个是前几年大行其道的D-PHY接口,一个是C-PHY接口,还有一个是M-PHY接口。D-PHY接口一般是1/2/4 Lane,每个

2021-07-29 07:21:11

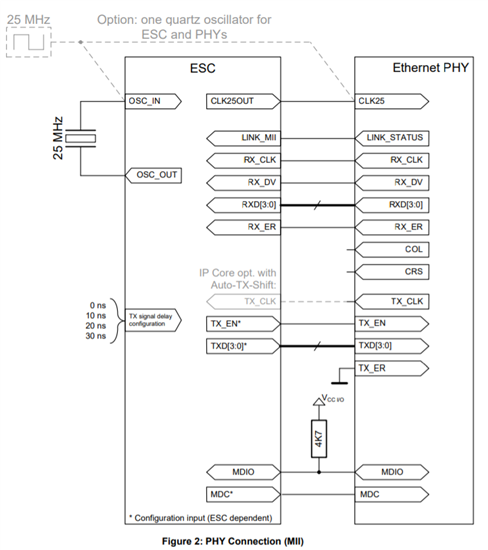

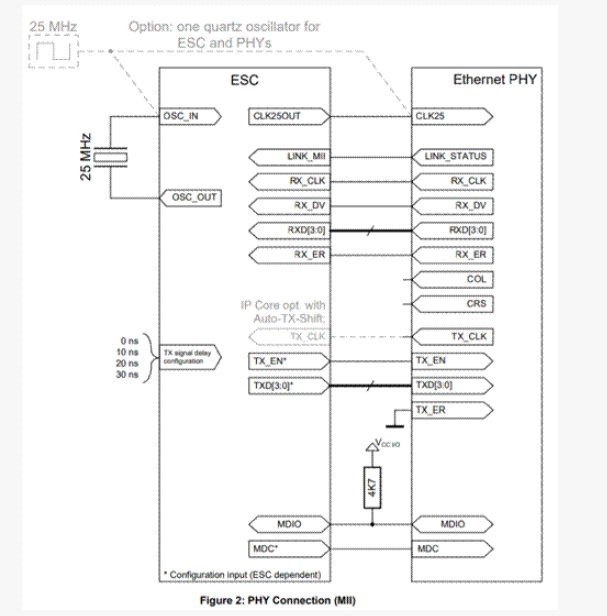

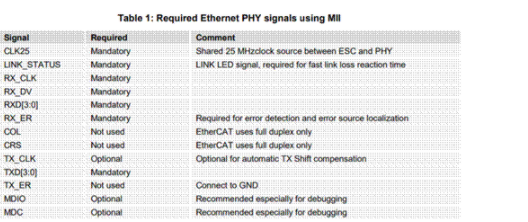

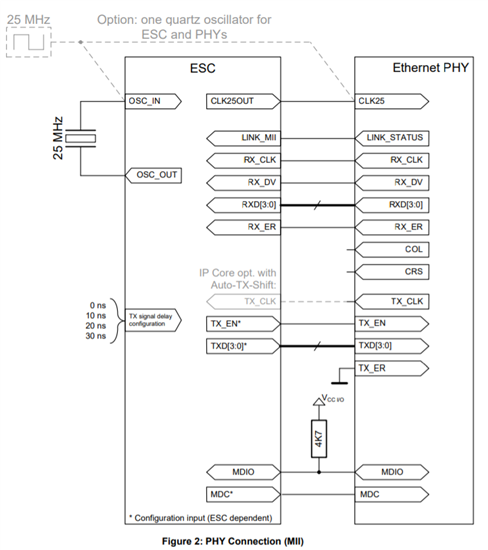

设备的传输延时,同时也会引入抖动,所以一般不建议在EtherCAT应用中使用,本文主要讨论PHY的MII接口的硬件配置。下图是ESC和PHY MII之间的连接关系的示意图。ESC和PHY之间的时钟必须保持一致。LINK_STATUS是一个LED输出信号…

2022-11-07 07:55:18

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以

2023-06-06 15:43:13

什么是MAC和PHY?MAC与PHY是什么关系?什么是MII/RMII/GMII/RGMII?

2021-09-27 07:46:54

USB 3.0/2.0等多种接口类型,内核USB驱动已经兼容这几种不同类型的USB接口,只需要根据实际的硬件设计修改对应的板级DTS配置,就可以使能相应的USB接口。 两个Type-C

2022-11-18 16:23:02

en_tx_lpi_clockgating;int has_xgmac;};设备树配置与解析// RK3568设备树配置gmac0: ethernet@fe2a0000 &

2022-09-14 16:58:21

我正在使用 S32K148 微控制器,它是否支持带 PHY 的 MII 模式?需要做什么设置才能在 MII 模式下工作?TX_CLK 和 RX_CLK 应该配置为 2.5MHz/25MHz 吗?

2023-04-17 08:43:10

我们使用的是 NXP 的以太网交换机,零件号是 SJA1105QELY。框图如下所示。

请求您对以下查询的输入:

我们想知道SJA1105QEL是否有内部电压电平转换器将PHY侧MII信号

2023-06-12 08:44:16

和RMII接口》,介绍了STM32以太网和外部PHY的所有接口。如果有同学对SMI,MII和RMII接口不熟悉,建议看一下上面提到的两篇文章,不然可能看不太懂下文。区域1:我们称为SMI接口,用于配置外部PHY芯片。区域2:是数据交换接口,也就是上面我们说的MII接口和RMII接

2021-07-29 07:47:55

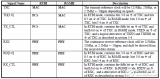

与 PHY 通讯。1. MII如图 1 所示,MII 接口标准定义了 16 跟信号线,根据功能将其可以分为 3 组(发送,接收,载波侦听和冲突监测),另外还有用于对 PHY 进行配置的 SMI 接口

2021-01-28 13:17:17

函数):PHY Address,(PHY ID代码中没看到),模式改为MII,GPIO管脚的配置。另外void LwIP_Init(void) 这个函数要修改吗?把程序下载到板子上,网口的绿灯和黄灯都是

2014-07-18 11:53:52

侦听和冲突监测),另外还有用于对 PHY进行配置的SMI接口。 发送 TX_CLK:MII接口需要25MHz的时钟(100Mbits传输速率时),当以 10Mbits的速率工作,PHY内部的电路会对

2014-11-19 18:20:12

支持媒体独立接口(MII)和精简媒体独立接口(RMII)。

•RMII是一种针数较低的替代方案,针对多端口应用低成本设计:

•用于调试的MII上的内部环回。

•用于PHY配置的MDC/MDIO

2023-09-11 07:20:19

支持媒体独立接口(MII)和精简媒体

独立接口(RMII)。

•RMII是一种针数较低的替代方案,针对多端口应用

低成本设计:

•用于调试的MII上的内部环回。

•用于PHY配置的MDC/MDIO

2023-09-06 07:30:29

在上篇文章《STM32网络之SMI接口》中,我们介绍了STM32网络控制器的SMI接口,SMI接口主要是用于和外部PHY芯片通信,配置PHY寄存器用的。真正网络通信的数据流并不是通过SMI接口

2021-08-05 07:01:43

接口与 PHY 通讯。1. MII如图 1 所示,MII 接口标准定义了 16 跟信号线,根据功能将其可以分为 3 组(发送,接收,载波侦听和冲突监测),另外还有用于对 PHY 进行配置的 SMI 接口

2021-08-10 11:28:38

am3352使用port1连接marvell6095,使用mii模式。管脚配置如下:

static struct pinmux_config mii1_pin_mux[] = [

["

2018-05-15 09:06:33

stm32总线接口有哪些,在上篇文章《STM32网络之SMI接口》中,我们介绍了STM32网络控制器的SMI接口,SMI接口主要是用于和外部PHY芯片通信,配置PHY寄存器用的。真正网络通信的数据流

2021-08-05 07:28:55

OSI 的 7 层基准模型中 PHY 属于第一层 ——物理层。PHY 是数据链路层的媒体访问控制部分和媒体的接口。PHY 对所有传输的数据只是进行编码转化,没有对有效数据信号进行任何分析或改变,但是

2021-03-25 11:26:24

(OSI) 模型的一部分。OSI 模型是通信系统内部功能的概念模型。在该模型中,介质接入控制 (MAC) 通过介质独立接口 (MII) 连接 PHY。PHY 将包含一个物理编码子层 (PCS)、一个物理

2022-11-21 06:04:29

我有一个使用 i.M6ULL 的设计。我需要它的两个以太网接口 (FEC1 + FEC2)。在我的板上,两个 FEC 都连接到 LAN8720A PHY。FEC1 具有 MDIO 地址为 0

2023-04-11 08:26:34

如何实现单片以太网微控制器?以太网MAC是什么?什么是MII?以太网PHY是什么?网卡上除RJ-45接口外,还需要其它元件吗?造成以太网MAC和PHY单片整合难度高的原因是什么?10BaseT和100BaseTX PHY实现方式不同的原因何在?什么是曼彻斯特编码?什么是4B/5B编码?

2020-12-28 06:22:47

。 • 时钟产生模块:产生 MII 接口的时钟信号,这个时钟信号需要满足外部 PHY 芯片对时钟的要求。• 输出控制模块:因为 MII 连接到外部 PHY 的数据线实际只有一根线,输出控制模块需要将输出、输入

2018-12-29 10:59:10

使用AM335X核心板自制底板,配置的mii2+dp83848,未使用mii1。 能够连接到phy并配置为模式100/Full,但是ping不通,rx有数,不知道原因?

2022-01-12 07:24:35

的框图,MII接口PHY用的25M时钟,RMII接口用的50M时钟,这个为什么要这么用呢?

方案二:OMAPL138=>EMIF=>硬件协议栈芯片=>PHY

疑惑#1

2018-06-21 07:09:52

/ PHY以太网端口端口1/2。端口0提供两个MII端口连接器,支持以下功能:支持外部MII- / RMII- / Turbo MII的MAC,LAN9303处于PHY模式,通过板载40针公MII连接器

2020-05-18 09:30:22

EVB-LAN9353,评估板,利用LAN9353提供具有双RMII或单MII / RMII / Turbo MII接口的全功能三端口以太网交换机。 EVB-LAN9353通过板载RJ45连接器提供

2020-08-17 09:39:14

我在 MII 模式下使用 KSZ9021GN PHY。由于供应链问题,我们不得不求助于此 PHY。(Cube MX 说我不能使用 GMII 模式)。我遇到了这个明显常见的问题:[15.650981

2022-12-26 10:12:45

如何配置clause 45接口的phy外设?有没有相关的例程?我搜索到的官方例程好像都是用的clause 22 MDIO.

相对于clause 45来讲,我下面的理解是对的吗?

MAC MDIO

2024-01-18 08:57:19

协商? - 这个TEMAC核心是否支持autoneg?在此先感谢。任何帮助都会很棒PS:我必须使用没有可选管理接口(MDIO)的MII接口。

2019-11-05 09:46:20

某些phy芯片同时支持rmii和mii接口,比如ksz8863,那么工作的时候是自动识别连接方式吗?

2019-09-26 04:13:47

MII接口的管脚定义有哪些?怎样通过MII或者RMII接口进行网络通信呢?

2021-10-28 08:03:00

型的USB接口,只需要根据实际的硬件设计修改对应的板级DTS配置,就可以使能相应的USB接口。RK3399 SDK DTS的默认配置,支持Type-C0 USB 3.0 OTG功能,Type-C1

2022-05-20 14:51:07

我正在使用自定义 P2041 板。有两个 SGMII PHY,但此 PHY(作为硬件)没有 MDIO 总线。简而言之,我无法使用 MDIO 总线配置 PHY。但我正在使用 TBI 块来获取 PHY

2023-05-04 06:00:03

大家好,我将使用CYYSUB3610。我有个问题。是否有可能禁用内部PHY并直接使用MII或RMII接口与芯片?在我们的应用中,使用它更有效。溴穆拉特特米兹

2019-09-24 07:04:08

MAC是什么?RMII是什么?PHY又是什么?

2021-10-27 08:00:07

1. 有MII/RMII接口、且内置MAC的单片机,如 STM32F407、STM32F107方案:外置PHY,且内部程序要运行TCP/IP协议栈PHY芯片推荐列表:LAN8720、LAN8742

2021-08-05 06:39:42

怎样去设计一种基于MII和RMII接口的STM32网络电路呢?有哪些操作步骤呢?

2021-11-01 06:27:02

mac总线,mac接phy,phy接网线(当然也不是直接接上的,还有一个变压装置).

PHY和MAC之间是如何传送数据和相互沟通的.通过IEEE定义的标准的MII/GigaMII(Media

2023-06-26 07:04:39

;PHY_uiLinkDelay);i++;if (i >= pPhyDev->PHY_uiTryMax) {return(MII_ERROR);}if (MII_READ(pPhyDev->

2016-08-29 18:06:16

,PhyAddr从0到31,重复扫描。请问:1、6748通过MDIO接口扫描32个Phy的现象,什么时候会停止?是扫到硬件的Phy就停止?2、为什么我这边,代码运行后,MDIO引脚一直有扫描32个Phy的信号?3

2018-07-25 07:38:40

个PHY(TLK110),使用EtherCat时只能用MII吗?请问RMII什么情况下使用(只是少用7个IO,可’以扩展其他功能)?它们之间通过PINMUX切换使用?2.启动配置芯片的引脚除了连接到CPU的启动配置引脚还将该线连接到了CPU的PRU等引脚上,请问这些引脚的电平会不会影响到CPU的启动方式?

2018-06-21 00:29:23

原子的例程是RMII接口用的是以太网中断,我看ST官方例程中用的外部中断,我使用的是MII接口,没弄成功,我想问一下这个接口和中断有没有必然的联系?

2019-11-05 03:47:55

MAC:S32K148PHY:LAN8710A(配置为MII模式)我想知道 enet_loopback 是否在 MII 模式下工作?如果不是,则必须进行哪些更改才能从 RMII 模式转换为 MII

2023-04-17 06:17:31

方法可以实现单片机系统接入因特网:一种方法是利用NIC (网络控制/网卡)实现网络接口,由单片机来提供所需的网络协议;另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器)来实现网络接口,主控

2019-04-30 07:00:16

RMII接口信号定义 RMII接口(Reduced MII接口)是简化的MII接口。它也分为MAC模式和PHY模式。 RMII接口接收、发送和控制的同步参考时钟REF_CLK是由外部时钟源提供的50MHz信号。这与原来的MII接口

2011-03-28 16:20:33 118

118 在网络通信链路中,需要将MAC与PHY连接,用于网络数据的传输,常用的接口有MII、RMII、SMII、SSMII、SSSMII. GMII. RGMII. SGMII. TBI. RTBI.

2018-01-25 11:22:48 17

17 以及RMII接口的PHY芯片SR8201G。2017年8月,和芯润德推出首款MII/RMII接口的100M以太网PHY芯片SR8201F,该类型芯片目前广泛应用于嵌入式系统和安防电子领域

2018-03-13 14:28:01 1768

1768 。 LAN8720 是 RMII 接口的 10/100M 以太网 phy 芯片,其与 CoM-335x 的硬件连接和设计请参考《CoM-335X 底板设计手册》。以下内容为具体步骤说明。

2018-05-17 08:19:00 11057

11057 。它包括一个数据接口和一个MAC和PHY之间的管理接口。 数据接口包括分别用于发送器和接收器的两条独立信道,每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。 管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

2018-05-18 13:51:00 14870

14870 )。在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的。

2018-05-18 13:54:00 18517

18517

介绍了以太网的物理层和链路层,重点讨论了MII接口和RMII接口的信号定义和硬件设计,此外,介绍了在官方的例程中如何根据不同的PHY进行软件的修改。

2018-07-03 05:10:00 18662

18662 网络设备一定离不开MAC和PHY,有MAC和PHY的地方就有相应的接口,无论看得见或者看不见,它就在那里,不悲不喜。在以太网中,这个接口就是介质无关接口,英文称为Media Independent

2019-06-22 09:51:53 28924

28924

MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口(图1)。数据接口包 括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。

2019-08-24 10:17:25 14515

14515 Interface)的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII

2021-01-18 10:34:13 2441

2441

通过本文对基于RGMII+phy的典型应用快速入门,解决问题。 1. 以太网接口介绍 以太网接口包含管理、数据通信接口,管理接口也就是我们常说的MDC/MDIO,用来访问phy寄存器,配置工作模式

2021-09-29 10:47:44 6045

6045

FIFO,会增加EtherCAT从站设备的传输延时,同时也会引入抖动,所以一般不建议在EtherCAT应用中使用,本文主要讨论PHY的MII接口的硬件配置。

下图是ESC和PHY MII之间的连接关系的示意图。ESC和PHY之间的时钟必须保持一致。LINK_STATUS是一个LED输出信号…

2022-01-12 15:31:21 4831

4831

PHY是物理接口收发器,它实现物理层.IEEE-802.3标准定义了以太网PHY.包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层。

2021-12-20 10:00:59 24046

24046 STM32只有网络外设时不能进行网络通信的,因为STM32只提供了SMI接口,MII和RMII接口。我们还需要与之通信的外部网络芯片,简称PHY芯片。

2022-09-01 10:21:15 2189

2189 PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-05-04 10:06:12 900

900

的芯片称之为PHY,数据链路层的芯片称之为MAC控制器。本文旨在学习以太网基础MAC和PHY的知识,总结系统框架和物理硬件组成原理,了解各种接口。PHY&MAC&

2022-12-02 10:52:30 1375

1375

PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-07-26 11:46:20 611

611 本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-07-26 11:48:08 6211

6211

MII接口进行通信和连接,到了MultiG车载以太网时,MII接口就包含了更多芯片厂商的接口比如SGMII,USXGMII,XFI等等, 但是往往这些接口是非标准的而且速率越来越高,怎么样才能更好的进行测试呢? content 直播预告 本期云上大讲堂, 泰克技术经理

2023-08-30 10:15:02 427

427

电子发烧友App

电子发烧友App

评论