macOS的主要版本)。Codasip Studio是一个处理器设计自动化平台,用于完成Codasip领先的RISC-V处理器IP的定制,使设计人员能够快速且轻松地定制其处理器设计,以面向特定领域

2022-06-28 14:06:36 1037

1037

,RISC-V®嵌入式处理器IP的领先供应商Codasip在捷克布尔诺和德国汉堡宣布,嵌入式电机和运动控制集成电路及微系统领域的全球领导者Trinamic选择了Codasip的Bk3处理器用于其下一代产品系列。

2018-03-01 16:23:47 9764

9764 Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少

2020-09-27 11:33:02 8050

8050

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议

2020-12-23 15:32:37 2169

2169 德国慕尼黑,2022年5月——处理器设计自动化领域的领导性企业Codasip宣布:通过采用西门子集团Siemens EDA的OneSpin IC验证工具,扩大了其形式验证解决方案的可用工具范围

2022-05-07 13:55:42 6483

6483

推出的FPGA设计工具集搭配Zynq UltraScale+ RFSoC会提供所有生产用的IP以及一些通用功能的IP库,用户在搭建自己设计时可以用到。这些IP集成模块可以轻松的导入Xilinx Vivado设计工具,所有IP都支持AXI4协议并且可以无缝对接Xilinx提供的IP资源。

2019-02-13 10:53:59 4004

4004 ,以实现无限创新。该系列被命名为“700系列”,包括多款应用处理器和嵌入式处理器内核。700系列通过引入一个不同的、可满足更高性能需求的出发点,来进一步完善了Codasip已广受欢迎的嵌入式处理器内核。Codasip的客户可以使用Codasip Studio™设计工具来针对其目标应用场景优化每

2023-10-24 17:25:33 339

339

8086处理器有何功能?中断系统的功能都有哪些呢?

2021-10-29 07:07:41

PL端的编写和使用,接下来是PS端的介绍AXI_Lite总线使用方法(上)pl端读写BRAM一、总览如图,main函数实现的功能主要是初始化中断,中断来自WRRD模块发送数据完毕,中断触发为上升沿。具体功能往下看。我们首先来看#define。不知道还有没有记得..

2022-01-10 08:00:55

成本是很多嵌入式系统设计的关键。为削减成本,因为考虑到越少的器件意味着越少的成本,所以设计者一般会使用单独的微处理器来处理整个系统。使用多个处理器把任务划分开会简化设计,并加快其面市时间,这就大大

2018-12-06 10:20:18

bit,则最大可以接入系统的存储空间为256kB。4) 控制总线:用来传送自CPU发出的控制信息或外设送到CPU的状态信息,双向通信;微处理器系统的程序设计语言:程序设计语言(Programming

2018-02-07 11:41:21

自动将数据(在本例中为操作码)传输到内部程序存储器。BMODE管脚确定ADSP-2111是通过HIP从主机处理器引导,还是通过数据总线从外部EPROM引导。 中断 ADSP-21xx的中断控制器

2020-07-17 14:23:24

产品线的完整信息,请参阅相应的模拟器硬件用户指南。开发工具模拟设备通过一整套软件和硬件开发工具支持其处理器,包括集成开发环境(包括CrossCore Embedded Studio和/或

2020-10-12 17:17:43

设计。处理器从代码总线正确引导,并执行指令(已禁用ITCM)。问题是我认为普通LDR / STR和LDREX / STREX在AXI总线上没有区别。无论我怎么尝试,STREX指令都将失败(返回1

2022-08-18 11:11:48

本文介绍了AMBA3.0AXI的结构和特点,分析了新的AMBA3.0AXI协议相对于AMBA2.0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟设计。最后介绍了基于AXI协议的设计实例,探讨了利用IP复用技术和DesginWareIP搭建基于AXI协议的SOC系统。

2023-09-20 08:30:25

ARM处理器中有些总线APB AHB AXI 3 AXI 4,他们的有什么不同,各自作用?

2023-10-24 07:16:36

第二章——ARM处理器文章目录第二章——ARM处理器一、ARM处理器特点1.ARM处理器主要特点2.指令集方面的主要特点3.Cortex系列处理器特点4.ARM处理器功能结构5.处理器总线接口6.

2021-12-13 07:18:29

什么是ARM系列微处理器软件架构工具?ARM系列微处理器软件架构工具有哪些特征?

2021-11-05 06:40:18

必须被下游模块实时处理。上图就明白了:这一模式实际上是对AXI总线的简化,很多场合下并不完全需要AXI总线强大的流控功能,特别是在AXI总线模块的上下游均为可进行实时处理的FPGA逻辑电路的情况下

2018-08-13 09:27:32

作者:Brian Curbo,安森美半导体注意到有什么不同吗?现在,Motion SPM在线设计工具无论在外观上,还是在功能上都与我们的Power Supply WebDesigner中的最新工具

2019-07-25 07:04:47

RISC-V生态仍然存在着不足,配套的软硬件、工具链、OS都需要均衡的发展。在此环境下RT-Thread Studio(物联网一站式开发环境)对芯来科技RISC-V处理器内核开发的全面支持,为

2020-11-14 09:26:41

Studio(CCES)和VisualDSP ++开发环境结合使用,以测试ADSP-21489 SHARC处理器的功能。开发环境有助于高级应用程序代码开发

2020-03-16 10:19:26

STV2238D总线控制多功能单片处理器相关资料分享

2021-05-21 07:02:58

以达到设计目标。 TI的WEBENCH®接口设计工具可为串行链路仿真提供简单却功能强大的环境。这款基于Web的免费工具可作为快速且方便使用的高速通道分析仿真工具 —— 对传统上由已获授权的电子设计

2018-09-10 11:47:37

本帖最后由 一只耳朵怪 于 2018-6-7 15:52 编辑

WL1837MOD的CPU处理器需要满足什么功能?其参考设计里提到用嵌入式ARM处理器作为CPU,用其他的也可以吗,为什么?如果用ARM处理器,选哪种型号呢?希望能一一解答,谢谢

2018-06-07 06:39:30

1、通用微处理器有被让人们称为单片机,它是将计算机系统集成到了一块芯片中。通用微处理器是以某中微处理内核为核心,拥有A/D、Flash RAM等各种功能和外设。一个单片机能够延生多种产品,最大

2020-11-30 16:30:42

的存储器接口,当希望对某个串口发送数据时,只需要使用类似于SRAM接口的时序,来对本模块进行数据读写即可。 MicroBlaze处理器使用的高效的AXI总线接口,因此,可以对本设计稍作修改,将对处理器

2016-12-16 11:00:37

处理器功能在硬件中实现以替代几种软件指令。通过减少多种代码指令为单一指令,以及在硬件中直接实现指令的方式,从而实现代码加速。最常用的协处理器是浮点单元(FPU),这是与CPU紧密结合的唯一普通协处理器

2015-02-02 14:18:19

后,要通过寄存器对其功能进行控制,然后是驱动程序的设计,即开发独立于处理器的属于硬件抽象层的应用程序接口函数。1.1实现功能,按键亮灯,读出LM75数据,设定高于一定温度亮灯。其中自定义IP有

2015-06-11 23:52:23

分析工具,将捕获结果可视化为图表。用红色突出显示超出预期范围的数据。 此功能可帮助用户分析性能瓶颈分析。 VARON由嵌入目标设计和捕获AXI总线的VARON IP部件以及在Linux上运行的VARON

2020-11-02 16:54:39

地实施DRC-clean,并实现具有充分质量保证的模拟意识布局,从而使设计人员对设计工具产生信心。因此,工具供应商必须为设计人员提供能够实现等同或优于其手工布局方案的工具。

2019-07-08 06:00:51

第一章复习要点①微处理器 p12②微型计算机p13③总线微处理器:一般也称中央处理器(CPU),是本身具有运算能力和控制功能,是微型计算机的核心。微处理器:由运算器,控制器和寄存器阵列组成!以及片

2021-07-22 06:48:44

前使用 Armv8.1-M 功能。让我们看看这些工具如何帮助充分利用 Cortex-M55 处理器。构建您的代码——针对性能和功耗进行优化Arm Compiler 6包含在 Keil MDK 和 Arm

2022-06-01 17:18:35

®接口设计工具可为串行链路仿真提供简单却功能强大的环境。这款基于Web的免费工具可作为快速且方便使用的高速通道分析仿真工具 —— 对传统上由已获授权的电子设计自动化(EDA)软件工具进行的分析(更严格

2018-05-28 10:41:37

,便于软件开发人员编写高效轻便的代码,而且广泛适用于多核心处理器(CPU)、图形处理器(GPU)、Cell类型架构以及数字信号处理器(DSP)等其他并行处理器,在能源电力、轨道交通、工业自动化、医疗

2020-09-08 09:39:19

我需要设计一个Zynq(可能是Zynq-7030)主板,支持ARM处理器的SATA硬盘驱动器。我想知道是否可以用GTX收发器实现SATA控制器并将其连接到芯片中的AXI总线。是否有任何参考设计或评估板支持此功能?

2020-07-29 10:28:58

CMSDK工具设计了AHB总线系统,在基于单级AHB总线的框架下,通过APB桥接器和AXI桥接器扩展了APB总线和AXI总线,进而构成该SoC高效的总线框架。通过搭建高效的总线系统将M3处理器与硬件加速器

2022-08-26 15:23:33

CSR简介RISC-V 架构的控制和状态寄存器(Control and Status Register, CSR),用于配置或记录一些处理器核的运行状态。CSR寄存器是处理器核内部的寄存器,使用其

2022-08-25 15:51:38

如何使用半自动化设计工具。这些工具对于电源设计工程师新手和专家都很有价值。

2021-09-29 10:51:53

我有一个simpleregister读/写/重置测试接口代码(在VHDL中),我想与我的顶级处理系统7wrapper代码链接。我想使用AXI总线协议对寄存器进行读/写/复位。实际上,我的测试接口

2019-09-09 10:03:44

`1、在开发zynq工程时遇到多个axi_hp总线读写ddr时,总线锁死。现象就是axi_hp的wready信号一直为低。架构图: 2、应用write1、wrtie2、read1同时并行读写ddr3

2020-04-15 21:57:28

工业应用领域正在不断增长,工业生态系统也始终需要更高的性能和更多样化的处理能力。而这正是Sitara™ AM57x处理器系列成为业内众多应用理想处理器解决方案的原因之一。凭借其独特的内核以及一个位

2018-09-04 10:07:50

到存储器或I/O端口等。它还向微机的其它各部件发出相应的控制信号,使CPU内、外各部件间协调工作。 内部总线用来连接微处理器的各功能部件并传送微处理器内部的数据和控制信号。 必须指出,微处理器本身

2011-04-13 09:52:22

随着嵌入式系统在消费电子和工业设备中的广泛应用,功耗已经开始像时钟速度和系统性能一样成为微处理器的一个核心特性。为了确定各种微处理器的功耗效率,嵌入式微处理器基准协会开发了一个有力的工具

2019-08-22 07:30:54

,FPGA/PLD和固件设计人员现在可以开始做硬件工作。 PCB开发是一个反复的过程,工程师经常改变可编程器件的内容。工程师一般也用微处理器和调试工具。 在开发和调试过程中的早期,固件

2019-05-05 09:29:32

有没有人推荐使用Vivado的好处理器?我目前有一个6核3.5GHz AMD设备,8GB内存。我的设计不是很复杂(AXI总线,MIG,一些IP),但在Artix 100T上合成和实现大约需要25分钟

2019-03-14 10:09:23

逻辑)进行常规的数据寄存器读写控制或状态监控。在实际项目中,AXI GP常常不可或缺,本实例我们就要设计一个PL端的AXI GP从机,实现PS端可读写访问的AXI GP寄存器外设。2 AXI总线协议

2019-11-12 10:23:42

HP总线。PL作为AXI HP主机,可以通过这4条总线实现对内存(DDR3)的读写访问,这4条总线加总的极限带宽,通常能够超过DDR3的最大有效带宽,因此,对于处理器与PL之间的数据交互,Zynq

2019-11-26 09:47:20

` 1概述用于PL与DDR3交互的AXI HP总线,它的性能到底如何?吞吐量是否能满足我们的应用?必须4个通道同时使用?还是只使用1个通道?时钟频率的高低对AXI HP总线的带宽有什么影响?这些

2019-11-28 10:11:38

系统的优化。也可以在互联中的任何必要的地方插入寄存器,使用简单的寄存器隔离关键的时序路径,以实现处理器和高性能存储器间的直接、快速的连接。 1.3 基本传输下面我们要对AXI协议的每个基本传输做一一

2019-05-06 16:55:32

。writeIssuingCapability:指明AXI4总线写最大同时支持的指令个数。combinedIssuingCapability:其值应不小于前两者,用于在AXI4总线读写地址通道共用的场景

2022-08-02 14:28:46

当今的设计工程师受到面积、功率和成本的约束,不能采用GHz级的计算机实现嵌入式设计。在嵌入式系统中,通常是由相对数量较少的算法决定最大的运算需求。使用设计自动化工具可以将这些算法快速转换到硬件协处理器中。然后,协处理器可以有效地连接到处理器,产生“GHz”级的性能。

2019-09-03 06:26:27

中测试他们的嵌入式软件。但现今提供的商业ESL工具没有一种可以在更早的阶段帮助工程师决定系统的基础架构,例如决定整个系统需要使用处理器的数量和种类;需要设计专门的通信机制还是使用传统的分级总线;如何将

2019-07-18 06:40:11

)、精简的两线和单线调试接口、“WFE”指令、物理内存保护(PMP)等特色功能,详细说明可参考青稞微处理器手册。

特色功能

1.硬件压栈(HPE)

稞处理器开启硬件压栈后,当发生中断,硬件自动将

2023-10-11 10:42:49

工程师试用,与为昕一起推动 EDA 软件国产化尽一份力!试用得有礼!具体产品介绍如下:产 品 介 绍 为昕 PCB 设计工具-Mars 是一款完全自主

2023-03-06 16:32:21

AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 9601

9601

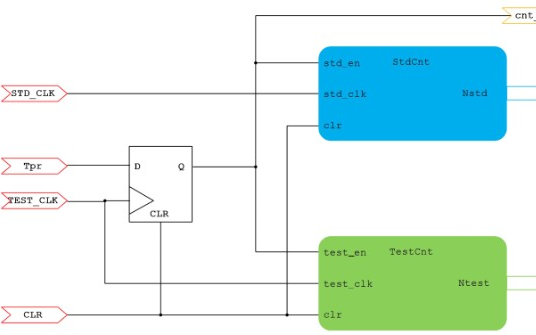

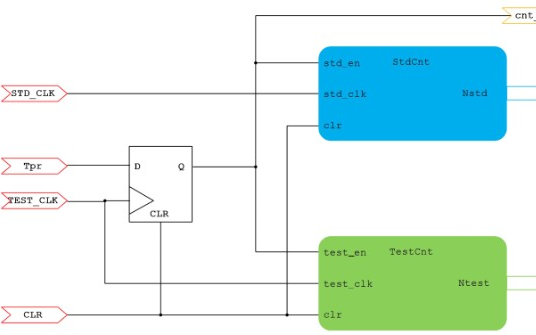

这一节我们实现一个稍微复杂一点的功能——测量未知信号的频率,PS和PL通过AXI总线交互数据,实现我们希望的功能。

2018-12-08 11:00:30 1406

1406

多个ADM1260器件可以相连,将电压时序控制器解决方案从10 V供电轨扩展至40 V。这可以通过使用一个片内总线和ADI Power Studio工具实现,该工具可将多个器件虚拟化为单一器件。

2019-06-17 06:21:00 1372

1372 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2021-02-04 06:00:15 10

10 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 4970

4970

Codasip 科达希普公司详细介绍 RISC-V处理器IP和处理器自动化设计工具领先供应商 2014年始创于捷克科技重镇布尔诺 10余年的大学科研是CODASIP的萌生之本 国际RISC-V基金会

2021-06-22 14:15:29 1654

1654 IAR Systems专业的开发工具IAR Embedded Workbench for RISC-V现已能够支持Codasip的低功耗嵌入式处理器。

2021-12-02 13:46:59 1379

1379 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 Dave Higham作为ISO 26262道路车辆功能安全国际标准和安全方面的著名专家,将继续推动Codasip去拓展定制处理器机遇。

2022-02-09 11:51:51 1380

1380

德国纽伦堡,2022年7月-- 可定制RISC-V处理器知识产权(IP)和处理器设计自动化的领导者Codasip日前宣布,Veridify Security公司的抗量子安全工具现在可以通过安全启动

2022-07-06 16:06:07 985

985 随着Codasip Studio 9.2.0版本的发布,Codasip Studio新版本通过扩展和优化等系列新功能赋能处理器设计自动化。

2022-09-14 17:21:13 942

942 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能、高主频的系统设计的。AXI协议是被优化

2022-10-10 09:22:22 8632

8632 SiliconArts光线追踪解决方案将采用Codasip的RISC-V处理器内核IP。Codasip Studio工具将支持客户为其图形应用实现高度优化。通过获得Codasip完整的架构授权,SiliconArts从此项合作伙伴关系中获得了充分的灵活性。

2022-11-03 11:21:14 557

557 SiliconArts光线追踪解决方案将采用Codasip的RISC-V处理器IP。Codasip Studio工具将支持客户为其图形应用实现高度优化。

2022-11-04 12:06:14 471

471 Codasip通过收购Cerberus增强RISC-V处理器设计的安全性 RISC-V的安全性问题需要得到高度重视 德国慕尼黑市,2022年11月 - 处理器设计自动化和RISC-V处理器硅知识产权

2022-11-16 19:37:05 486

486 对于CGI Studio的用户来说,上市时间是重中之重,这种理解反映在CGI Studio 3.11的主要新功能中。

2022-11-30 11:29:02 2504

2504 来源:Codasip 德国慕尼黑,2022年12月7日——处理器设计自动化和RISC-V处理器IP的领导者Codasip今日宣布成立Codasip实验室(Codasip Labs)。作为公司内部创新

2022-12-09 15:55:58 452

452 Codasip成立Codasip实验室以加速行业前沿技术的开发和应用 日前处理器设计自动化和RISC-V处理器IP的领导者Codasip宣布成立Codasip实验室(Codasip Labs)。作为

2022-12-09 18:23:01 3646

3646 加贺富仪艾电子旗下代理品牌 Candera CGI Studio是可扩展且独立于硬件的HMI设计工具,它可以开发针对汽车,工业和家电领域的各种创新和定制化的嵌入式GUI解决方案。

2023-04-23 10:52:59 642

642

在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

2023-05-25 11:22:54 570

570

这种灵活性对于处理器IP来说虽然不太常见,但是可以使用Codasip IP来实现。所有的Codasip RISC-V内核都是用一种叫做CodAL的高级语言设计的,并且可以用Codasip

2023-05-31 15:25:25 609

609

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

用Codasip独特的Codasip Studio设计工具集,为MEMS(微电子机械系统)传感器开发一个定制的RISC-V内核,助力数字耳朵的研发和应用并最终为全人类谋福祉。 无独有偶,该技术再次受到生物学的启发,由欧盟提供部分资金,涉及欧洲7个国家的27个组织,3千万欧元资金扶持。这个为期

2023-06-23 21:23:38 396

396 ,2023 年 6 月 30 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,基于 AI 的 Cadence Virtuoso Studio 设计工具和解决方案已获得 Samsung Foundry 认证。 双方的共同客户可以放心利用 Virtuoso Studio 和

2023-06-30 10:08:30 681

681 的IP来加速和简化其设计项目。 Codasip的系列RISC-V处理器可以通过使用功能强大的Codasip Studio处理器设计自动化工具进行

2023-07-03 16:13:04 464

464 在本文中,我们将以西门子EDA处理器验证应用程序为例,结合Codasip L31这款广受欢迎的RISC-V处理器IP提供的特性,来介绍一种利用先进的EDA工具,在实际设计工作中对处理器进行验证的具体方法。

2023-07-10 10:28:41 300

300

LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484 LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

RISC-V定制计算领域领导者 Codasip 今天宣布推出全新高度可配置的RISC-V基准处理器系列,旨在实现无限创新。该"700家族系列"包括应用和嵌入式处理器内核。700

2023-10-18 10:03:55 320

320 自动化设计工具是Codasip定制计算解决方案的重要工具。这一强大而灵活的自动化工具,可帮助半导体制造商、系统

2023-11-02 09:24:45 397

397 2023年年尾最为重要的集成电路年会,Codasip作为银牌赞助商向客户和观众展示了其独特的定制计算解决方案、新产品RISC-V处理器700系列以及Codasip Studio设计工具的独到之处。 Codasip作为全球领先的RISC-V处理器IP核供应商,我们在此次展会上再次证明了其在处理器的设计、开发和优

2023-11-11 10:22:32 414

414 移动和物联网。10月高通联合谷歌开发基于RISC-V架构的Snapdragon Wear芯片,用于下一代Wear OS手表。RISC-V应用在巨头们的引领下加速发展。 总部位于欧洲的Codasip公司是RISC-V行业先锋企业,主要提供IP核和设计工具,从而形成整体解决方案支持客户做定制化的处理器

2023-11-29 10:40:17 956

956

电子发烧友App

电子发烧友App

评论