All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))昨日宣布推出符合汽车级要求的Zynq® UltraScale+™ MPSoC系列器件,其可支持安全攸关的ADAS和自动驾驶系统的开发。

2018-01-17 09:15:26 9204

9204 Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,专用于和元器件内的控制寄存器进行通信。AXI-Lite允许构建简单的元件接口。这个接口规模较小,对设计和验证方面的要求更少

2020-09-27 11:33:02 8050

8050

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

UltraScale+MPSoC系列器件共有四个大的系列,分别是CG系列、EG系列和EV系列,其中EG系列和EV系列提供汽车级和军品级器件。 相较与上一代ZYNQ-7000产品,器件性能优越性主要体现在

2020-12-17 10:53:42 19692

19692

FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门

2020-12-25 14:07:02 2957

2957

一、AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程。若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP

2020-12-31 09:52:02 7165

7165

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实验使用一个AXI GPIO的IP核,让PS端通过AXI总线控制PL端的LED灯,实验虽然简单,不过可以让我们了解PL和PS是如何结合的。

2021-02-01 10:06:00 6182

6182

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2022-08-02 12:42:17 6661

6661 在Zynq MPSoC的器件里,PS (Processing System )集成了三个看门狗,分别是CSU SWDT,LPD SWDT和FPD SWDT。

2023-06-30 09:47:22 851

851

1、AXI接口协议详解 AXI 总线 上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线

2022-10-14 15:31:40

我目前正在使用ZCU102板测试Zync Ultrascale + MPSoC。并要求使用APM检查DDR子系统性能。令人惊讶的是,AXI总线QoS没有明显的影响,我开始仔细研究在我的ILA中开发

2020-05-21 14:00:01

描述TIDA-01480 参考设计是一种可扩展的电源设计,旨在为 Xilinx Zynq UltraScale+ (ZU+) 系列 MPSoC 器件供电。此设计接收来自标准直流电源的电力,并通过明确

2018-10-25 16:06:36

本帖最后由 何立立 于 2018-1-9 15:03 编辑

ZYNQ 、AXI协议、PS与PL内部通信 三种AXI总线分别为:AXI4:(For high-performance

2018-01-08 15:44:39

ZYNQ Ultrascale+ MPSOC FPGA教程

2021-02-02 07:53:25

大部分器件的接口要求,提供互联架构的灵活性与独立性。

(1)AXI总线

总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由数据线、地址线、控制线等构成。在ZYNQ中支持三种AXI总线

2023-11-03 10:51:39

ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果一、前言 在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问

2020-04-23 11:16:13

1、Zynq MPSoC支持的DDR介绍自己做自己的嵌入式产品一般要选择合适的DDR,而这里开发板给的是4GB的UIMM的DDR4,也就是电脑上用的,所以用不了,只能自己挂载Component,这里

2022-04-19 17:56:03

通信设备类功能的分步过程本节介绍CDC抽象控制模型(ACM)Linux小工具驱动程序的详细信息,如何配置Linux源以支持Zynq®的串行小工具驱动程序UltraScale +™MPSoC USB

2019-01-03 09:59:50

MPSOC系列FPGA视频教程目录(总计128集)第一部分 MPSOC裸机开发(共65集)一、MPSoC简介及开发流程01_MPSoC架构介绍02_MPSoC开发之Vivado工程创建流程03_MPSoC

2022-07-21 10:34:51

` Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平台。其亮点在于FPGA里包含了完整的ARM处理子系统(PS),包含了四核Cortex-A53处理器或双核

2021-01-07 17:11:26

管理系统;高密度片上UltraRAM静态存储器;单通道速率高达32Gbps的高速收发器;集成100GbE、PCIe Gen4、150Gbps Interlaken等I/O控制器;高性能UltraScale可编程逻辑。和Zynq-7000系列器件相比,加密、安全和电源管理都得到了显著增强。

2019-10-09 06:07:09

,在详细介绍具体步骤之前,我们先来了解什么是管理程序,以及它们如何与Zynq UltraScale+ MPSoC 上的处理器协同工作。

2019-10-09 06:21:21

我有一个simpleregister读/写/重置测试接口代码(在VHDL中),我想与我的顶级处理系统7wrapper代码链接。我想使用AXI总线协议对寄存器进行读/写/复位。实际上,我的测试接口

2019-09-09 10:03:44

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

`1、在开发zynq工程时遇到多个axi_hp总线读写ddr时,总线锁死。现象就是axi_hp的wready信号一直为低。架构图: 2、应用write1、wrtie2、read1同时并行读写ddr3

2020-04-15 21:57:28

``XILINX 新一代 SOC,Zynq UltraScale+ MPSOC 系列性能强悍无比,相比ZYNQ 7000系列每瓦性能提升5倍,作为一名电子发烧友,都想体验一把这高性能的MPSOC

2019-08-07 15:05:33

介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。3 AXI GP外设配置在zstar_ex53实例的基础上,需要对ZYNQ7Processing System(PS)配置页面做更改

2019-11-12 10:23:42

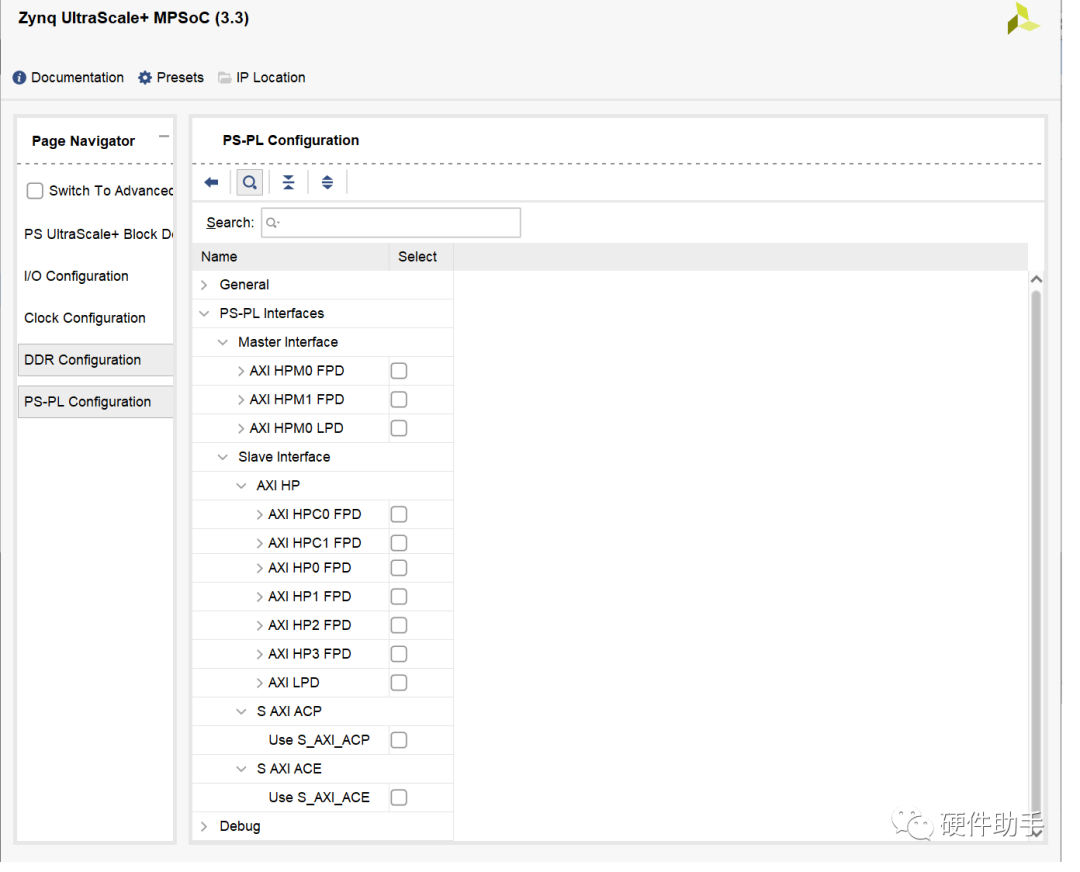

的逻辑设计。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。3Zynq PS的AXI HP配置在ZYNQ7 ProcessingSystem中,点击左侧Page

2019-11-26 09:47:20

不同通道使用情况下的数据吞吐量。大家可以在此基础上,更改不同的AXI HP总线时钟频率,以评估时钟频率对AXI HP总线的影响。2 AXI总线协议介绍参考文档《玩转Zynq-基础篇:AXI总线协议介绍

2019-11-28 10:11:38

`玩转Zynq连载3——AXI总线协议介绍1 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 1 AXI协议简介AMBA AXI(Advanced

2019-05-06 16:55:32

最近做的东西涉及到将原有的DSP+FPGA架构的程序移植到ZYNQ-7系列FPGA上,请问如何将原DSP程序移植到ZYNQ-7的ARM上,可不可以做一个EMIF总线和AXI总线转换的模块呢?

2014-05-12 21:51:09

你好我们正在考虑在我们的新设计中使用Zynq Ultrascale + MPSOC。我们想在我们的电路板设计中加入HDMI接口。 Zynq Ultrascale + MPSOC在PS中有一个

2019-10-14 09:17:03

AMBA AXI 总线学习笔记,非常详细的AXI总线操作说明

2015-11-11 16:49:33 11

11 今天,赛灵思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎来一个新的产品系列及三款最新器件! 新的产品系列被称为Zynq Z-7000S系列,三款新器件分别为

2017-02-08 04:25:13 517

517

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 在高性能系统中越来越多地使用高速串行互联意味着你会在Zynq UltraScale+ MPSoC系列中的11款器件中发现很多Gbps

2017-02-08 05:50:41 552

552 Zynq UltraScale+ MPSoC器件提供64位处理器可扩展能力,将实时控制系统与软件和硬件引擎相结合,完成显示、视频、波形生成以及数据包处理等操作。基于通用的实时处理器与可编程逻辑组合

2017-02-08 09:28:11 218

218

学了zynq一段时间,一上来的时候就被zynq的GPIO唬住了,实在没搞清楚zynq的GPIO怎么回事,一会这样,一会那样,最后才慢慢发现zynq至少有3种GPIO可以调用。难怪我觉得每篇介绍

2017-02-08 10:23:12 2711

2711

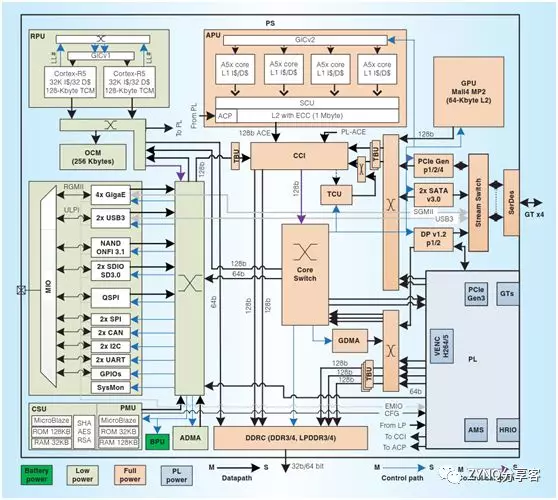

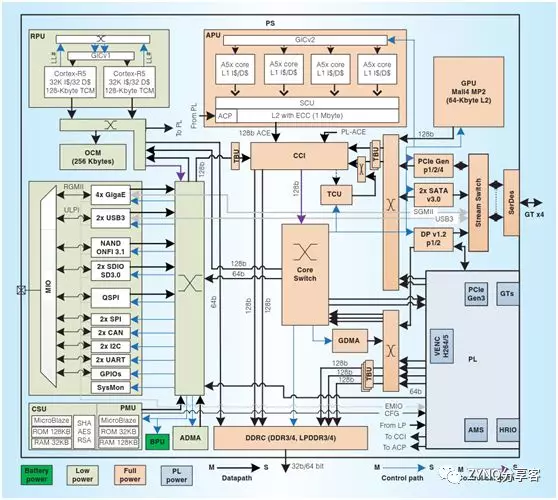

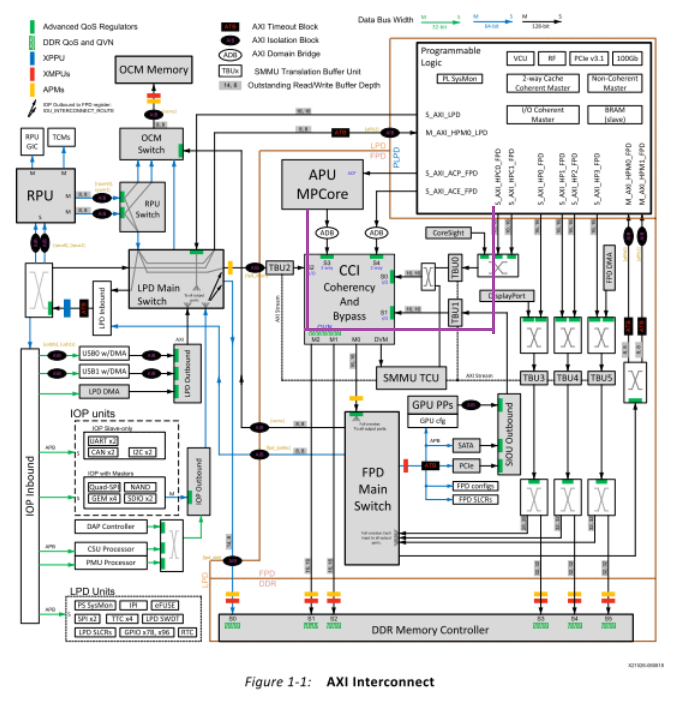

MPSoC器件族中的11个功能单元以“为任务量身打造模块”的概念引入所需的处理能力。以下块状图展示了 Xilinx Zynq UltraScale+ MPSoC系列中所有可用的元件。 这里可清楚看到

2017-02-09 08:01:11 1934

1934

本节介绍的AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。 书上讲的AXI比较具体,本节呢不打算落入俗套,从应用角度解释AXI。

2018-07-13 07:08:00 10226

10226

详细介绍AXI总线

2017-02-28 21:03:54 1

1 本文主要介绍zynq linux AXI DMA传输步骤教程,具体的跟随小编一起来了解一下。

2018-07-08 05:46:00 29549

29549

AXI总线的MicroBlaze双核SoPC系统设计

2017-10-31 08:54:44 8

8 QEMU 在 Xen 上运行 Doom 呢,在详细介绍具体步骤之前,我们先来了解什么是管理程序,以及它们如何与Zynq UltraScale+ MPSoC 上的处理器协同工作。

2017-11-18 18:39:25 2298

2298

1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write data

2018-01-05 08:13:47 9601

9601

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

2018-03-21 14:55:00 3099

3099

本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492 该视频重点介绍了UltraScale +产品系列的第一个成员Zynq®UltraScale+™MPSoC,并展示了使用可编程逻辑中的DDR4 SDRAM IP的存储器接口系统的稳健性。

2018-11-29 06:36:00 3044

3044 该演示展示了Zynq UltraScale + MPSoC的视频处理功能。

使用ZCU102开发套件,Zynq UltraScale + MPSoC将全高清1080p视频输入转换为UltraHD 4K视频输出

2018-11-29 06:28:00 2904

2904 Zynq®UltraScale+™MPSoC,现已开始发售。视频向您重点介绍了Xilinx UltraScale +产品组合的第一位成员

2018-11-27 06:47:00 3262

3262 该视频重点介绍了UltraScale +产品组合的第一个成员,Zynq®UltraScale+™MPSoC,以及其多样化收发器技术的稳健性。

2018-11-27 06:33:00 2501

2501 全新Zynq UltraScale MPSoC实现了前所未有的异构多处理能力,从而能够实现“为合适任务提供合适引擎”。这些新器件相对此前解决方案可将系统级性能功耗比提升约5倍。位于处理子系统

中心

2018-11-27 06:09:00 3893

3893 行业抓取式演示视频重点介绍了Zynq UltraScale + MPSoC装有专用处理引擎,面向图像处理,实时处理和功能安全性。

2018-11-23 06:59:00 2723

2723 赛灵思联盟成员MoSys在OFC 2016上展示了其与Xilinx Zynq UltraScale + MPSoC平台接口的BandwidthEngine®3高速串行接口智能存储器IC。

2018-11-22 06:16:00 2752

2752 该视频显示了Zynq®UltraScale+™MPSoC处理系统中硬化控制器的性能如何,LPDDR4以2.4Gbps运行48小时以上,在压力下,具有低抖动和大量余量。

2018-11-22 06:14:00 3772

3772 本视频向您演示了赛灵思16nm MPSoC产品系列的最新成员Zynq UltraScale + MPSoC EV器件的强大的实时视频处理功能。该器件专为视频处理等应用优化,集成H.264 / H.265视频编解码

单元,能够以每秒60帧的速率同时对视频进行4K编码和解码操作。

2018-11-22 05:51:00 4039

4039 本文档的主要内容详细介绍的是zynq UltraScale MPSoC的产品选择指南资料免费下载

2019-02-15 11:51:59 14

14 Zynq UltraScale+™ MPSOC系列基于Xilinx UltraScale™MPSOC体系结构。该系列产品在单个设备中集成了功能丰富的64位四核或双核ARM®Cortex™-A53

2019-02-21 16:48:54 19

19 由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

2019-05-12 09:10:33 10860

10860

XA Zynq UltraScale+ MPSoC 系列已通过 Exida 认证,符合 ISO 26262 ASIL-C 级的安全规范。Exida 是全球领先的自动化和汽车系统安全性和保密性专业认证公司之一。

2019-07-29 11:11:49 2364

2364 Zynq UltraScale+ MPSoC是Xilinx推出的第二代多处理SoC系统,在第一代Zynq-7000的基础上做了全面升级,在单芯片上融合了功能强大的处理器系统(PS)和用户可编程逻辑(PL)。Zynq UltraScale+ MPSoC系统框图

2019-11-18 11:03:22 2540

2540

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。 本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论

2020-09-27 11:06:45 5857

5857

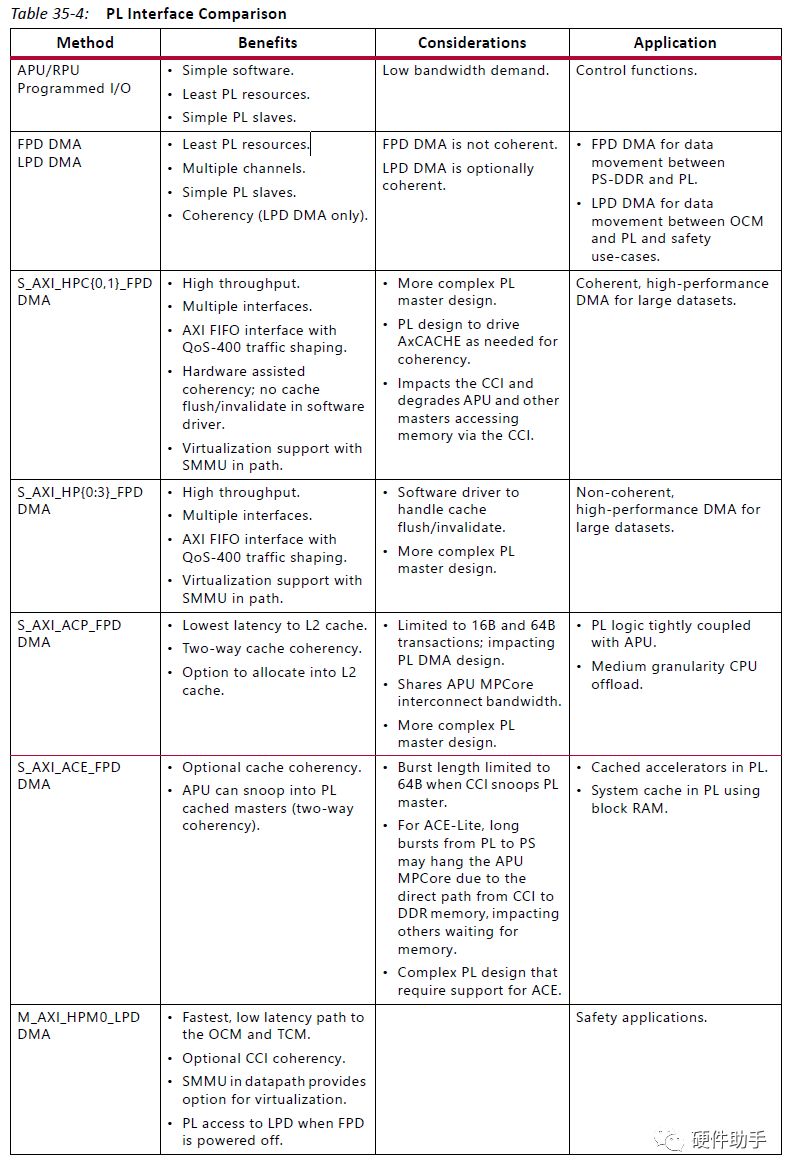

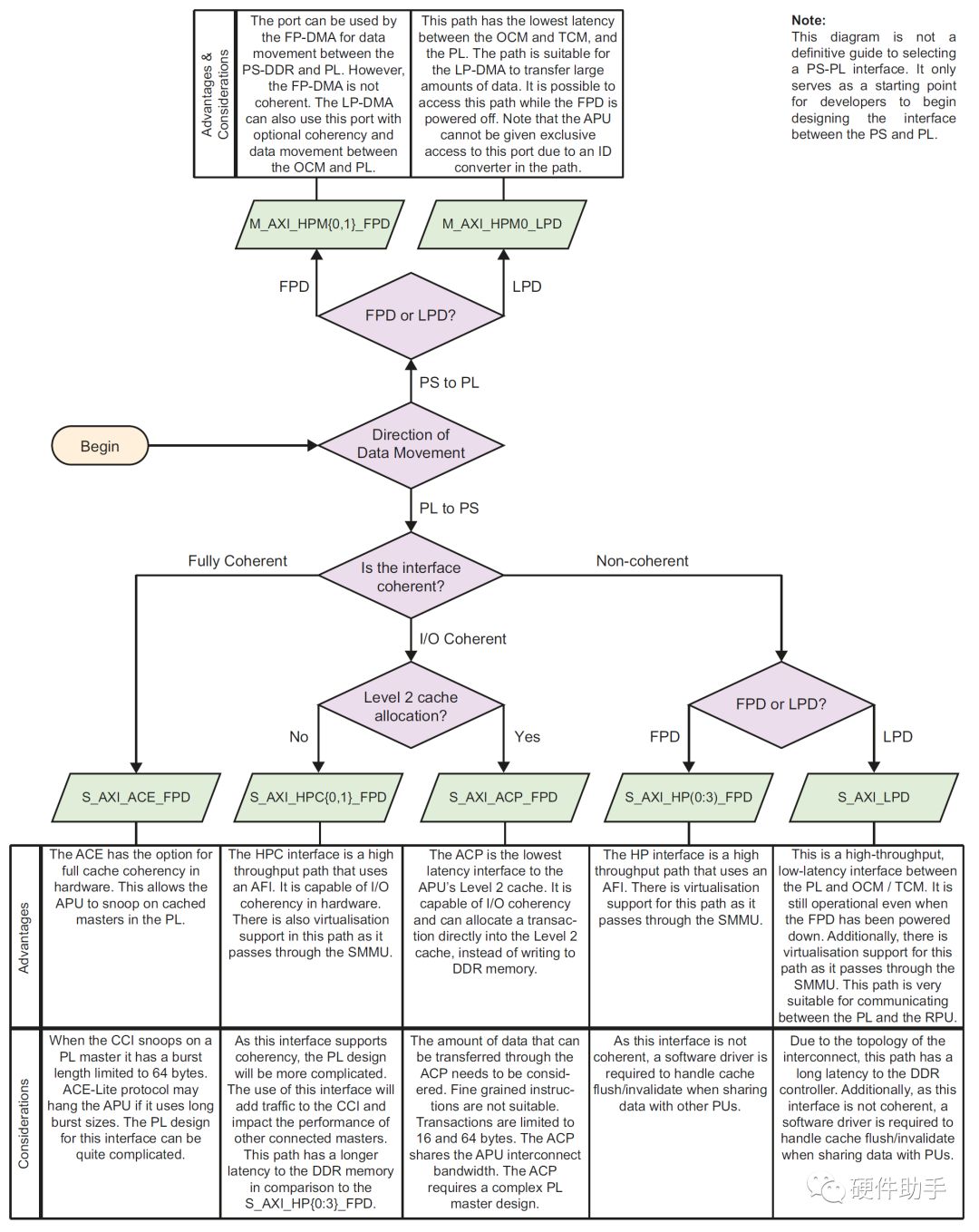

1. 参考文档 1.1. AR69446 AR# 69446 Zynq UltraScale+ MPSoC Example Design - Use AXI HPC port to perform

2020-11-04 12:19:07 4389

4389

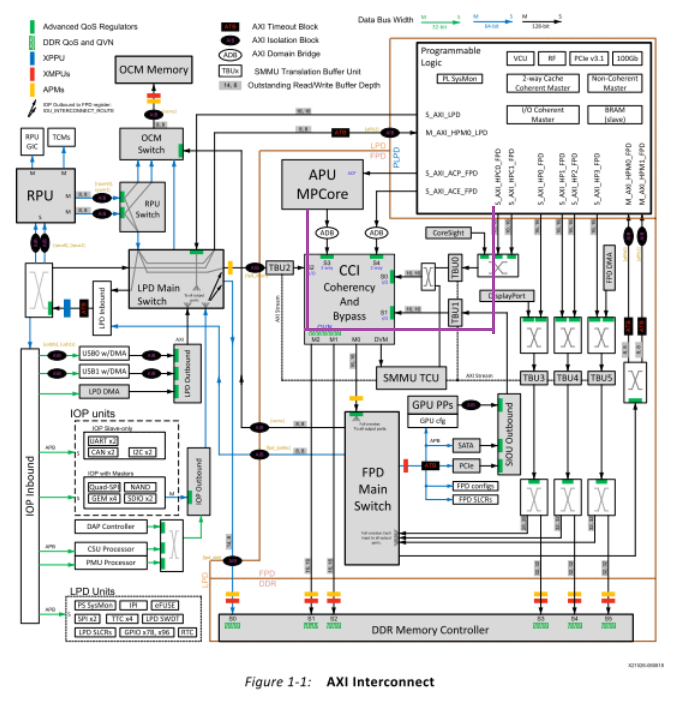

ZYNQ中DMA与AXI4总线 为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的: 图4‑34连接 PS 和 PL 的 AXI 互联

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

2022-02-08 11:44:02 12802

12802 ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 2046

2046

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

2021-02-04 06:00:15 10

10 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq

2021-02-23 06:00:10 15

15 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点。 2.1 技术时间线 进一步介绍之前,需要指出这三种

2021-04-02 17:20:14 13783

13783

AXI是个什么东西呢,它其实不属于Zynq,不属于Xilinx,而是属于ARM。它是ARM最新的总线接口,以前叫做AMBA,从3.0以后就称为AXI了。

2021-04-09 17:10:10 4970

4970

目录1. MPSoC的中断处理介绍 2. 扩展PL中断 3. 扩展AXI Intc中断 3.1. AXI Intc PL连接 3.2. AXI Intc Device Tree 3.3. AXI

2021-05-07 15:34:15 3626

3626 学习内容 近期设计需要用到AXI总线的IP,所以就对应常用的IP进行简要的说明,本文主要对AXI互联IP进行介绍。 基础架构IP 基础的IP是用于帮助组装系统的构建块。基础架构IP往往是一个通用IP

2021-05-11 14:52:55 5612

5612

米尔电子推出的国内首款zynq ultrascale+ mpsoc平台核心板(及开发板):MYC-CZU3EG吸引了人工智能、工业控制、嵌入式视觉、ADAS、算法加速、云计算、有线/无线通信

2022-01-07 15:20:29 3

3 [导读] 前面写过篇介绍ZYNQ基本情况的文章,今天来肝一篇实战文章介绍AXI quad SPI 使用方法,如果你正使用ZYNQ的这个IP,希望对你有所...

2022-01-26 17:01:47 6

6 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 关于AXI总线协议的一些简单知识,通过阅读Xilinx的使用指导手册(UG1037),结合正点原子的ZYNQ视频进行梳理总结。

2022-07-15 09:16:29 2230

2230 Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在相对较高层次对比了三种器件。Zynq MPSoC的PS部分比Zynq的PS部分面积更大,也更复杂。本章,将介绍这三种器件的特点.

2022-08-15 09:16:38 1629

1629 ZU19EG 是一款紧凑型 SoC 原型开发板,采用 Zynq® UltraScale+™ MPSoC 器件,可提供 64 位处理器可扩展性,同时将实时控制与软和硬引擎相结合,用于 SoC 原型

2022-09-26 11:28:39 4

4 基于 Xilinx 公司ZYNQ Ultrascale+ MPSoC系列 FPGA 芯片设计,应用于工厂自动化、机器视觉、工业质检等工业领域

2022-11-02 14:35:47 1127

1127 在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

2023-05-25 11:22:54 570

570

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

电子发烧友网站提供《Zynq UltraScale+ MPSoC中的隔离方法.pdf》资料免费下载

2023-09-13 17:11:48 1

1 电子发烧友网站提供《Zynq UltraScale+ MPSoC的隔离设计示例.pdf》资料免费下载

2023-09-13 11:28:01 2

2 电子发烧友网站提供《Zynq UltraScale+MPSoC嵌入式设计教程.pdf》资料免费下载

2023-09-13 09:14:33 4

4 电子发烧友网站提供《Zynq UltraScale+ MPSoC生产勘误表.pdf》资料免费下载

2023-09-15 10:35:56 0

0 电子发烧友网站提供《Zynq UltraScale+ MPSoC验证数据手册.pdf》资料免费下载

2023-09-15 10:13:41 0

0 Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

LogiCORE™IPAXI IIC总线接口连接到AMBA®AXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

2023-09-28 15:56:16 4484

4484 armbian、 hdmi、 zynq、 mpsoc、 rk3399

2023-10-13 18:11:00 913

913 在介绍AXI之前,先简单说一下总线、 接口 以及协议的含义 总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般

2023-12-16 15:55:01 248

248

电子发烧友App

电子发烧友App

评论