使用自己做的6678的板卡. PCIe参考时钟100MHz. 运行例程中的PCIe测试.pcie_phy_loopback. 当运行完 gpPCIE_app_regs->CMD_STATUS

2019-01-03 11:36:50

6678的pcie和fpga的pcie TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

2018-06-21 15:49:12

有没有研究PCIE的,求指导。{:4_100:}

2013-03-23 23:46:18

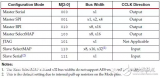

1.PCIE的发送和接收数据本工程的目的是在XC7K325tffg的平台上实现pcie的数据发送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的结构:架构各个模块的作用PCIE部分

2019-12-26 10:46:09

开发环境:windows开发平台:QT5.11.31.PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2019-12-26 10:27:19

开发环境:windows开发平台:QT5.11.31、PCIE上位机测试过程FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:1.实现上位机的速度测试,经测试pcie的传输速度

2022-01-13 16:44:54

PCIE-52P90H

2023-03-29 22:43:17

我想用C6657的PCIE接口扩展一个WIFI.

C6657的PCIE需要一个LVDS的参考时钟(PCIECLKP, PCIECLKN), WIFI芯片的PCIE需要一个HCSL的参考时钟

2018-06-21 18:45:06

用过好多PCIE网卡与PCIE SAS卡,很多都在卡上通过DCDC把12V转为3.3V,为何不直接使用主板提供的3.3V呢?没想明白

2019-03-14 10:38:59

从主板直接引出两路PCIE接口,接两路SDI视频采集卡。硬件可以正常扫描到,但只有一路SDI视频,另外一路直接没信号。两路PCIE接口通过PCB板直接转接出来的,是因为走线原因还是其它什么原因

2017-02-23 10:12:23

PCIe 5.0的接口设计有多难?如何使用成熟的IP来克服这个问题?32 GT/s PCIe 5.0具有哪些主要功能?

2021-06-17 11:37:04

本文档旨在提供关于将PCIe接口集成到基于AMBA的片上系统(SoC)的指导。

假设PCIe接口通过基于AXI或ACE协议的互连连接到SoC的其余部分。

读者应熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

描述 这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2022-09-21 07:43:27

PCIe-9110IM 是一款兼容 PCI Express r1.0a 规范的单 CAN 口 PCIe-CAN 通讯接口卡。PCIe-9110IM 接口卡支持 PCI Express 多功能设备外围

2022-10-31 06:11:43

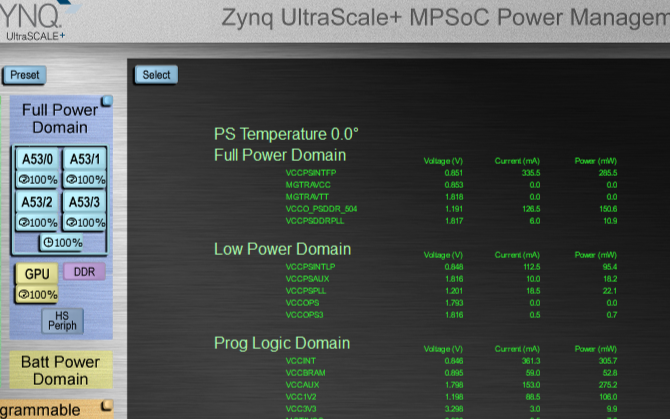

嗨,看起来ZCU104是ZCU102和ZCU106的升级版本,具有支持机器学习的额外功能,但更便宜?最好的祝愿,花环

2019-10-22 09:19:54

有大佬能分享一下PCI总线转PCIe(PCIe转PCI)的PCB原理图吗?

2019-01-25 11:38:39

` A1-106-100-533西门子主板 A1-106-100-533西门子主板故障分类: 人为故障 有些朋友,电脑操作方面的学问懂得较少,在操作时不留意操作标准及平安,这样对电脑

2020-02-24 17:29:55

`EC20 Mini PCIe是采用 PCI Express® Mini Card标准接口的LTE模块;采用LTE 3GPP Rel.9技术,支持最大下行速率100Mbps和最大上行速率50Mbps

2018-06-05 17:38:23

EK-U1-ZCU106-G

2023-03-29 21:47:32

PCIE BOARD 6 PORT DB-9

2023-03-22 20:41:28

我在LS1043A开发板上J12接口接上pcie接口设备,系统启动后,执行lspci,没有知道设备被识别请问这是什么问题?需要怎么配置?谢谢

2022-01-05 06:49:29

实现一个采样率(最大32MS/s)可调节的PCIe数据采集卡,直接插到PC或者工控机或者工业树莓派上使用。下

2021-07-26 06:55:30

DEVELOPMENTSYSTEMT4240PCIE

2023-03-22 19:56:26

您好,

我有一个ARM开发板, 其pcie接口支持pcie 1.1 X1,现在想通过它的卡槽连接C6657完成协处理功能. 发现C6657的pcie接口支持Gen 2 X2,想请问您

2018-06-21 06:16:11

FMC/FMC+子卡完成1.5MHz~6GHz的高速采集和回放功能;也可搭载我公司FMC+存储板完成48TB@5GB/s的实时存储功能,从而低成本的实现10GB/s的高速数据实时存储n PCB采用高速

2023-05-21 18:27:41

Virtex 7 PCIe硬IP是否意味着FPGA内部的ASIC?或者像Tandem方法一样,在第一阶段,CPLD将PCIe初始配置加载到FPGA? (http://www.em.avnet.com

2020-05-29 12:52:09

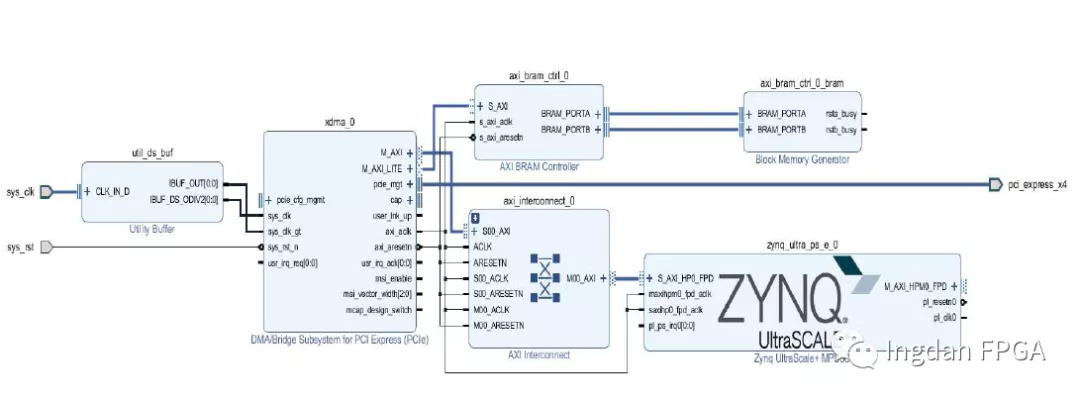

。实现PS,PL各路接口测试,目前完成PCIe功能开发,千兆网,万兆网的开发,FMC接口匹配公司视频,AD类子卡,有充分的接口互联软件,基础软件功能免费提供,高端软件及复杂软件进行定制。软件结构

2022-03-16 10:40:33

插入机箱时能够查到PCIE设备,但是不使用扩展板,直接将插针式连接器插入机箱则无法识别。想问一下是耦合电容的问题吗,或者其他什么原因?

pcie连接器原理图如下

2023-05-16 11:07:40

我看到了TI给出的6678pcie的例程,是两块demo板相互之间的通信,但是我还是不太清楚如何是将两块demo板的pcie接口实现互连,是用专用的插槽吗?这个的设备TI有提供吗?

2018-08-06 09:20:25

大佬们通过pcie延长线连接主板pcie插槽和板子上的金手指pcie代码烧到板子里重启电脑了但设备管理器其他设备没出现PCI内存控制器是什么原因呀救救孩子

2023-05-22 09:49:27

机制;(7)具有螺距补偿控制,在单轴上通过多个补偿点进行精确调整,从而实现更高的加工精度。

选择PCIE464控制卡的好处1、高速位置比较输出PSOPCIE464控制卡的高速硬件位置比较输出PSO功能

2024-01-24 09:48:21

:能使用xiinx 的PCIE ip核完成读写功能对以上课程有兴趣的同学点下面链接学习 : 明德扬FPGA课程_PCIE高速接口XILINX.ISE教程_哔哩哔哩_bilibili这只是我们明德扬课程

2022-02-14 09:50:22

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起来还是挺方便的,生成IP的同时生成了对应的PCIE

2023-11-17 14:35:30

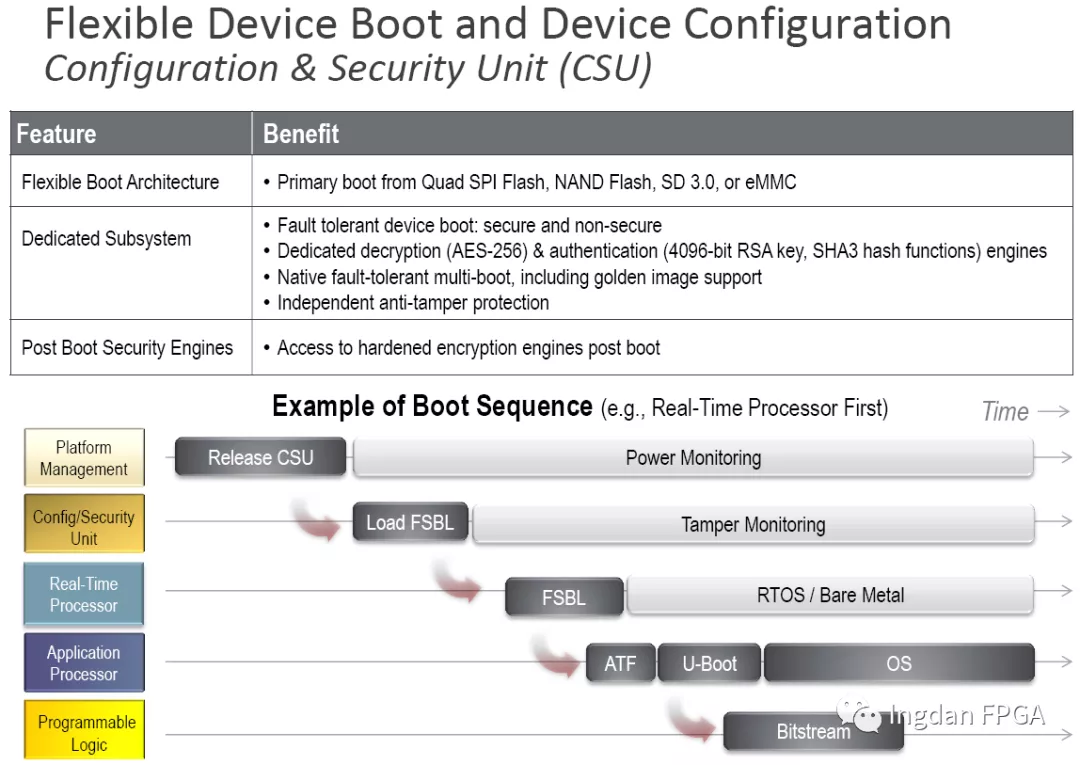

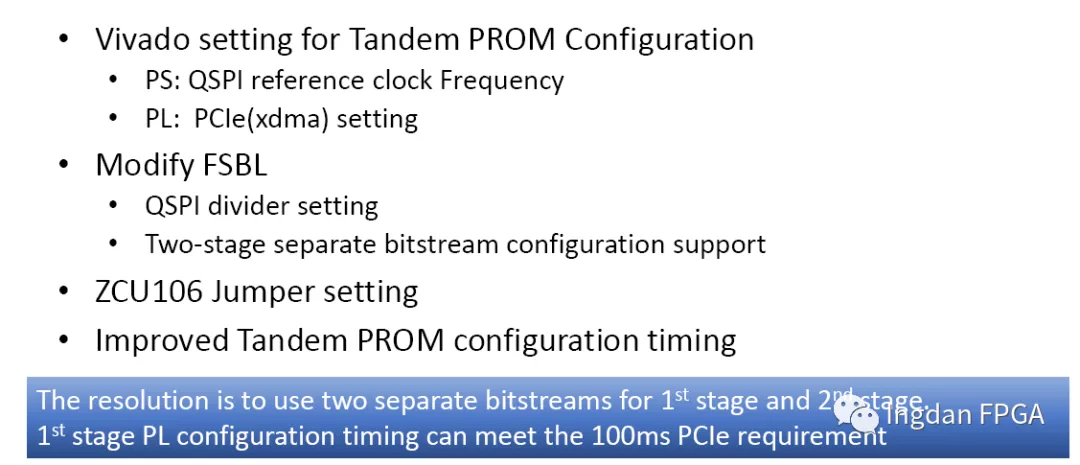

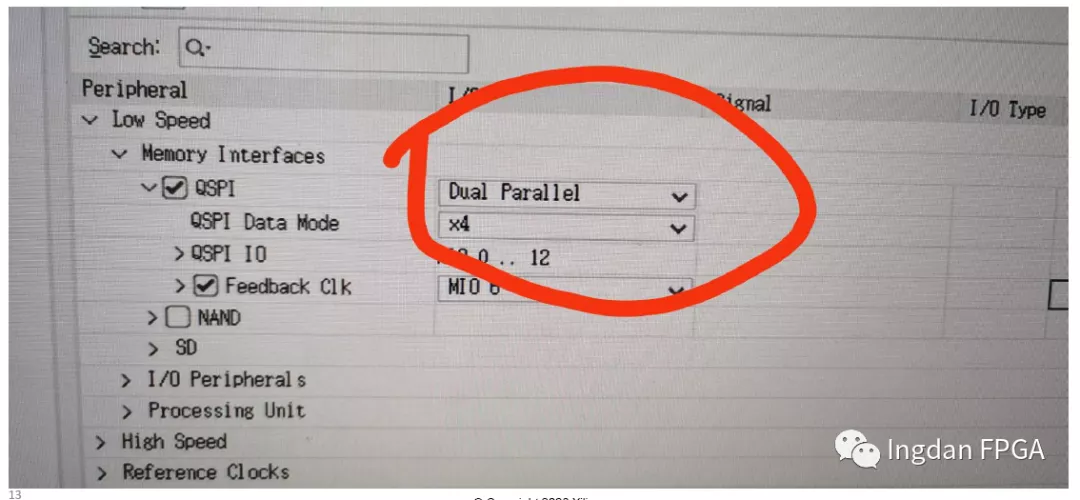

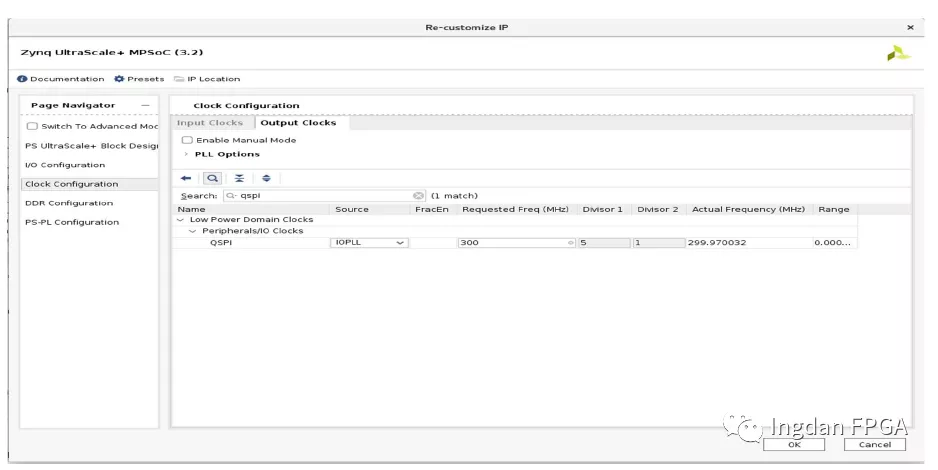

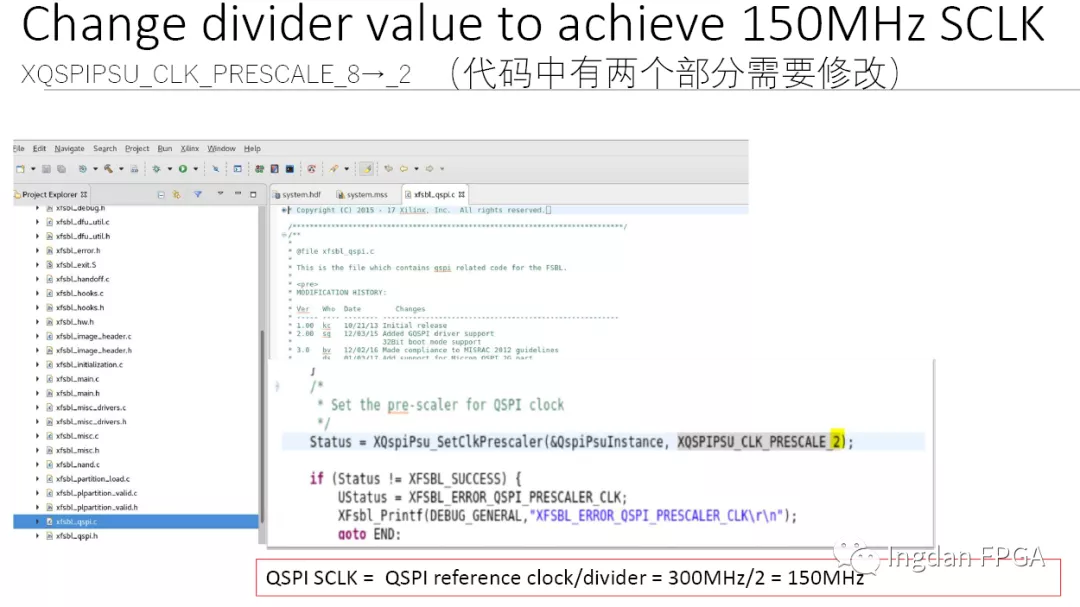

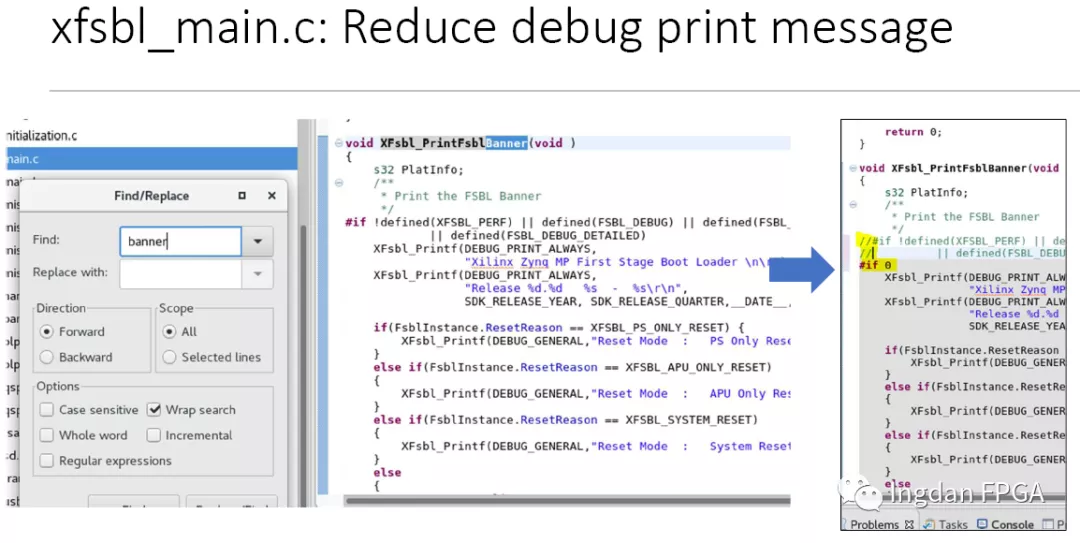

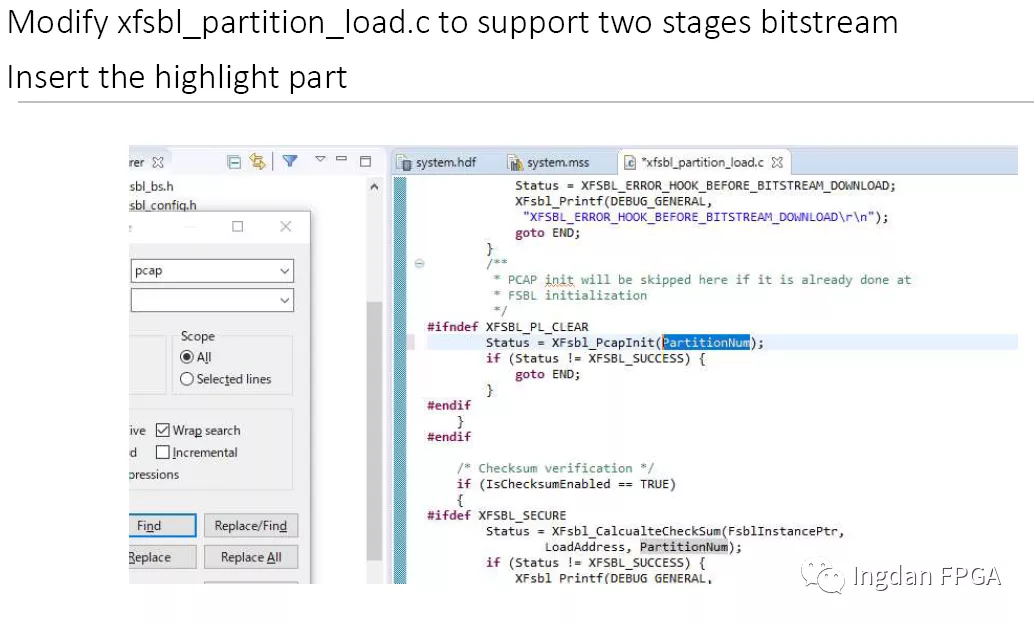

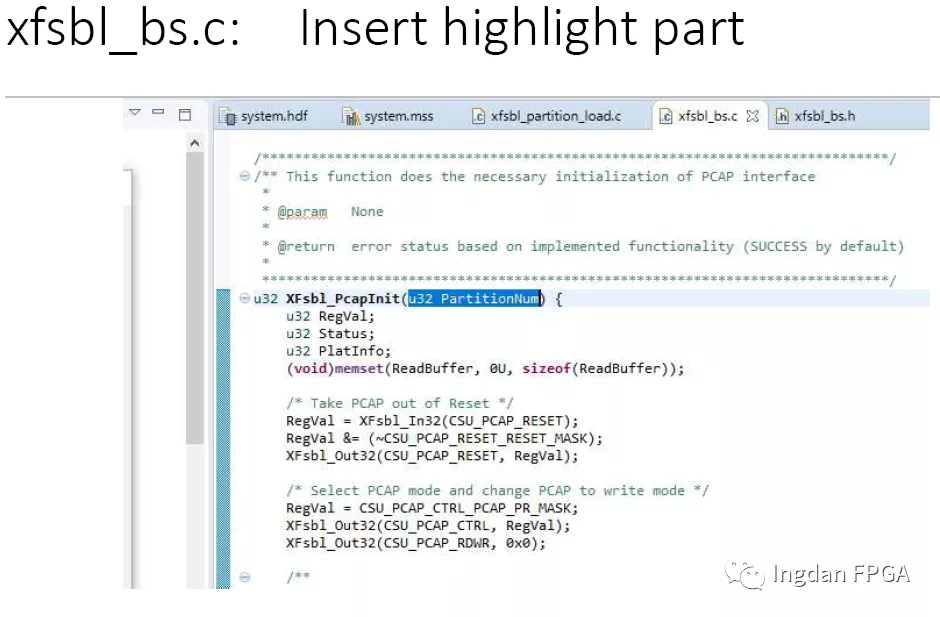

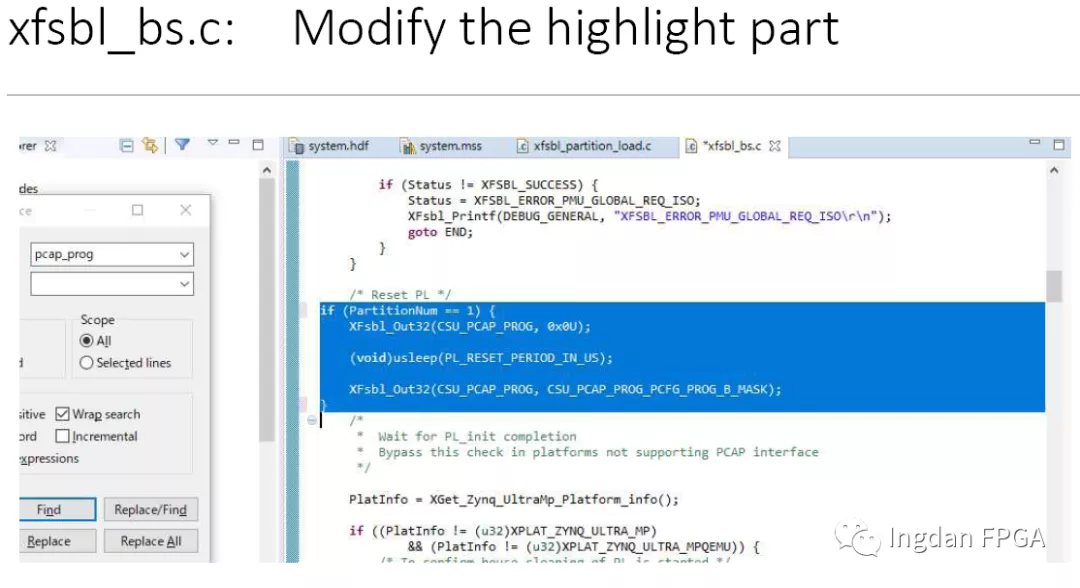

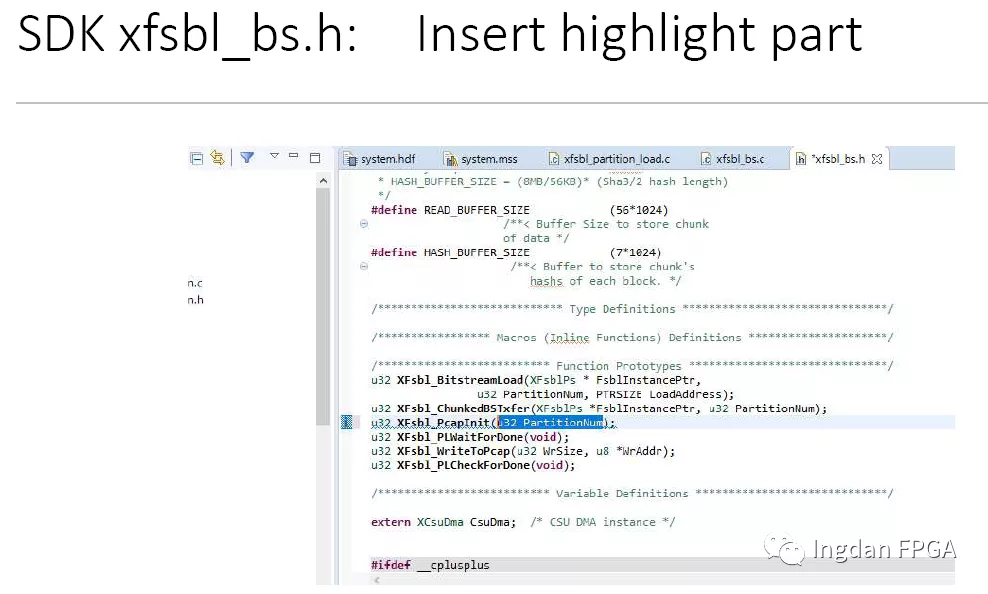

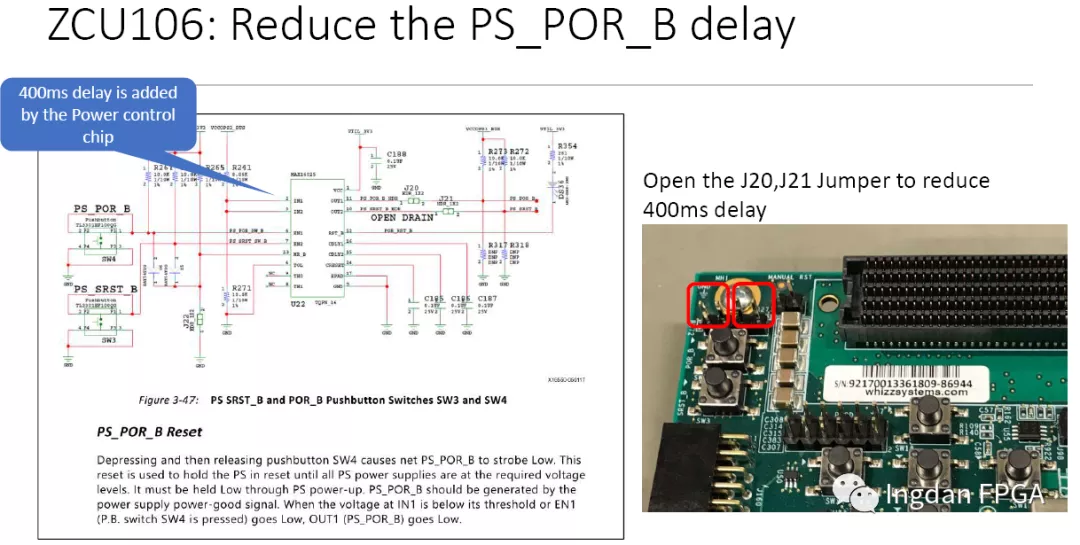

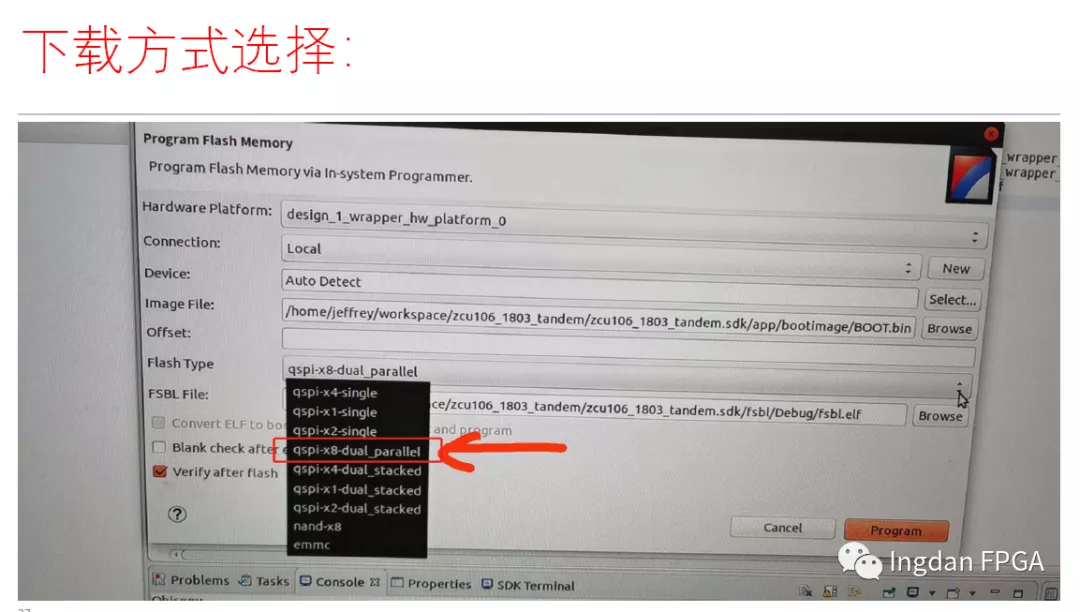

嗨,PCIe-Spec定义在稳定供电后100ms,PCIe设备必须为链路训练做好准备。使用7系列Zynq设备无法达到此时间。我使用了两种方法来减少启动时间: - 优化FSBL以达到SPI控制器的最大

2020-06-09 16:42:15

Altas200 A2模块的调试串口、PCIE接口。提供的默认PCIE测试工程功能如下:

图 2-1PCIE接口demo说明

默认提供的PCIE接口测试demo功能如图所示,主要功能组成包含如下几个

2023-09-05 14:39:57

功能,1、FPGA是不是可以直接通过PCIE操作DDR完成DMA操作?2、在操作过程中CPU是一个旁观者的角色吗?3、地址转换,DDR接口操作等都是由CPU内部的硬件完成?CPU在FPGA操作DDR的过程中,完全不受影响的工作吗?多谢!

2016-04-06 16:24:36

刚接触PCIe,想用PCIe口与PC通信,EP模式。把板子插到PC上之后,通过windriver能查看到TI设备,但是用PCItree不能看到,这样正常吗?我运行的程序

2018-08-07 08:28:19

本帖最后由 eehome 于 2013-1-5 10:01 编辑

1.一个pciex16插座包含16条pcie通道能拆分使用么或者扩展么 比如构成两个独立的pciex8接口如果能,两个能同时

2012-10-19 00:57:16

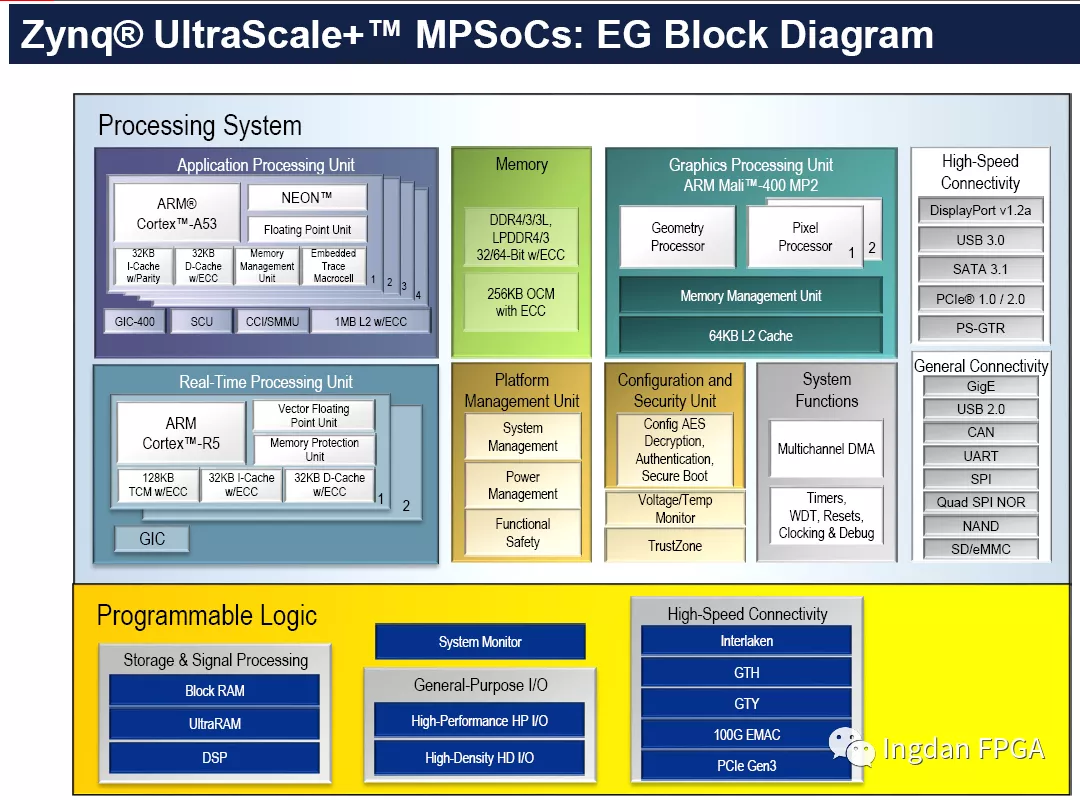

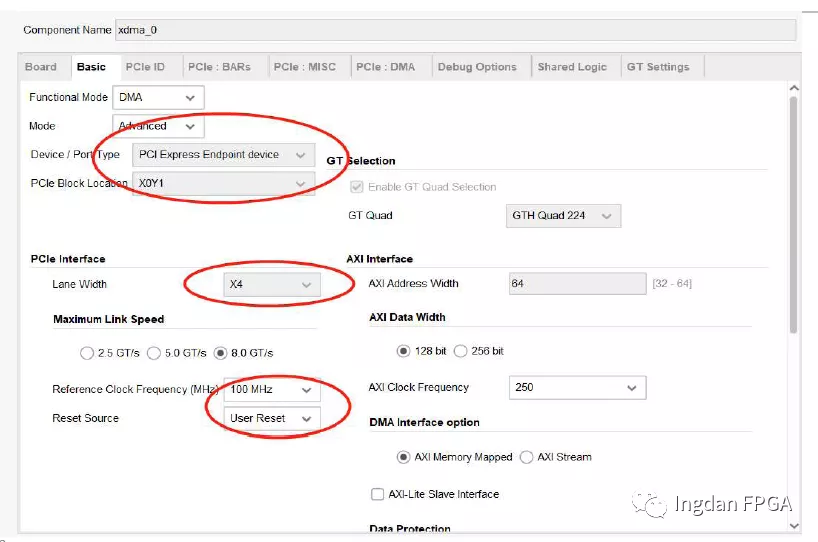

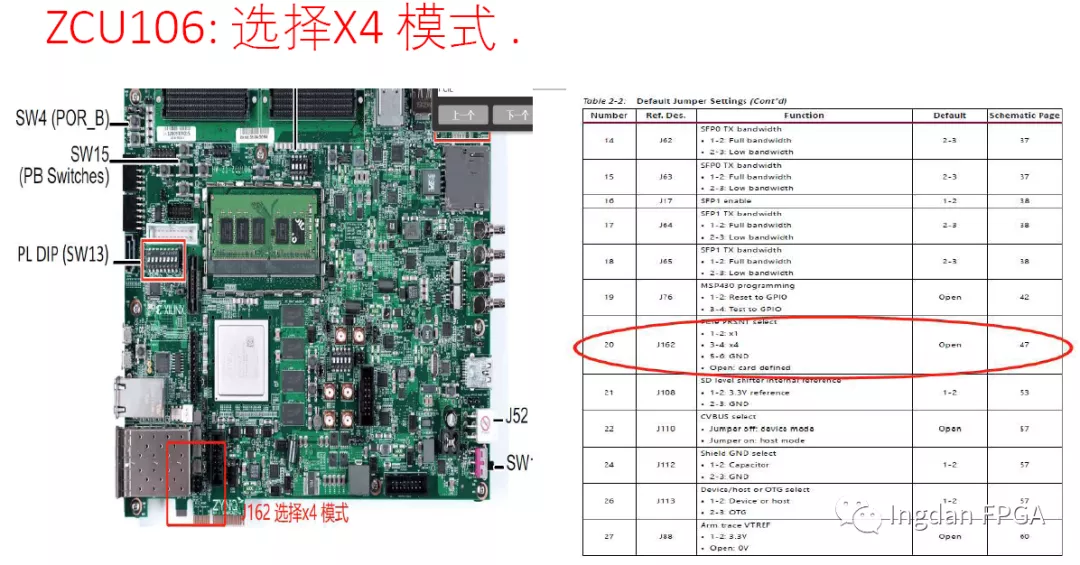

功能丰富的(PL)UltraScale架构在单个设备中。还包括片上存储器,多端口外部存储器接口和丰富的外围连接接口集,尤其是GTH 16.3 Gbps收发器,它具有支持PCIExpress®Gen3

2020-09-03 16:07:35

嗨,大家好,我目前正在创建一个PCIe接口卡,我正处于项目的调试阶段。我试图监视用户_clkrate的AXI突发。关于ILA核心和PCIe端点(在VC709上)我有一些问题。1.当我尝试将

2019-09-25 09:26:14

我配置了一个PCIe端点示例设计,但是我在bitfile编程后找不到Ubuntu中的PCIe设备。任何人都有ZCU106的示例设计?非常感谢!

2019-10-21 09:18:09

一块带有PCIE接口的FPGA,一块PCIE转USB3.0板卡,想通过FPGA控制PCIE转USB3.0板卡,实现USB3.0读入数据,经过FPGA高速处理,不需要经过电脑CPU。请问各位专家:1.

2014-12-25 22:54:58

`描述这款经验证的参考设计是一款 PCIe Gen-3 高速前端卡设计,旨在扩展 PCIe 子系统的 PCB 线迹距离。该电路板适合安装在主板与 PCIe Gen3 插卡之间的 x16 通道宽度

2015-05-08 11:31:58

PCIe Switch IDT-89HPES24T6G2,下游端口接了4路PCIe x1,第4路(PE5,pcb中红色标识)无法识别,请教大神们,会是什么原因,设计有没有什么问题?差分阻抗都按100Ω设计的,第4路走线最短反而识别不到。。。相关设计请见附件。感谢大佬们!!!

2020-01-08 15:02:27

各位大神好,TI专家好!本人使用自己画的DSP6678板卡,将PCIe接口通过转接板卡直接连接到机箱的PCIe插槽中,(没有使用官方的那种AMC转PCIe卡)初始化PCIe接口后,上位机PCIe

2018-08-02 07:16:05

labview做上位机 交替发送两针报文 时间间隔100ms要怎么实现 ?第一帧发送100ms后发送第二针,第二针发送100ms后在继续发送第一帧

2019-02-15 09:18:09

系列FPGA实现PCIe接口所涉及的硬件板卡参数、应用层系统方案、DMA仲裁、PCIe硬核配置与读写时序等内容。

2019-05-21 09:12:26

板子接口上。再将 ASM1062 小板接到 PCIE 小板上,将硬盘接到 ASM1062,启动板子。系统会识别到设备,并自动挂载硬盘。在安卓系统中可打开文件管理器看到挂载的设备。2、linux系统下

2020-01-07 20:20:34

The 100MS is an epoxy encapsulated electromagnetic/electrostatic interference (EMI) shield for use

2008-12-18 20:09:50 19

19 技嘉 8I945P-G 主板 BroadCom PCIe Gigabit LAN 驱动程式.exe

2010-01-26 15:37:04 21

21

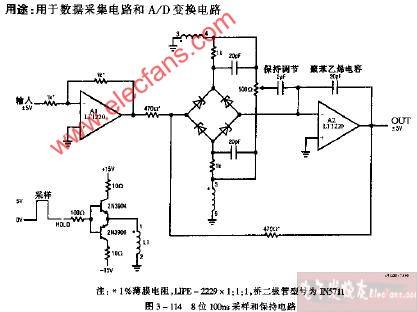

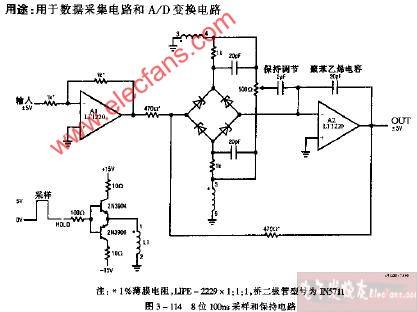

8位100ms采样和保持电路图

2009-06-29 09:56:42 613

613

白皮书 :采用低成本FPGA实现高效的低功耗PCIe接口 了解一个基于DDR3存储器控制器的真实PCI Express (PCIe) Gen1x4参考设计演示高效的Cyclone V FPGA怎样降低系统总成本,同时实现性能和功耗

2013-02-26 10:04:25 72

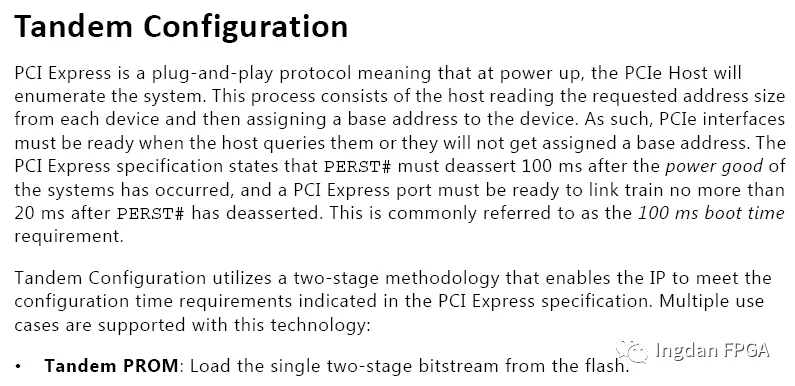

72 根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspci可能无法检测到基于FPGA

2017-02-07 20:55:41 2914

2914

设备间,其是一种基于数据包、串行、点对点的互连,因此所连接设备独享通道带宽。根据使用的版本号和通道数,其性能具有可扩展性。对于PCIe 2.0,每条通道在每个方向上的数据传输速率是5.0 Gbits-1。从PCIe1~PCIe16,能满足一定时间内出现的低速设备和高速设备的需求

2017-10-13 10:41:03 24

24 PCIE总线的多DSP系统接口设计

2017-10-31 10:42:03 23

23 旋风V阿瓦隆ST接口PCIe解决方案

2018-01-29 15:11:03 2

2 根据PCIe的协议,当设备启动后,PCIe设备必须满足启动时间的要求,即上电后100ms内,完成PCIe设备的初始化。如果不能满足PCIe设备启动时间的要求,则lspci可能无法检测到基于FPGA

2018-06-19 10:24:00 7625

7625

当然,热插拔不仅仅是硬件的事,其需要软硬件协同实现。要想实现热插拔功能,操作系统、主板热插拔驱动器、PCIe卡设备驱动以及PCIe卡硬件功能都必须支持热插拔,缺一不可。从PCIe卡设备硬件功能的角度来看,其需要支持Quiesce命令、Pause命令(可选)、Start命令和Resume命令。

2018-09-06 09:20:38 19624

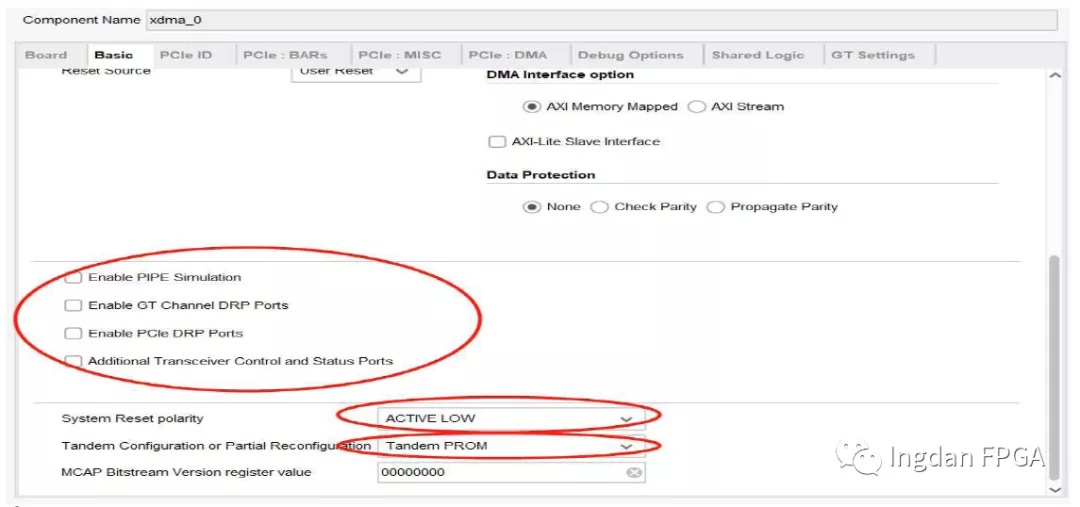

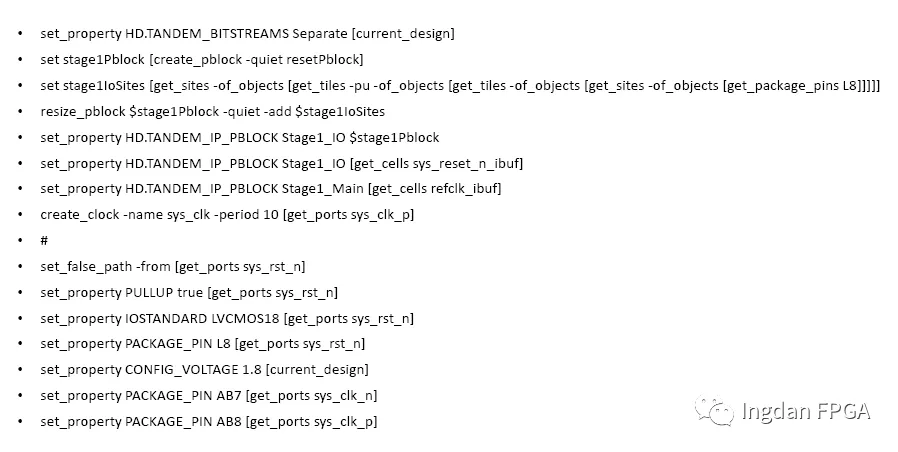

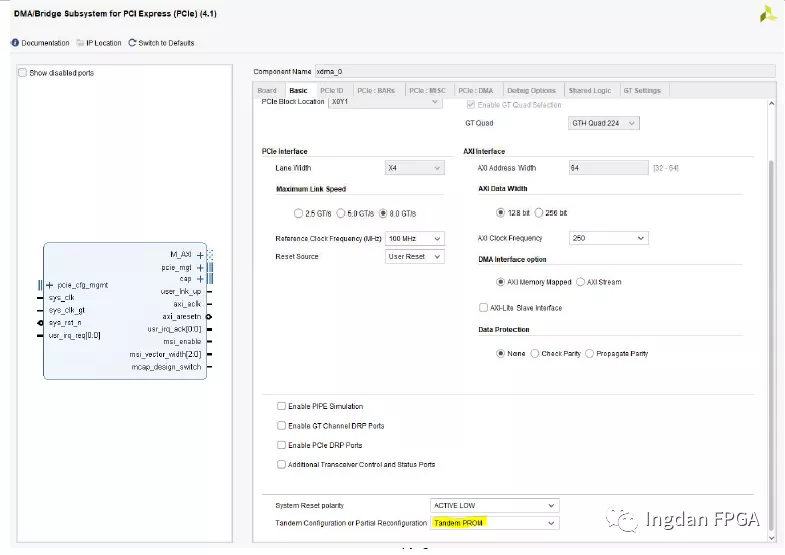

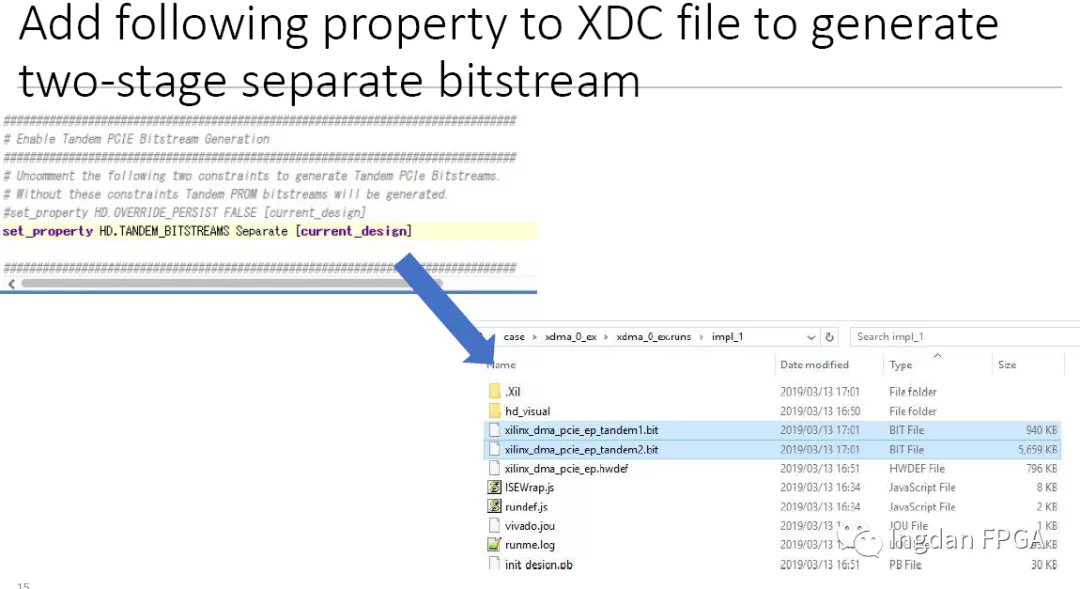

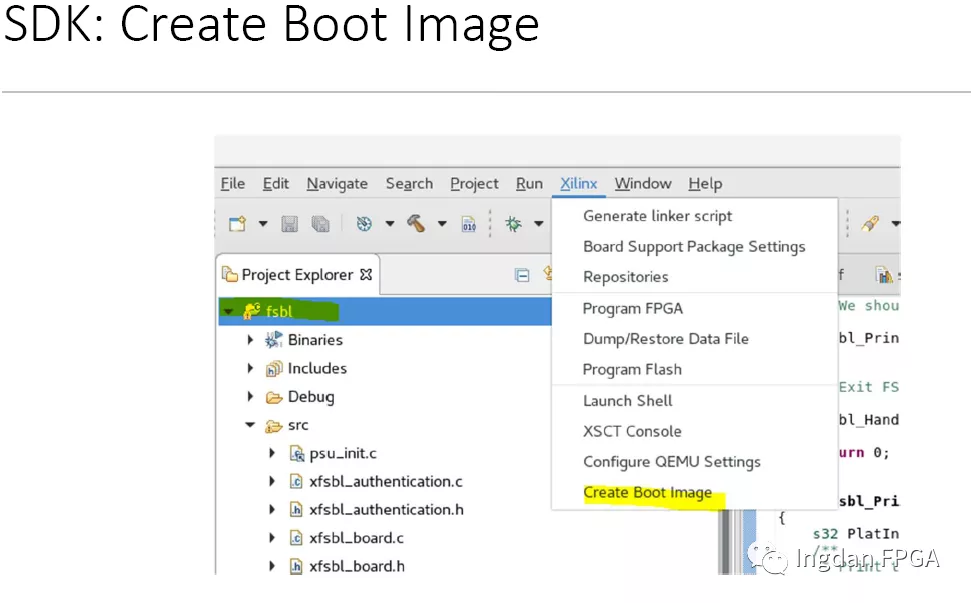

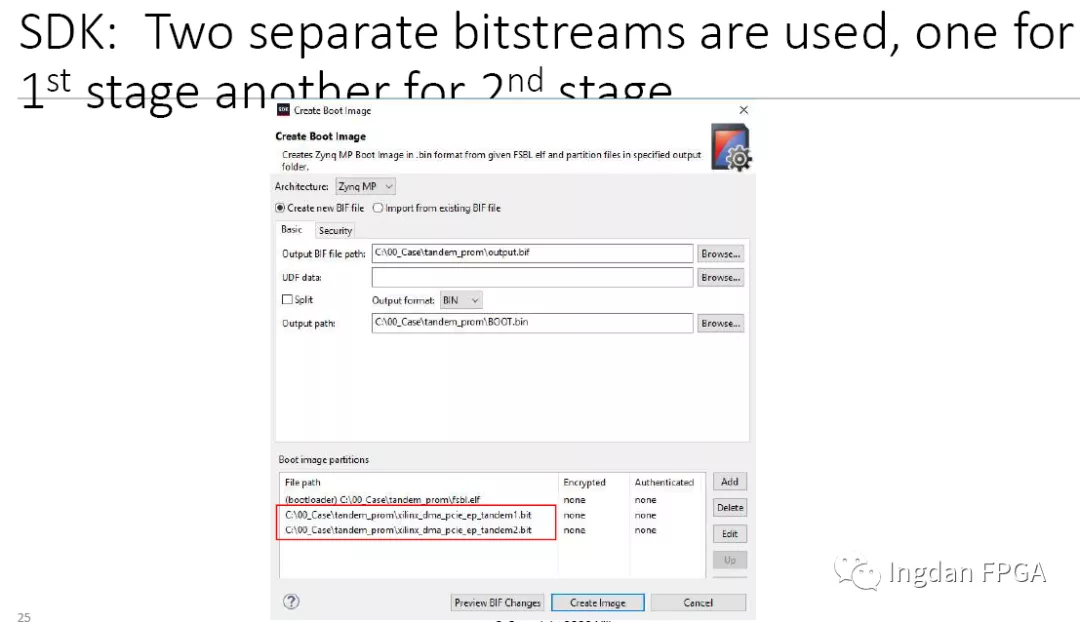

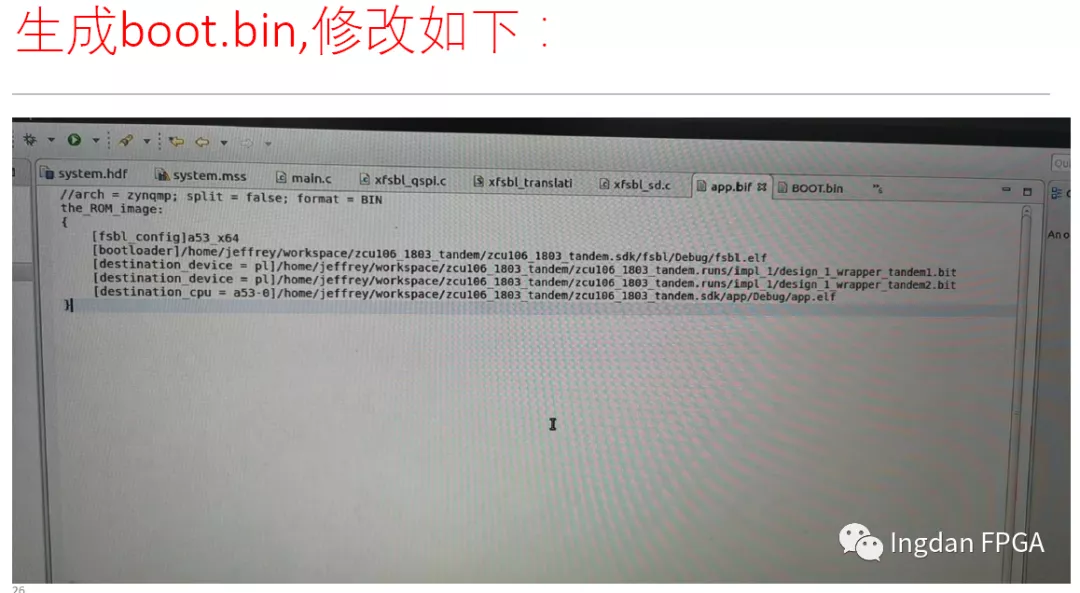

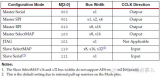

19624 了解如何针对KCU105评估套件创建Tandem设计。

Tandem方法将比特流分成两部分,允许首先加载比特流的PCIe部分,以确保在系统期间枚举PCIe块

2018-11-22 06:00:00 5172

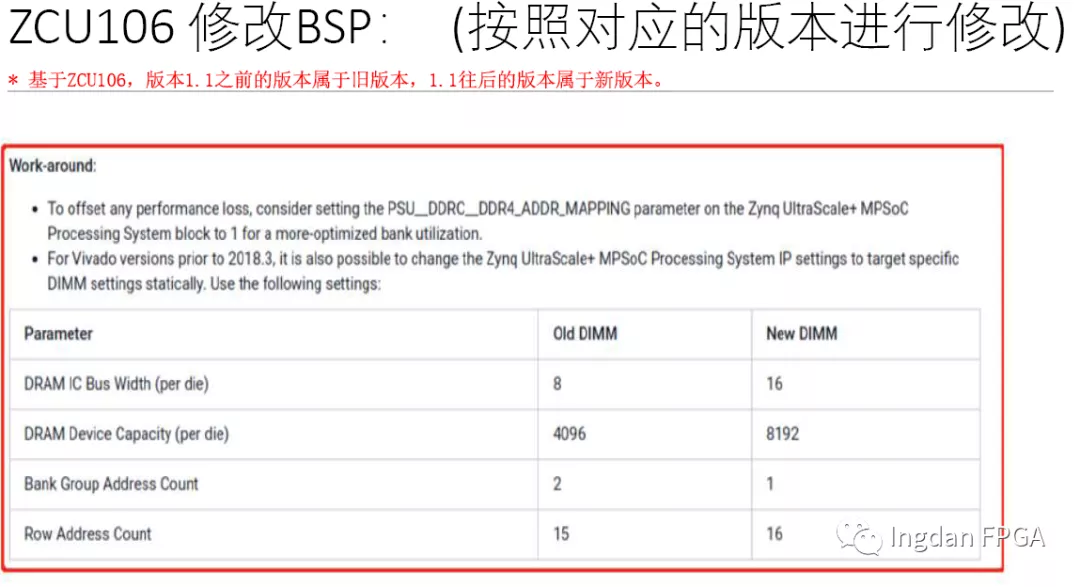

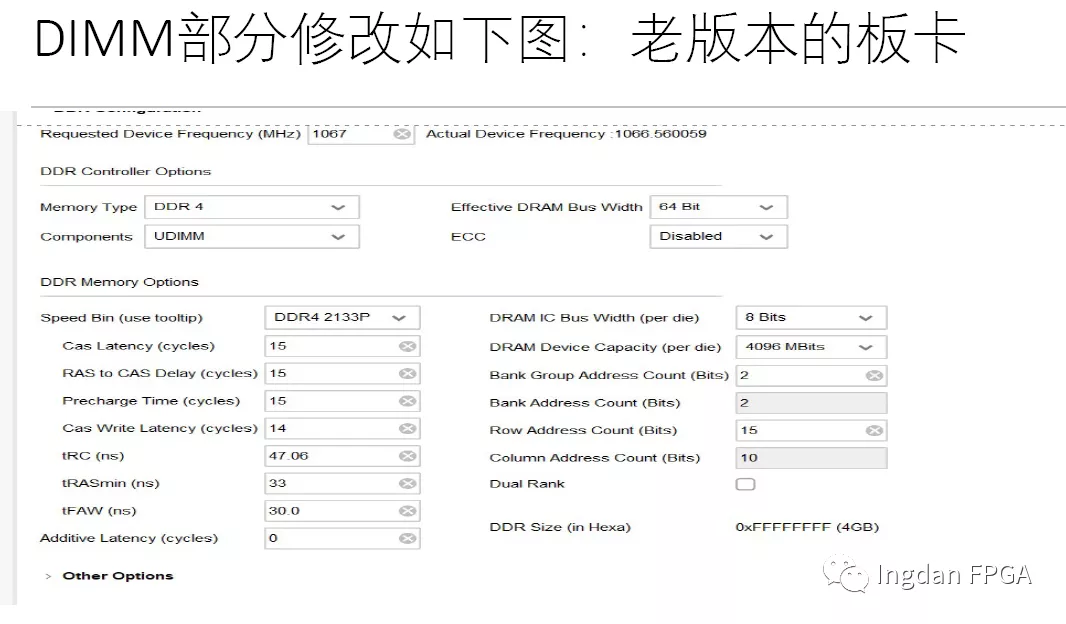

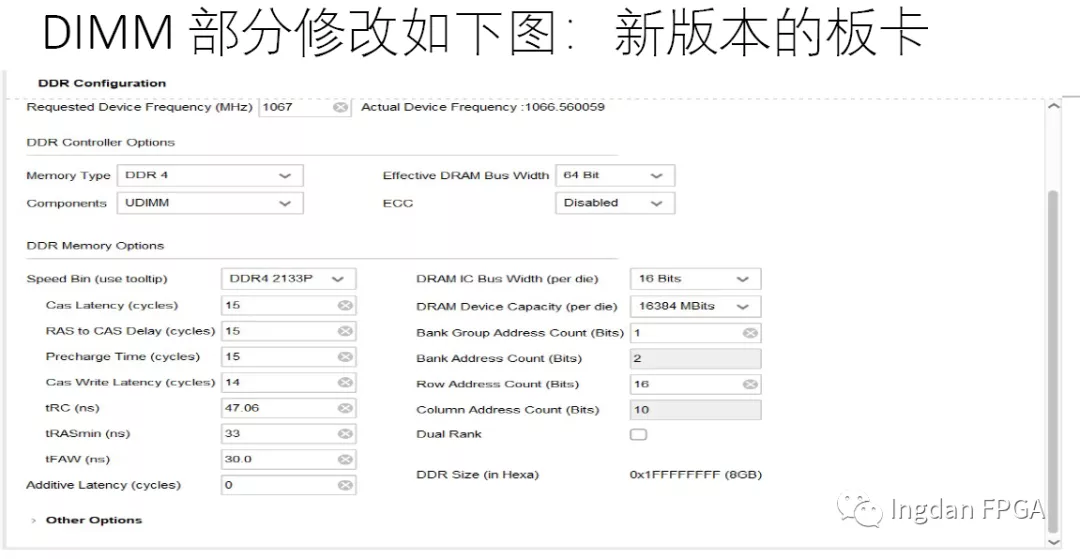

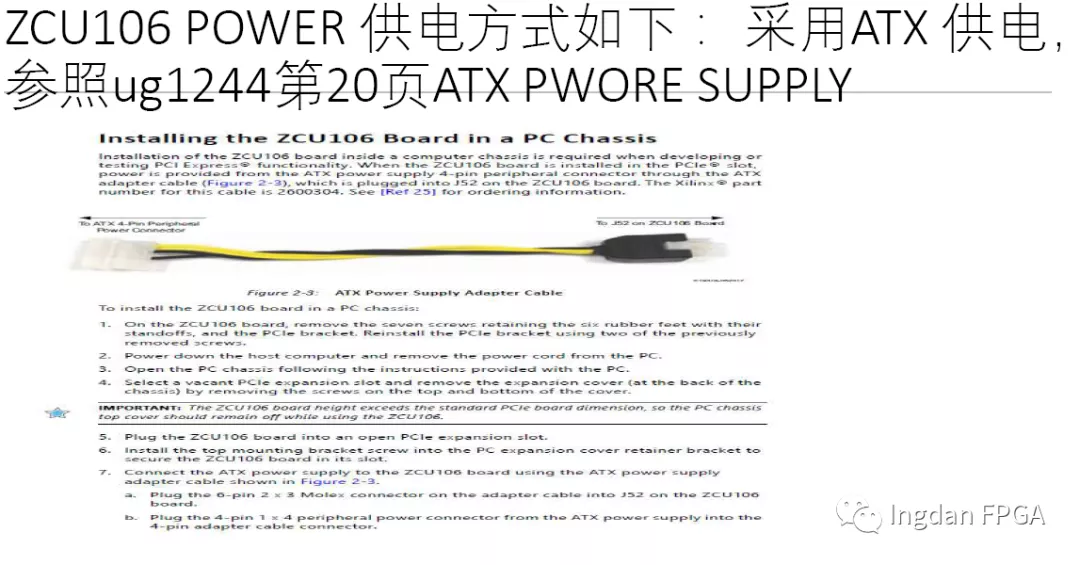

5172 ZCU106 评估套件可帮助设计人员为视频会议、监控、高级驾驶员辅助系统 (ADAS) 以及流媒体及编码应用快速启动设计。此套件包含一个 Zynq UltraScale+ MPSoC EV 器件,并支持所有可实现各种应用开发的主要外设及接口。

2019-07-31 17:00:49 5551

5551 电子发烧友网为你提供Broadcom(ti)P2100G - 2 X 100GBE PCIE NIC相关产品参数、数据手册,更有P2100G - 2 X 100GBE PCIE NIC的引脚

2019-07-04 09:51:00

电子发烧友网为你提供Broadcom(ti)P1100G - 1 X 100GBE PCIE NIC相关产品参数、数据手册,更有P1100G - 1 X 100GBE PCIE NIC的引脚

2019-07-04 09:51:00

EVB评估底板也在进行不停地完善与更新,以适应最新的功能评估需求。PCIe1接口具有2.5Gb/s的高速数据传输能力,且接口仅有3对差分信号组成,因此在嵌入式领域得到越来越多的应用。 在当前最新的ESMARC主板中(包括ESM6802G和ESM7100),我们对PCIe1接口信号的引出脚位进行了优化调

2020-02-07 11:00:47 1495

1495

)和双核Arm Cortex-R5F实时处理器,为应用程序开发人员提供了前所未有的异构多处理水平。ZCU106评估板提供了一个灵活的原型平台,具有高速DDR4内存接口、FMC扩展端口、千兆位/秒串行收发器、视频编解码器单元(VCU)、多个外围接口和用于定制设计的FPGA结构。

2020-09-18 08:00:00 44

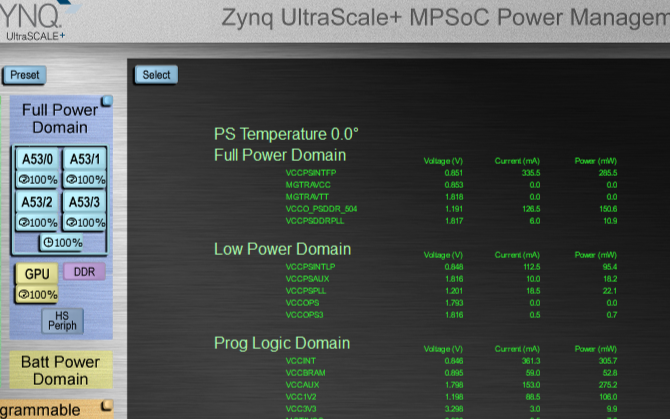

44 作者:付汉杰,hankf@xilinx.com,文章转载自:博客园 不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化

2020-10-10 16:43:07 1886

1886

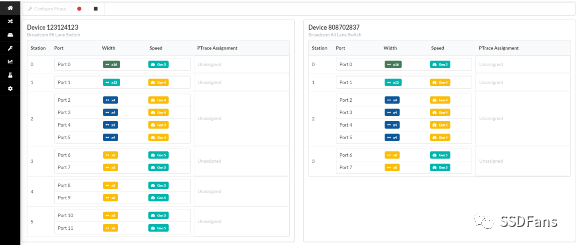

随着PCIe Gen 4和Gen 5的项目开发越来越多,很多公司希望在PCIe链路层注入故障来模拟针对主板/背板一侧,或者外设一侧(如插卡,NVMe SSD等)的各种异常,业内主流的CPU厂商例如

2020-10-16 11:11:38 3938

3938 2021年4月6日 Broadcom最新的PCIe Gen 5 switch芯片内置了SerialTek PCIe抓包分析功能,可以大大方便服务器、存储系统厂商调试PCIe Gen 5在初始化

2021-04-13 15:30:47 4797

4797

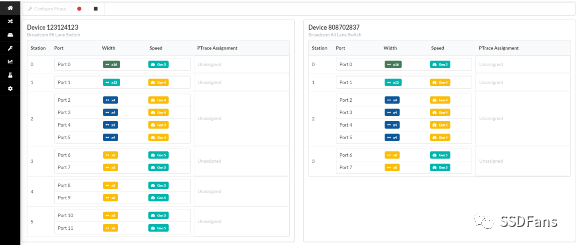

SerialTek是PCIe,NVMe和SAS/SATA协议测试解决方案的全球领先提供商,今天推出的PCIe测试和分析市场的最新技术和产品BusXpertiTAP,支持Broadcom的PCIe嵌入式分析仪技术,这是Broadcom新的PEX89000 Gen5 PCIe交换芯片的一项突破性功能。

2021-04-13 15:34:21 5505

5505

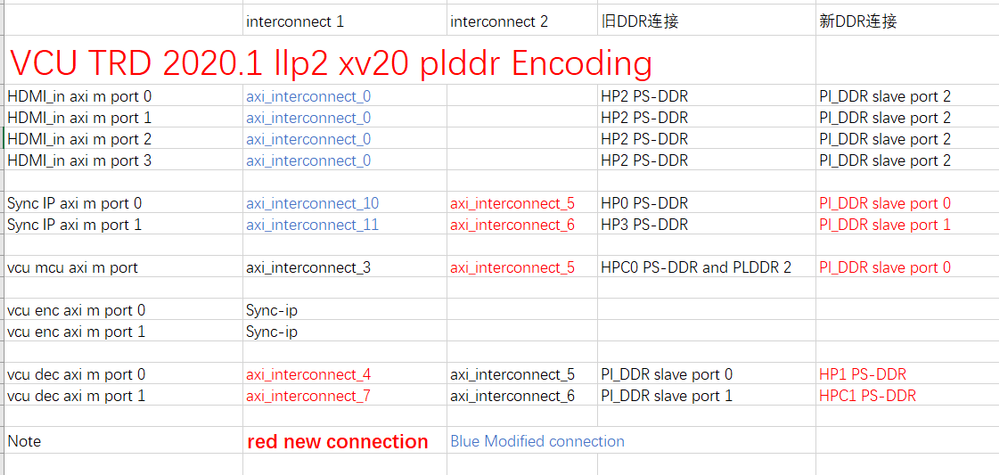

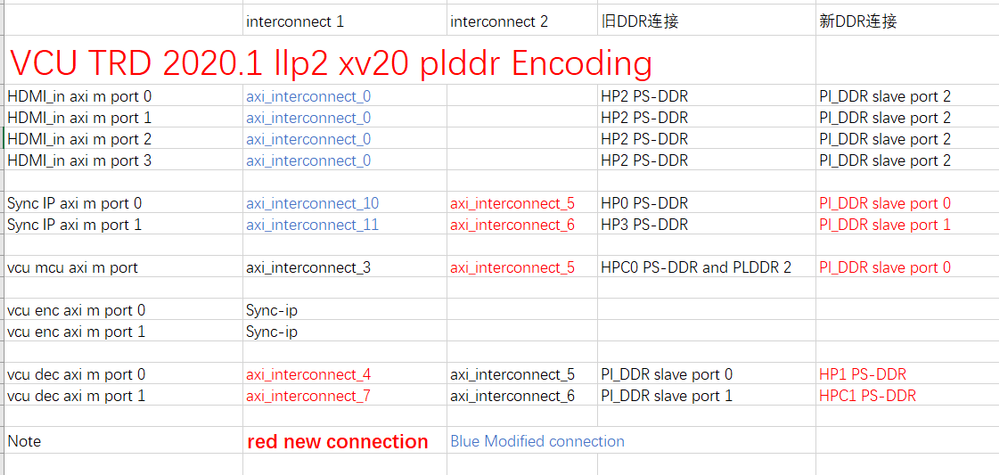

DDR。如果PS DDR已经被其它应用占用,也可以让编码使用的PL DDR。在VCU TRD 2020.2的例子zcu106_llp2_xv20基础上,做如下更改,可以实现使用PL DDR编码。 01硬件

2021-05-07 15:30:13 6222

6222

是Linuxptp,可执行文件是ptp4l。 1在zcu106之间运行1588 下面的命令,在zcu106之间运行1588。运行顺序是先在第一块单板(master)启动1588 master;再在第二块单板

2021-05-13 14:22:28 3315

3315 FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。 为此Xilinx的PCIE Tandem(详见PG156)功能

2021-06-18 14:57:17 3064

3064 /秒的数据链路速度操作,同时具有卓越的内存、存储容量和分段功能,可捕获更大容量的上行和下行流量。 什么是 PCIe 5.0? 第 5 代快速周边组件

2021-06-19 11:04:51 33055

33055 随着英特尔的十一代酷睿发布,PC硬件已经实现了对PCIe 4.0固态硬盘的全面支持。PCIe 4.0接口的全面普及推动了固态硬盘提速潮,PCIe 4.0逐渐走进了大众的视野,成为购买者选购固态硬盘

2021-09-14 18:09:49 22294

22294 按照在MPSoC上运行基于eglfs_kms的QT应用程序, 可以在MPSoC ZCU106单板的DP上基于eglfs_kms的运行QT应用程序。按照在VCUTRD 2020.1 里设置HDMI-TX显示QT界面, 可以在MPSoC ZCU106单板的HDMI-Tx上基于X11的运行QT应用程序。

2022-08-02 09:04:22 2418

2418 。如果PS DDR已经被其它应用占用,也可以让编码使用的PL DDR。在VCU TRD 2020.2的例子zcu106_llp2_xv20基础上,做如下更改,可以实现使用PL DDR编码。

2022-08-02 09:12:42 535

535

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency NV16 提供了详细命令。下面的命令,能表现得更加稳定。

2022-08-02 16:31:13 955

955 PCIe M.2 接口规范

2023-06-19 10:02:30 18

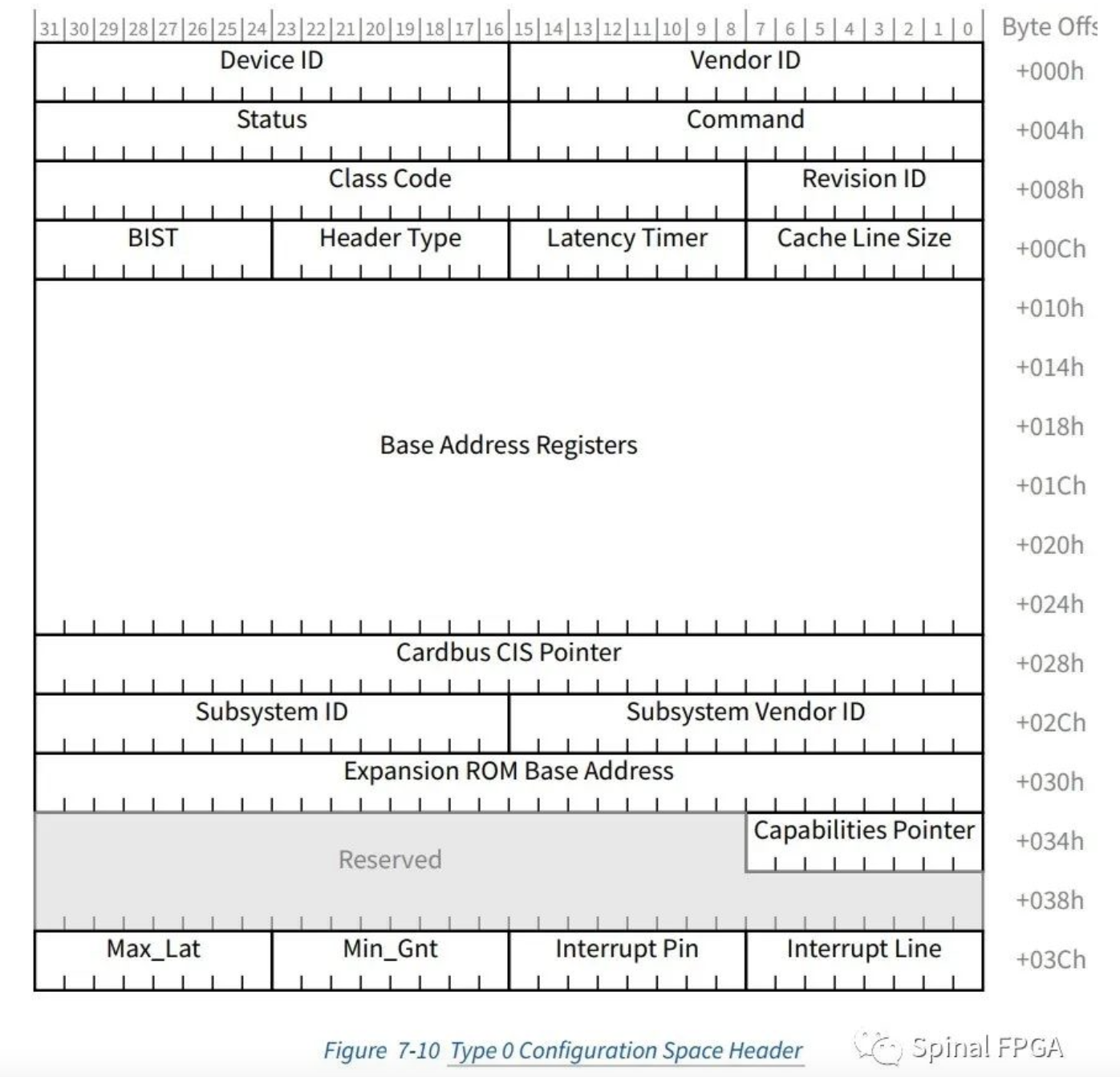

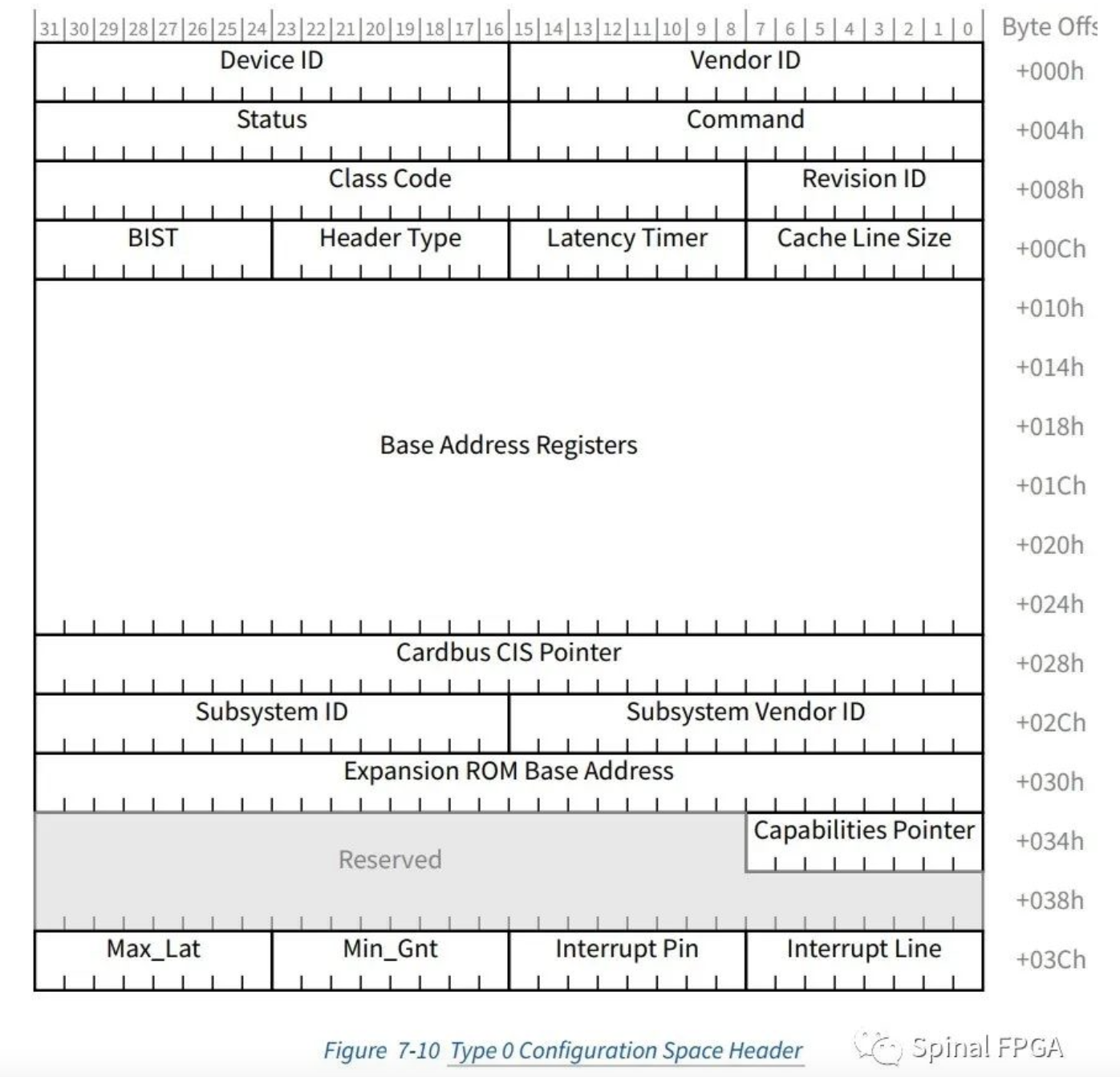

18 最近在研究cocotbext-pcie的实现,对于学习PCIe还是挺有帮助的,陆陆续续做个总结,有时间也会在SpinalHDL下实现类似的方针功能。

2023-07-03 17:47:34 2293

2293

PCIe是一种高速串行计算机扩展总线标准,自2003年推出以来,已经成为服务器(Server)和PC上的重要接口。今天为大家简单介绍一下PCIe的发展历史以及它的工作原理。 一、PCIe的由来

2023-07-04 18:15:03 9791

9791 本文将侧重于概述如何以 ZCU106 开发板为目标,创建和运行仅限 TX 的设计

2023-07-10 16:36:17 589

589

,PCIe标准几经迭代。PCIe最初作为一种串行接口引入,用于替代众多主板架构使用的并行总线, 但PCIe拥有一项独特特性:通道数量可从1个扩展至32个。 借助这一并行总线特性,PCIe兼容设备之间可以根据数据传输要求,建立宽度为1个、2个、4个、8个、16个甚至高达32个通道的链路

2023-11-30 12:15:01 310

310

一种计算机总线技术,用于连接外围设备和主板,提供快速的数据传输速度。 PCIe有广泛的应用,包括用于扩展卡、显卡、网卡等外部设备的连接。与传统的PCI总

2024-01-30 16:09:25 503

503 Transaction Layer的所有功能特性,不仅内置DMA控制器,而且具备AXI4用户接口,提供一个高性能,易于使用,可定制化的PCIe-AXI互连解决方案,同时适用于ASIC和FPGA。

2024-02-21 15:15:03 144

144

电子发烧友App

电子发烧友App

评论