一、概述

在我们的各种硬件产品中,经常会用到IIC总线,IIC是一种两线接口(Inter-Integrated Circuit)。它是一种串行通信总线,使用多主从架构,是由飞利浦公司在1980年代初设计的,方便主板、嵌入式系统或手机与周边设备组件之间的通讯。由于使用简单,它被广泛用于微控制器与传感器阵列、显示器、EEPROM、IOT等设备之间的通信。

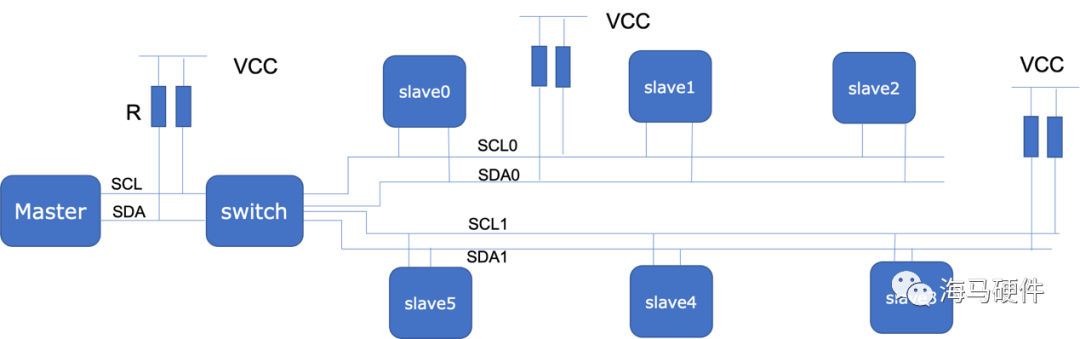

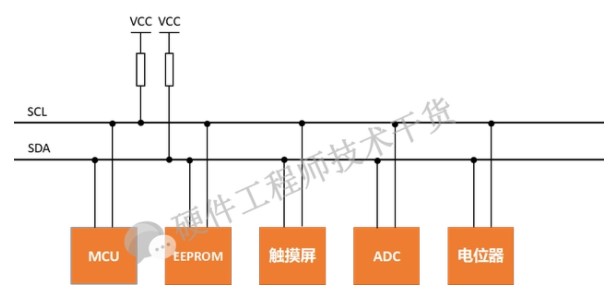

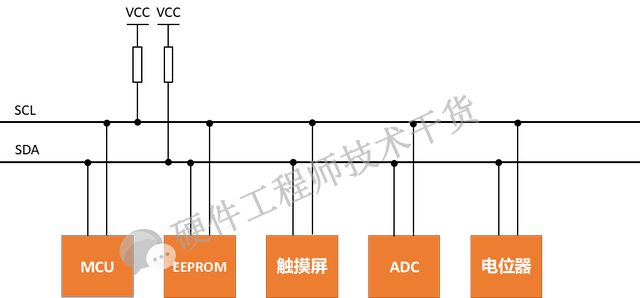

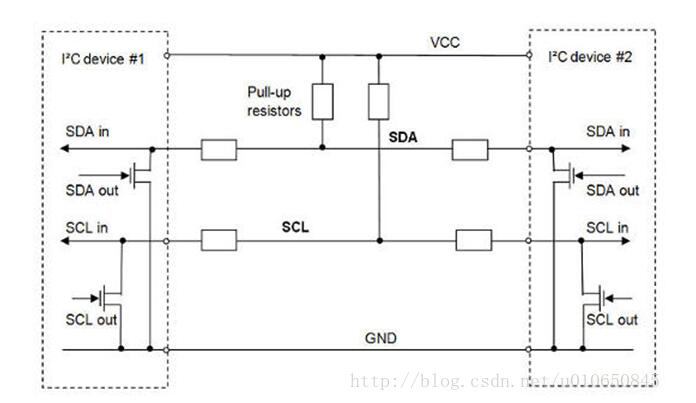

图1 IIC常用链路拓扑

IIC的主要特点如下:

只需要两条总线,串行数据线(SDA),串行时钟线(SCL);

没有严格的波特率要求,主设备生成总线时钟;

所有组件之间都存在简单的主/从关系,连接到总线的每个设备均可通过唯一地址进行软件寻址;

IIC是多主设备总线,可提供仲裁和冲突检测;

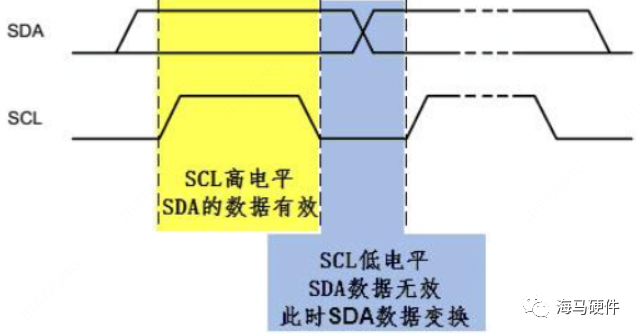

SDA 线上的数据必须在时钟的高电平周期保持稳定,数据线的高或低电平状态只有在 SCL 线的时钟信号是低电平时才能改变;

常用速率如下:普通模式:100kHz;快速模式:400kHz;高速模式:3.4MHz;

二、物理及协议层

2.1 硬件层

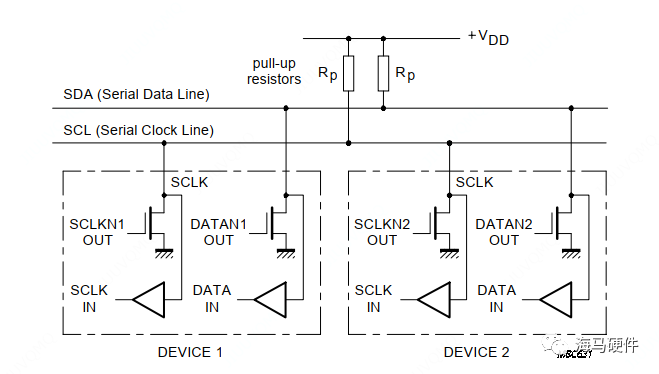

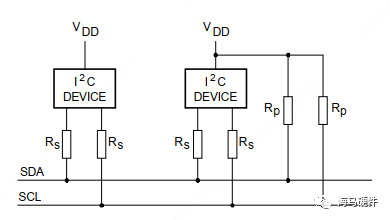

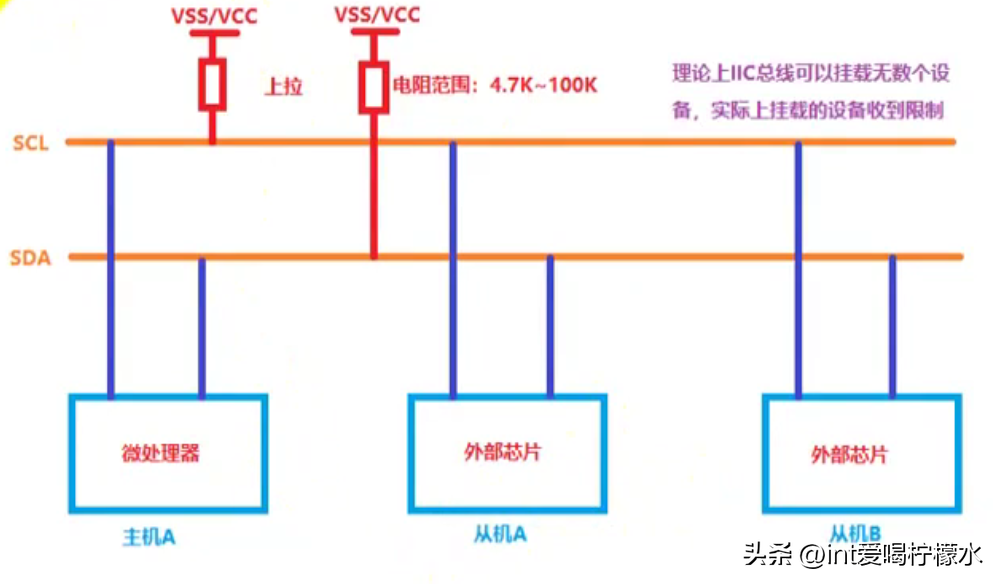

SDA和SCL都是双向线路,都通过一个电流源或上拉电阻连接到正的电源电压,连接到总线的接口数量主要受总电容限制(一般小于400pF),最大从机数理论上是127个;

由于SDA、SCL为漏极开路结构(OD),因此它们必须接有上拉电阻,阻值的大小可以是 1k8、 4k7 、10k等,当总线空闲时,两根线均为高电平;

图2 IIC总线内部OD门

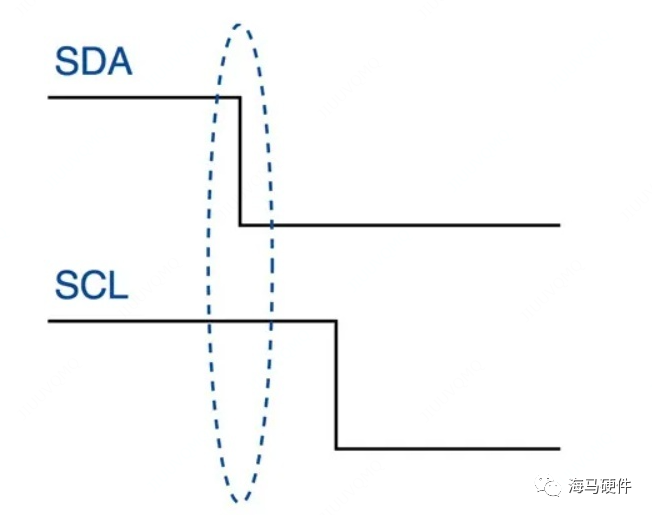

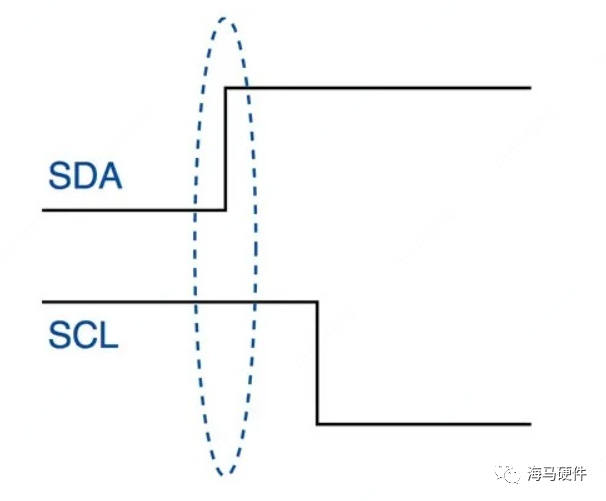

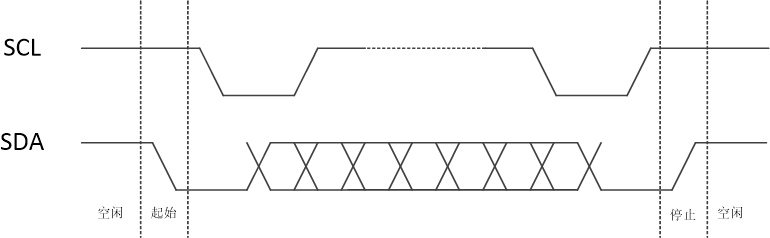

当主设备决定开始或结束通讯时,需要执行以下动作:

当 SCL 是高电平时

SDA 线由高电平向低电平切换当 SCL 是高电平时

SDA 线由低电平向高电平切换

通信开始条件通信停止条件

图3 通信开始/停止条件IIC总线的数据有效性

IIC总线既不是上升沿采样也不是下降沿采样,而是高电平采样;IIC 使用 SDA 信号线来传输数据,使用 SCL 信号线进行数据同步;

SDA在SCL的每个时钟周期传输一位数据。SCL为高电平的时候SDA表示的数据有效,即此时的 SDA 为高电平时表示数据“1”,为低电平时表示数据“0”。

当 SCL为低电平时, SDA 的数据无效,一般在这个时候 SDA 进行电平切换,为下一次表示数据做好准备。

图3 数据有效性

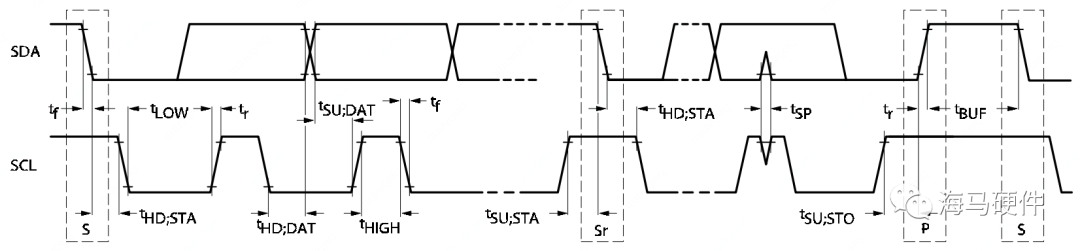

IIC总线的F/S模式器件的时序定义

在测试IIC总线的时候时序测试尤为重要,也是IIC信号完整性测试的主要模块,很多情况下IIC通信问题都是时序不对导致的。IIC总线在快速模式和普通模式下的时序定义如下图;

图5 IIC总线在F/S模式时序定义

重复起始条件的建立时间(tSU;SAT)

起始条件的保持时间(tHD;SAT)

数据保持时间(tHD;DAT)

数据建立时间(tSU;DAT)

SDA和SCL信号的上升时间(tr)

SDA和SCL信号的下降时间(tf)

停止条件的建立时间(tSU;STO)

停止和启动条件之间的总线空闲时间(tBUF)

测试信号时序时需要注意具体的波形卡点位置,卡点位置不对情况下会导致测出来的数据不是真正的实际数据;具体的卡点位置还要参考被测单板所使用的芯片规格书的要求,根据具体的datasheet要求来测试卡点,一般情况下这三种情况较多:【10%,90%】、【0.8V,2.0V】、【0.3VDD,0.7VDD】;

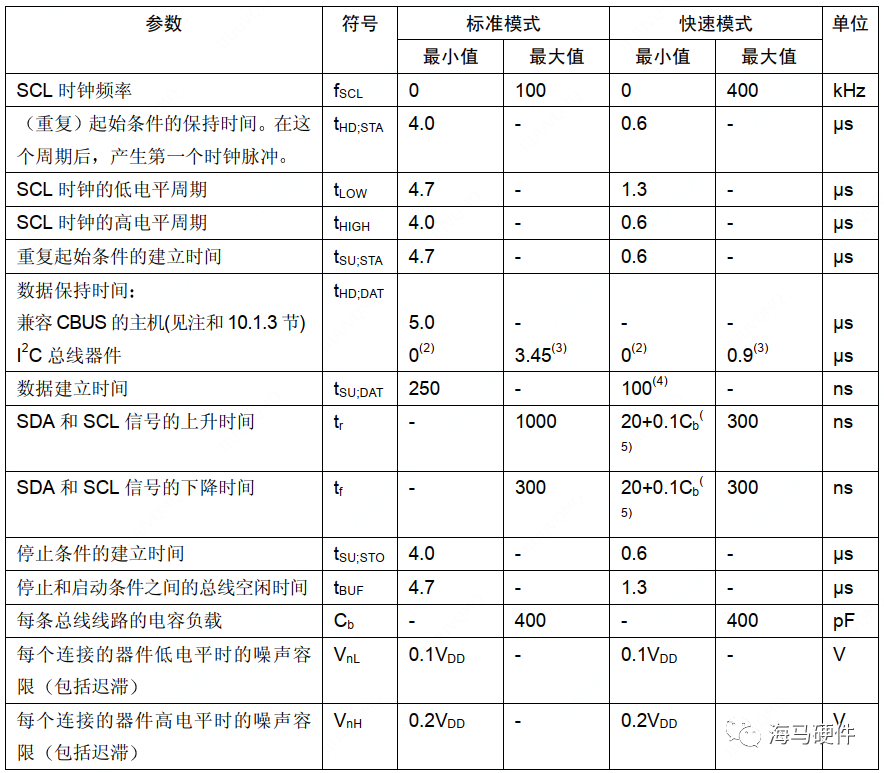

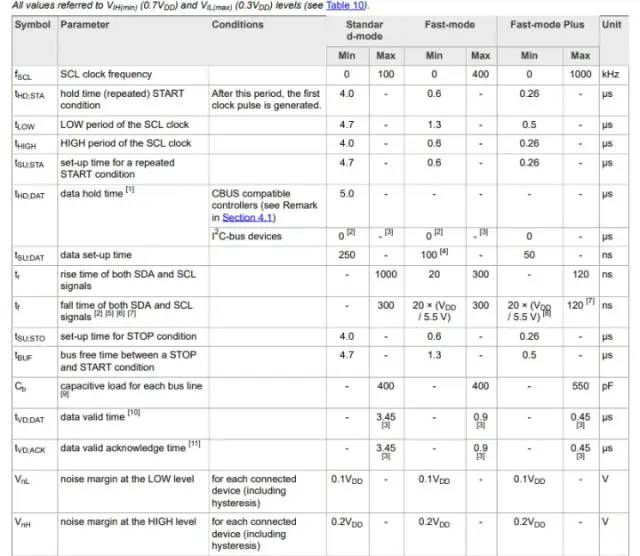

F/S模式IIC总线器件SDA和SCL总线时序标准

在标准模式和快速模式情况下,总线的时序标准是一致的,无论在哪种产品都要以如下标准来判定时序测试的通过与否。

图6 F/S模式IIC总线器件SDA和SCL总线时序标准

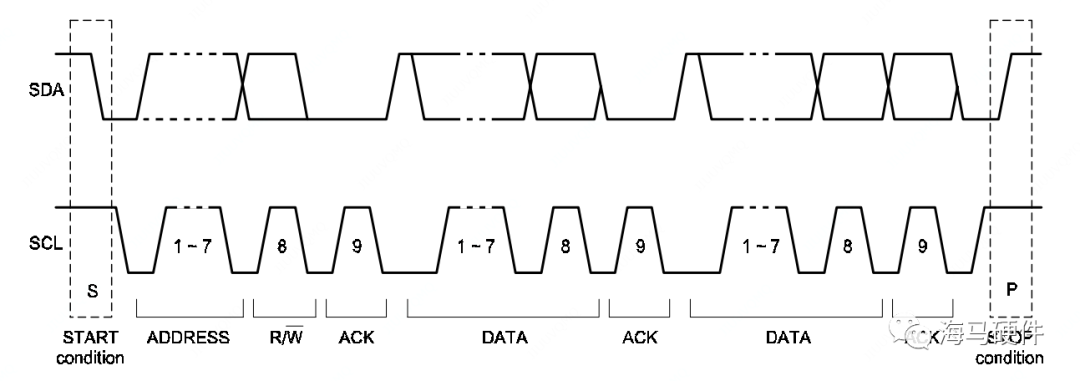

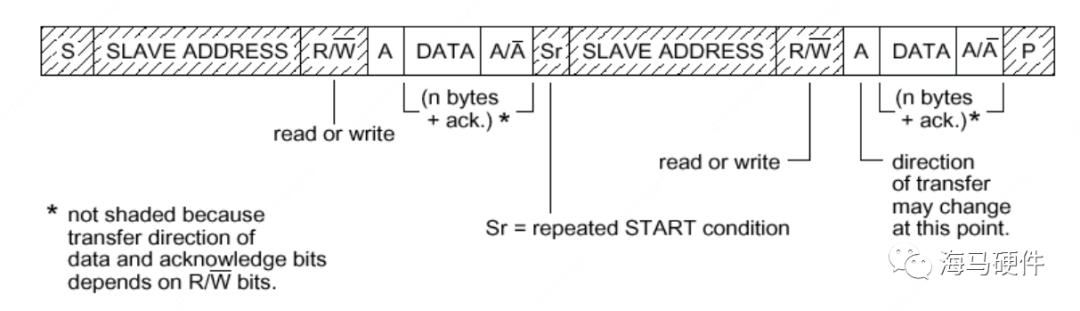

IIC总线的数据传输格式(7位寻址)

IIC总线寻址方式分为7位寻址和10位寻址,因为目前我们硬件产品所用到的都是7位寻址方式,所以介绍一下7位寻址模式的数据传输格式。

图7. 7位寻址方式数据传输格式

如上图所示:在起始条件 S 后,主机发送了一个从机地址,这个地址共有 7 位;第8位是数据方向位 R/ W; 0 表示发送 (写), 1 表示请求数据 (读);第9位为应答位(ACK),应答位低电平有效;后面为数据传输,每一组数据对应一个应答位。

如果主机仍希望在总线上通讯,可以产生重复起始条件 Sr(restart)和寻址另一个从机或寄存器,而不是首先产生一个停止条件,在这种传输中,一个数据串中可能既包括读也包括写的格式。

图8 带重复起始条件的7位寻址方式数据传输格式

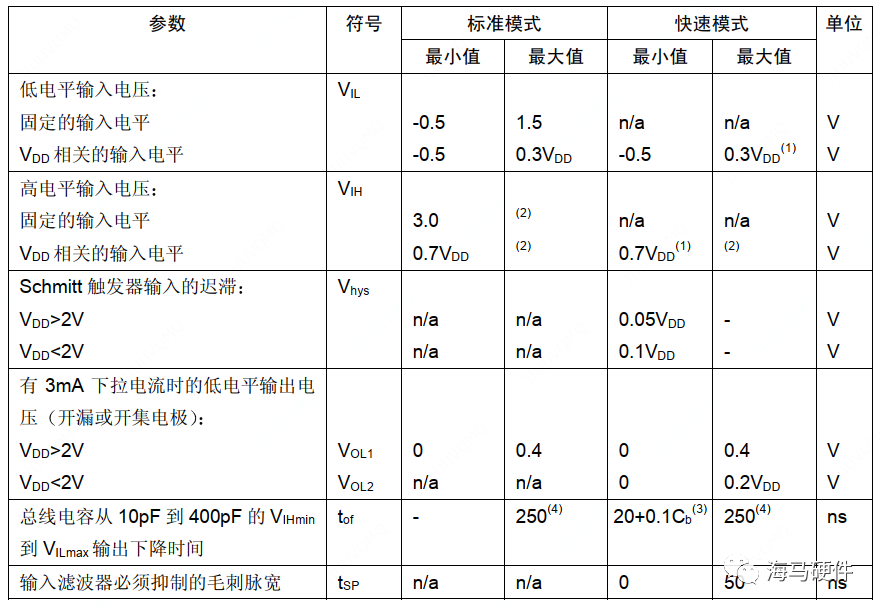

IIC总线器件SDA和SCL的I/O级的特性

1、使用非标准电源电压(不遵从IIC 总线系统电平规定)的器件必须将输入电平连接到有上拉电阻Rp 的 VDD 电压;

2、 最大的 VIH=VDDmax+0.5V;

图9 F/S 模式 IIC 总线器件 SDA 和 SCL I/O 级的特性

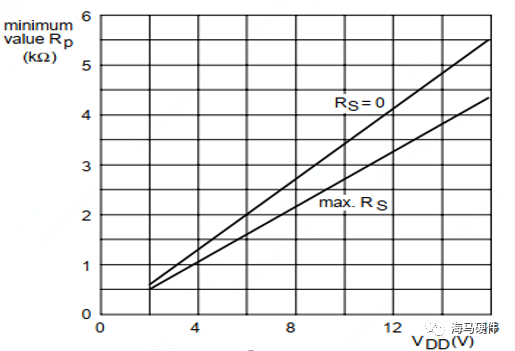

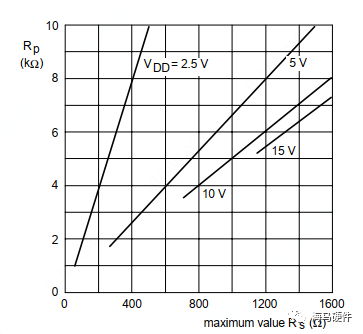

标准模式IIC总线器件电阻Rp和RS的最大和最小值

1. 电源电压限制了电阻 Rp 的最小值 ,因为输出级在 VOLmax=0.4V 时指定的最小下拉电流是 3mA ;

2. 低电平要求的 0.1VDD 噪声容限限制了 RS 的最大值;

3. 总线规定的上升时间及电容的存在限制了 Rp 的最大值 ;

Rp:总线的上拉电阻值;

Rs:总线的串阻值;

图10 IIC上拉和电源供电示意图

最小上拉电阻vs电压串阻vs上拉电阻

2.2 IIC总线固件工作过程

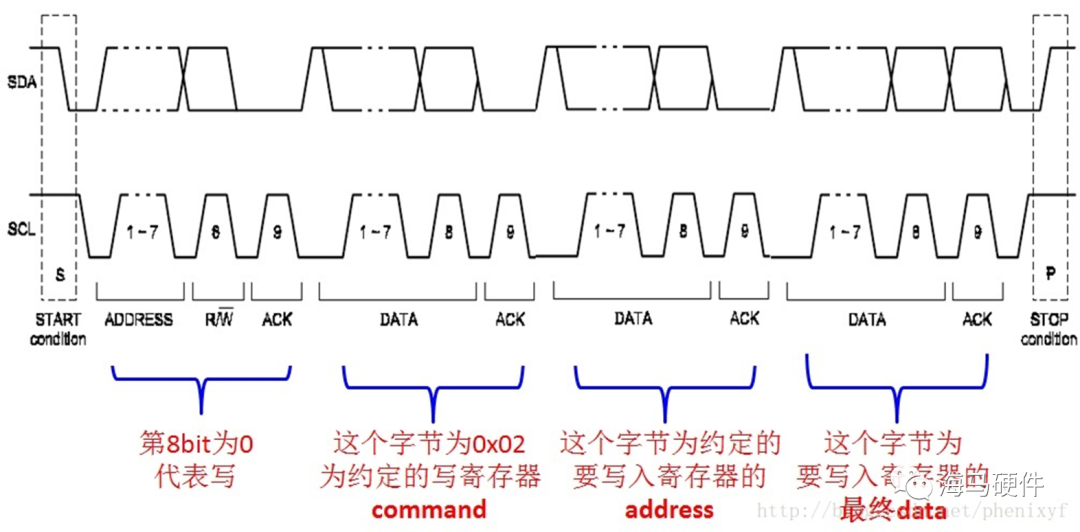

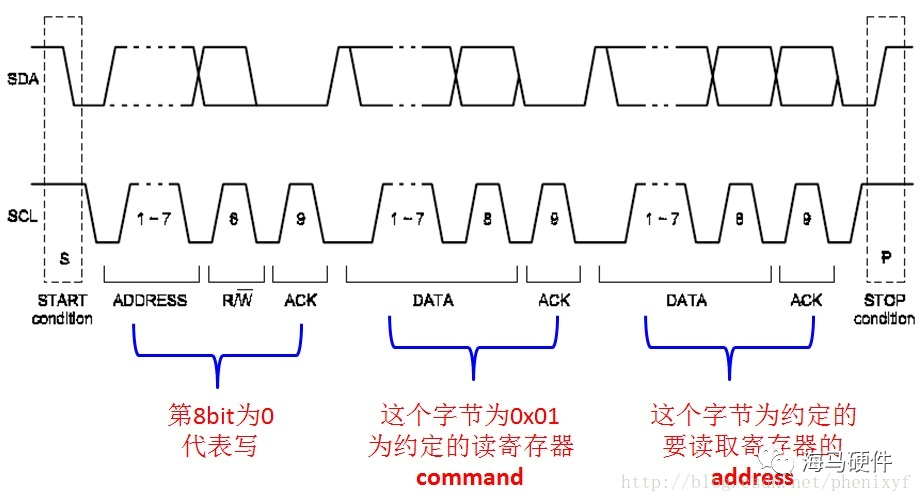

在通信之初,主从机必须根据自己的要求约定好通信规则:command的定义和位置、address的位数和位置。

以读写从机的寄存器数据为例:假设主机寄存器地址为8位、从机寄存器也为8位;约定读寄存器的command为0x01,写寄存器command为0x02;约定主机发起通信后,第一个slave address字节收到ack后,紧跟的一个字节为command,再下面一个字节为寄存器地址address

写(主往从设备写数据)

主机:发起通信,按约定依次写入command、要写入的从机寄存器地址address和要写入的数据data;

从机:分别提取command、address和data,根据command做出判断是读还是写,将data存入入与到接收的address对应的寄存器;

图13 主设备往从设备写数据格式

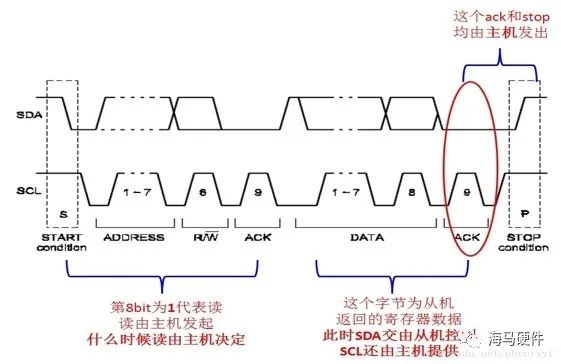

读(主设备读取从设备数据)

主机:先发起一次通信,将读command(0x01)和需要读取的寄存器地址address写入总线;

从机:分别提取command和address提取;判读command的定义;根据收到的address,将对应的寄存器数据放入从机的IIC输出buffer;

主机:再次发起一次通信(restart),读取从机的数据;

主设备读取从设备数据格式

restart读取从设备数据格式

三、IIC总线测试分析

几乎所有的iot产品、it产品、摄像机、服务器产品等在单板和整机通信中都会使用到IIC总线用于信息传输,所以对总线的可靠性、稳定性的要求也是非常高,测试的把关需严格要求。

IIC总线测试主要包括主机对从机的读测试和写测试、总线信号的信号质量测试和信号时序测试等。根据所使用的芯片不同,一般需要查找芯片规格书的参数,以制定不同的测试用例参数。

以下是关于IIC总线测试的一些典型问题。

波形畸变

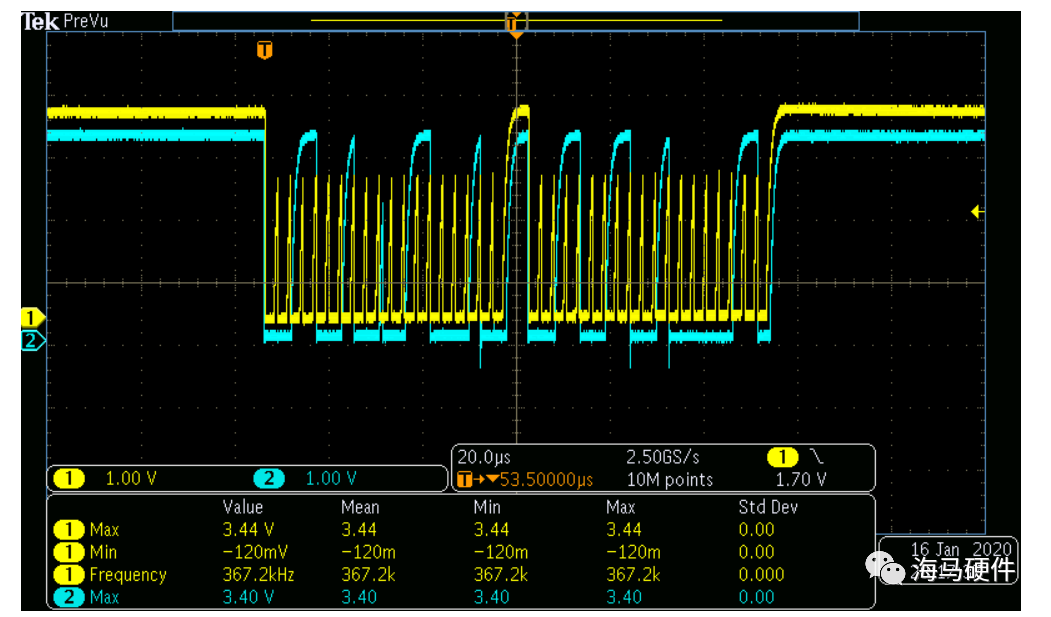

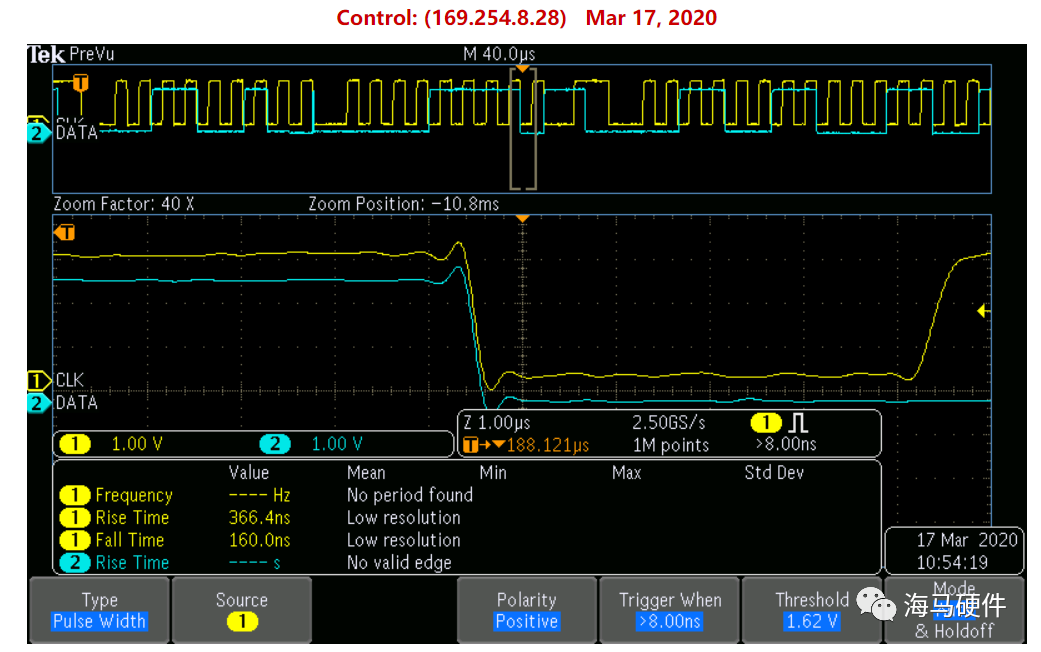

White或Read时发现时钟信号畸变,测试时钟频率约为367kHz。

测试发现SCL波形畸变

整改后SCL波形正常

原因分析:固件配置IIC传输速率错误,没有按照要求的速率配置,实际速率与IC和硬件电路的参数不匹配,导致波形畸变。

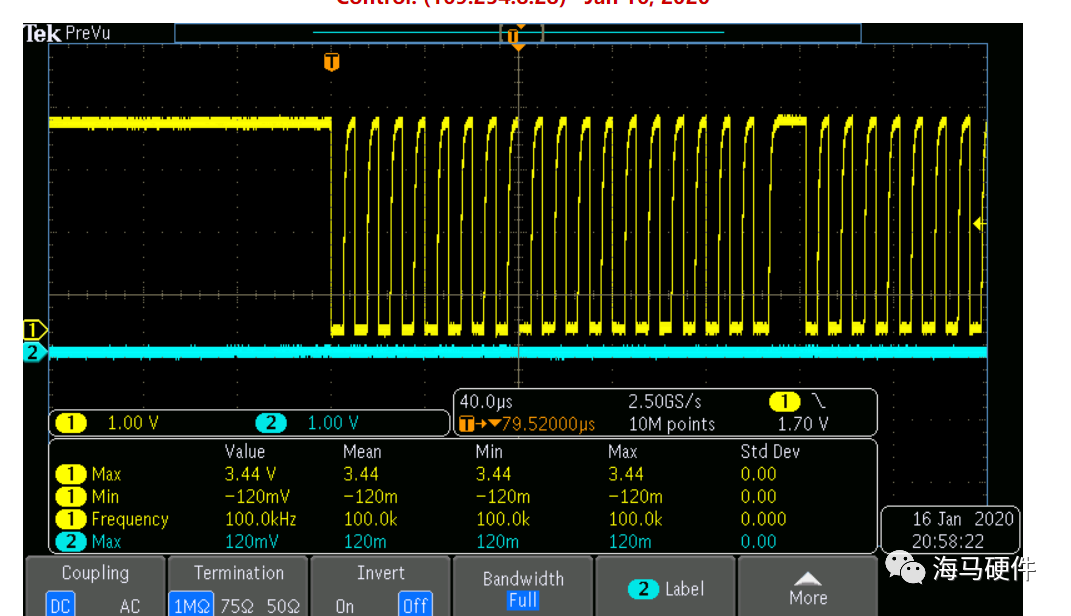

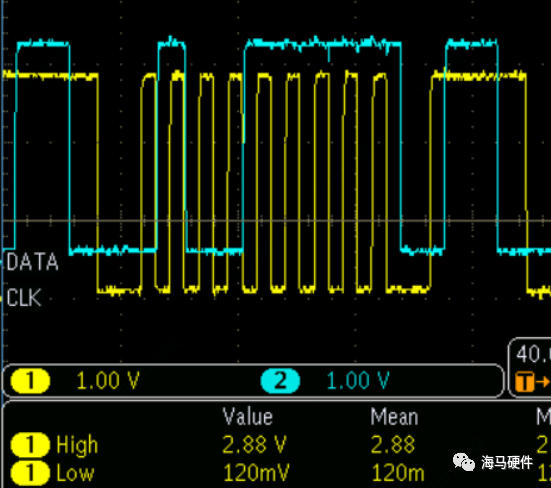

时序问题

MCU和从机之间IIC的SCL上升时间为1.2us,指标要求1us以下。

SCL的上升时间超标

整改后SCL上升时间正常

原因分析:由于此链路的IIC总线的上拉电阻选用太大;导致了SCL的上升时间太大(上拉电阻太大还可能导致电平时间低于预期)。

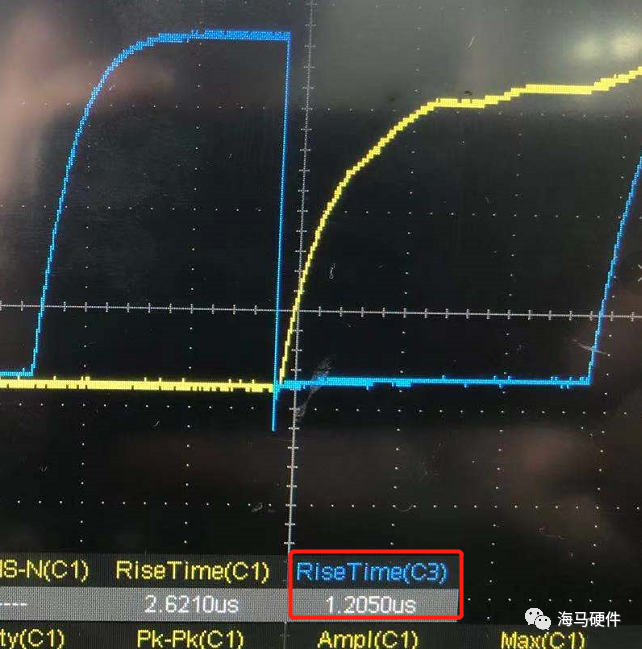

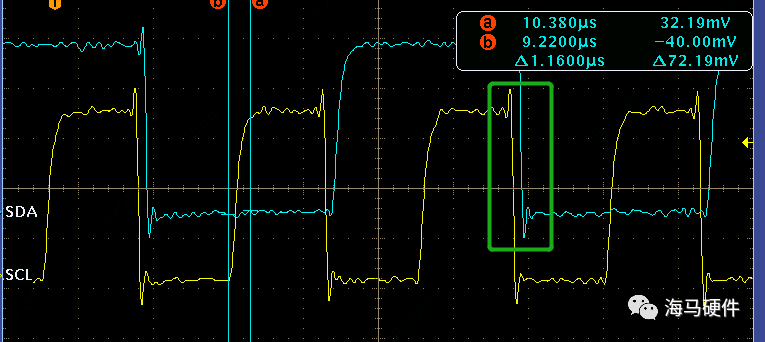

时序问题

数据保持时间不符合要求,数据超前时钟。

时钟在SDA之外变化

整改后SCL在SDA内变化

原因分析:slave芯片部分批次存在固有缺陷,使用旧批次芯片问问题解决。

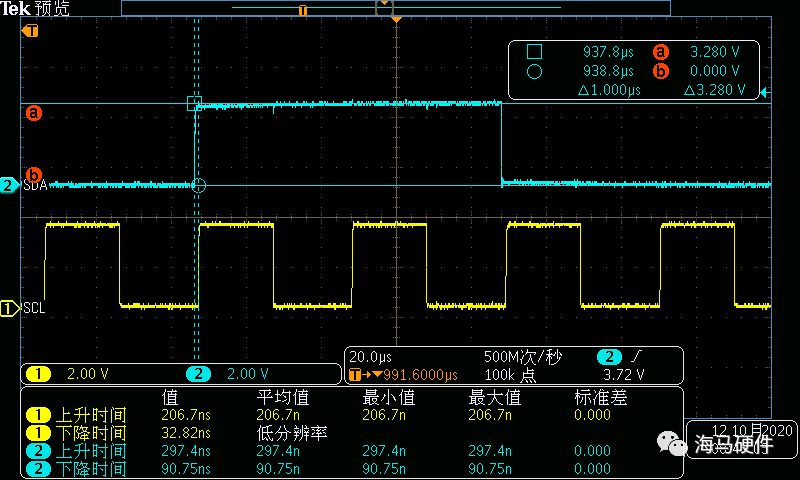

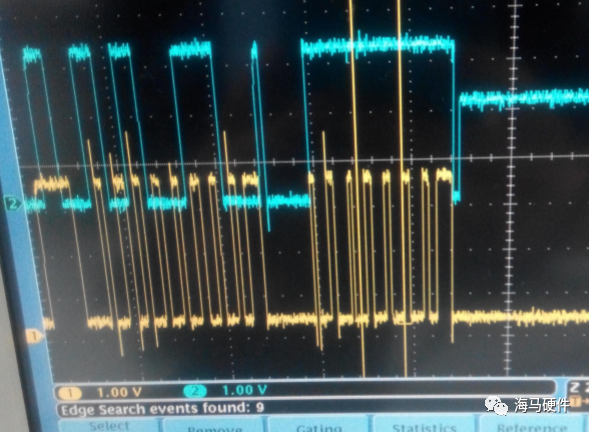

信号质量问题

测试发现IIC总线存在过冲现象,最大电压能达到4.1V;超过芯片能承受的最大3.6V和最小-0.3V电压。

SCL存在过冲现象

整改后SCL在标准内

原因分析:接收端信号震荡导致,存在一定的信号反射导致scl存在尖峰波形超过标准。(注意:探头接地线太长也会导致类似过冲现象)解决方案:接收端加一个22欧姆的电阻作为阻抗匹配,后效果明显改善;

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论