据说SpinalHDL相比chisel更具优势,这让我有了兴趣,今天开始安装搭建。平常用的linux系统的,但是Intel IDEA安装在Ubuntu上的时候总是卡的不行,就放弃了,其实

2021-08-24 14:43:09 8188

8188

SpinalHDL是基于Scala全新的硬件描述语言,解决了不少Verilog等传统HDL语言的痛点,可以快速的完成某些IP的开发,和完美的融入现有的开发流程。 诚然SpinalHDL的学习路线

2023-07-27 09:29:39 766

766

,这个一步需要勾选红框中的这一项;

对应的IDEA中的插件安装Scala和SBT:

Scala插件安装:

SBT插件安装

2.2、JDK安装

直接到JDK官网下载安装包下载即可:

JDK的安装没有

2024-01-21 10:52:10

SpinalHDL中Bundle与SystemVerilog中的packed struct很像,在某些场景下,与普通数据类型之间的连接赋值可以通过asBits,assignFromBits来实现

2022-10-18 14:22:42

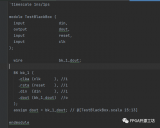

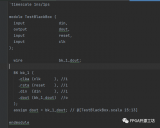

对于仿真信号的驱动,在SpinalHDL里通过“#=”方法实现:值得注意的是当我们的设计里有一个输入信号为:val a=in UInt(32 bits)在进行仿真信号驱动时,下面的写法会报错的:a#

2022-07-27 14:37:46

的Stream总线最近做系统总线的定义,模块之间存在着大量的握手交互,在SpinalHDL中这类总线往往继承于SpinalHDL中的Stream。以下面的总线定义为例:先来说说自己为什么这么来定义总线

2023-01-31 16:38:03

发送一帧总线的最后一拍时重新拉高waitPacket。可以看出,整体的设计思路并不难,我们用Verilog也可以很容易实现,但SpinalHDL好处在于能够将功能封装抽象成库函数供我们快速调用而不是

2022-07-21 14:31:07

安装。软件安装所有软件安装在 X:\\SpinalHDL 目录下即可所有软件安装过程中,把 path 选项都勾选上;使用sbt国内镜像。 在个人用户目录下新建.sbt文件夹,在文件夹内创建

2022-10-17 15:33:34

在SpinalHDL的测试代码里也可以起多个,不过其为协程。SpinalHDL的仿真库已经帮我们封装好了底层协程的处理,两个协程之间的通信(类似systemVerilog中的mailbox)我们可以

2022-07-25 15:09:03

在Bits的基础上,SpinalHDL提供了UInt、SInt数据类型,从而能够进行有符号/无符号数操作。变量定义/初始化UInt/SInt的初始化与Bits类型相似:逻辑操作符UInt/SInt

2022-07-14 14:45:15

设计。以下是SpinalHDL检查的简要概括: 重复赋值 时钟域交叉 层次化违例 组合逻辑环路 Latch 未驱动的信号 位宽不匹配 得不到的switch生命 在每个SpinalHDL

2022-10-24 15:37:28

SpinalHDL中的switch在之前的文章中曾提到过SpinalHDL中switch的使用:通常情况下,switch对应着我们日常Verilog代码中的case。像下面的代码:其生成的RTL代码

2022-07-06 10:59:58

,data1两个UInt信号以及为该方法定义了一个sum求和函数,文中针对该总线进行功能描述。而就SpinalHDL中关于代码描述的一些建议,在之前的文章中也有提及:《SpinalHDL代码组织结构之

2022-06-28 15:21:19

声明时,master/slave是另一种选择,它需要我们在定义类时继承扩展Bundle及Imaster Slave:这里我们继承了ImasterSlave,则需要我们在class中实现asMaster

2022-07-21 14:20:23

,在SpinalHDL例例化一个带层次结构的RTL代码(RTL代码本身没什么意义,主要展示带层次结构的RTL代码在SpinalHDL中设计仿真的实现)。RTL代码分两个文件:SpinalHDL IP

2022-06-22 14:59:25

时会同时生成用于生成相应ILa IP的tcl脚本,从而能够轻松的在SpinalHDL中实现对待跟踪波形信号的抓取实现。下面一段代码展示了如何在SpinalHDL里添加ILA:在上述代码中。就像声明一个类对象

2022-06-22 14:37:13

switch方法用于实现Verilog里case语句的实现:看起来似乎和Verilog里的差不多,但SpinalHDL基于Scala语言,可借助高级语言进行方便的代码构建:在SpinalHDL里,我们

2022-06-22 14:25:27

下午微信群里有个小伙伴问了这么一道题:将一个为UInt(128 bits)的Stream接口连接到一个UInt(32 bits)的StreamFiFo上,在SpinalHDL里有没有什么好的方式实现

2022-07-27 14:52:09

快速连接器在液体冷却中的作用是什么?如何确保连接器稳定性?要注意哪些因素?

2021-04-13 06:34:53

快速连接器在液体冷却中有什么作用?

2021-06-07 06:47:48

快速Gabor滤波算法在虹膜识别系统中的应用是怎样的?Gabor滤波器的实现

2021-04-07 07:00:17

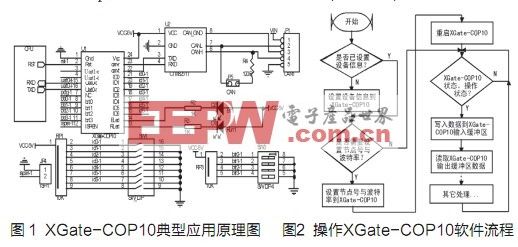

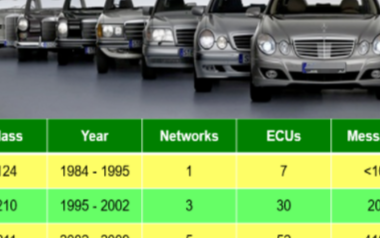

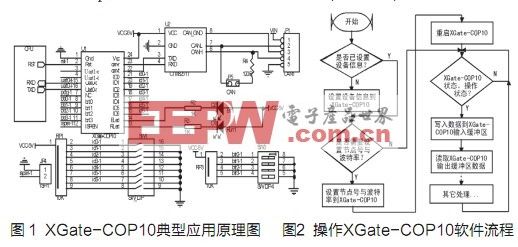

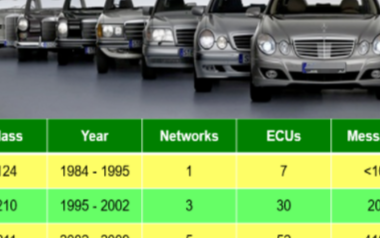

CAN总线快速入门

2012-08-07 16:07:56

CAN总线快速入门

2012-08-20 19:20:24

582M 蓝牙键盘项目,蓝牙处于连接状态下,我想快速断开当前连接,并改地址进入广播状态,但蓝牙总进入Connected Advertising..,要等好久才会Advertising..。。在不擦除绑定信息的情况,有什么办法可以快速进入Advertising..吗??

2022-08-01 07:34:25

在现代电子系统中,有为数众多的 IC 需要进行相互之间以及与外界的通信。为了简化电路的设计,Philips 公司开发了一种用于内部 IC 控制的简单的双向两线串行总线 I²C

2018-09-29 09:37:11

数据传输是通过ISA总线控制芯片组中的两个级联8237 DMAC来实现的。这种DMA机制也称为“标准DMA”(standard DMA)。标准DMA有时也称为“第三方DMA”(third-party

2019-07-01 08:10:07

LabvIEW中如何实现大容量数据的快速读取呢?我试过将数据存放在excel表中,然后用读取电子表格VI去读取,但是,分析下来,要花1s左右,有没有更快的方法呢?我想控制在200、300毫秒之内

2014-10-08 21:25:42

RS-485总线在工业设计中的应用485总线的工业设计应用指南 &

2009-09-04 08:35:45

方便的实现上述电路逻辑:在上面的代码中,14~18行例化了一个Mem并实现其写端口逻辑,20行通过Mem提供的streamReadSync函数实现对Mem的读操作(接收一个Stream总线作为读请求

2022-06-22 14:44:29

来源于《SpinalHDL—Area》一文,读者可参考该篇文章研究该实现方式。SimEnv对于仿真而言,最好的形式便是仿真驱动与测试case分层设计,在这里,通过采用类继承的形式定义一个addInstSim的类来实现一个

2022-07-28 15:12:32

1 CHI的片上互联总线片上互联是将SoC内部不同模块连接起来的结构,如前文提到过的硬件系统结构中, Interconnect Bus就是片上互联。需要支持模块之间的高速数据传输,高效地互联互通

2022-06-29 16:28:32

Spinal状态机在使用SpinalHDL的状态机时,生成的Verilog代码里状态机中状态的定义全都是由宏定义来实现的。在真实的工程里,我们很少会讲所有的Verilog代码放在一个文件里。往往是一

2022-07-08 16:13:01

在做RTL仿真验证时,覆盖率收集往往是我们在验证中需要注意的地方,本篇就SpinalHDL中的验证覆盖率收集做一个简单说明。sbt配置在SpinalHDL里进行仿真验证时,我们的待测试代码会生

2022-06-24 15:56:45

驱动 cocotb仿真的实现机制和SpinalHDL原理无差。在cocotb中,对于信号的赋值,也和SystemVerilog提供了两种类似的方式:sig.value

2022-06-24 16:34:49

SpinalHDL和Chisel都是基于scala来实现的,而在SpinalHDL的example里,偶然看到一个apply的有趣用法。“神奇”的逻辑,"奇葩"的写法偶然看到一

2022-07-19 15:08:36

至少为1μs(参见下图五)。 图五:主控MCU读时隙 结语:本文只是通过以MY18E20为例,介绍单总线传感器在实际应用中,硬件设计和通讯时序的相关问题。明白了其实现原理,其他的就可以触类旁通,供读者参考。

2020-07-08 17:22:05

USB(通用串行总线)是一种新的数据通信接口方式,它使得外围没备到计算机的连接更加高效、便利。USB接口不仅具有快速、即插即用、支持热插拔的特点,而且能同时连接多达127个外部设备,可以有效地

2021-01-11 06:56:37

系统中DCS总线接口设备的设计与实现。2 概述MCGS工控组态软件开发工具基于Windows操作平台,支持快速构造、生成工业设备驱动,具有良好的扩充能力。具体地说,MCGS用Active DLL构件

2018-12-18 10:11:22

)→Turn_ar→Idle,突发数据交易,读交易则插入读等待状态R_wait.若从设备提出终止,则插入L_data和Backoff状态与主设备断开连接;若是主设备提出终止则正常的结束总线交易。在设计中,配置

2019-05-29 05:00:02

1 所有软件安装在C:\\SpinalHDL根目录下即可2 所有软件安装过程中,把path选项都勾选上3 仿真需要使用GTKWave+Verilator,安装MSYS2软件之后,打开用户终端输入如下

2022-10-24 15:40:49

如何实现一条can总线上连接许多can设备?

2021-11-15 06:37:44

CANScope分析仪是什么?如何快速判断CAN总线的故障节点?

2021-05-20 06:44:41

前言在安装完成Verilator、GtkWave后,我们即可在IDEA里通过SpinalHDL提供的仿真接口来对我们的设计进行仿真。在《SpinalHDL—仿真环境》一文中已提到SpinalHDL下

2022-07-26 16:59:25

currentState如果你去看过SpinalHDL中StateMachine,那么你会发现其实现里通过stateReg来标记当前状态,而这里通过addPrePopTask中将其赋值到

2022-06-30 15:19:03

打开过Bundle的代码实现,你就会发现这里面有一个assignAllByName的方法实现很符合我们的需求:我们在Bundle中声明的信号接口都存储于elements中,elements的定义形式为

2022-10-11 15:14:37

代码描述了,SpinalHDL提供对仿真的支持,而基于Scala这门语言,在构建仿真环境时拥有者更丝滑的体验。这里完整的仿真环境搭建代码如如下所示:仿真执行搭建完环境后,仿真的执行就很简单了:让仿真飞一会儿:仿真波形可以通过gtkwave来观看:原作者:玉骐

2022-07-20 14:38:07

主站在总线一端点 图所示的是一般的Profibus总线连接方法,主站位于总线的一端,终端电阻打ON。 然后依次连接后面的站点,中间的站点终端电阻打OFF,最后面的站点终端电阻打

2020-12-02 11:51:20

在航空电子综合化系统中,快速、有效的数据传输对整个航空电子系统的性能有很大影响,因此数据总线被称为现代航空电子系统的“骨架”。ARINC429是航空电子系统之间最常用的通信总线之一。要在计算机上实现与机载设备的ARINC429总线数据通信,必须实现429总线与计算机总线之间的数据传输。

2019-08-19 07:24:53

呢?在SpinalHDL中,对于总线连接时位宽的检查是十分严格的,这里直接使用"<>"或者“>>”方法来进行连接显然是不行

2022-12-12 16:31:03

最新总线技术在仪器控制与连接方面的远景简介过去二十多年间﹐科学家与工程师已在自动化仪器系统中广泛使用IEEE 488 和通用接口总线GPIB。当大众化电脑技术进入测试与测量领域﹐并在连接仪器

2009-10-23 18:35:10

1、基于SpinalHDL的多端口仲裁的设计》最低优先级调度 SpinalHDL中关于roundRobin的实现背后原理其实一开始困惑挺久,后来方慢慢理解。在讲解roundRobin之前,先来

2022-06-10 17:12:07

米)。 (5)传输媒介和连接方式 完整的现场总线系统,除了构成网络的范围(即最大距离)是一个重要的指标外,能否在总线系统中实现不同总线段间采用不同的传输媒介,也是重要的因素。它使系统的构成

2012-02-01 13:48:53

现场总线在自动化系统中的应用 传统方式现场级设备与控制器之间连接采用一对一所谓I/O接线方式传递4-20mA或24VDC信号 现场总线技术主要特征是采用数字式通信方式取代设备级的4-20mA(模拟量/24VDC 开关量信号使用一根电缆连接所有现场设备

2009-11-17 09:31:02

无论是Amba总线还是其他类总线,握手与分发总是无处不在。在SpinalHDL中,Stream的抽象提取个人认为绝对是一个精彩的操作。SpinalHDL的lib中针对Stream也提供了大量的组件

2022-07-07 17:18:27

; this}对于每个待连接的slave端口,这里转换成列表存放于translatedSlaves中。之所以将slave端口转换成列表的形式,在于当我们传入的slave端口是axi4时,在

2022-08-09 14:40:34

信号的不同bit赋值给不同的信号,这种拼接方式可以在SpinalHDL中按照如下的形式进行书写:case class demo() extends Component{val

2022-11-18 15:21:04

不做过多的讲解(小伙伴可以自行下载AMBA总线协议规范或者翻看网络上AXI4总线协议相关文章)。在SpinalHDL中,关于Axi4总线,包含了配置和实现两块内容,其内容均在

2022-08-02 14:28:46

UVM里面有前门访问,后门访问的概念。前门访问无非通过总线来实现寄存器/Mem的访问。而当在一些仿真中为了减少通过总线进行配置下发所需的时间,那么后门访问就非常便捷了,它使得无需通过总线即可修改

2022-07-04 15:19:10

BlackBox在之前的文章中,曾介绍过如何封装兼容别人的RTL代码:SpinalHDL——集成你的RTL代码整体的思路还是简洁明了的,相信读完后照着做很快就能上手。这对于保持设计的兼容性及混合

2022-06-29 16:02:13

的具备阻塞实现便捷性。正式基于上面的这些思路(这种设计思想也是深得我心),SpinalHDL中的StreamFifo便由此而来:无论是出口(pop)还是入口(push),均抽象为Stream接口,push

2022-06-30 15:28:00

各位大佬好

我想问下,平时我们使用的蓝牙遥控器是如何实现打开电视,就能快速连上的,普通的蓝牙配对连上至少需要五六秒钟的,这个只需要点一下就能唤醒马上能使用了,请问这种一般是如何实现的。

2023-09-19 09:15:51

》踩到的坑在很早之前,曾写过如何在SpinalHDL中例化之前用Verilog/SystemVerilog所写的代码,可参照文章《[SpinalHDL——集成你的RTL代码]》一文。在

2022-08-31 14:58:31

)及兼顾代码尽可能复用的准则,SpinalHDL里设计了Area的概念。通过类扩展集成Area,可以有效的避免上述问题。介绍Area之前,先介绍一个概念:在Scala中,参数的传递均为引用类型,而我们定义

2022-07-22 14:22:23

到ack为低电平即可处理新的任务。 写在最后 关于跨时钟域处理在处理上相对来讲还是一个易错点,其处理也是新学者需要好好把握的。SpinalHDL中的源代码还是很值得一读的。一方面

2022-06-30 15:11:08

介绍采用Altera 公司的可编程器件实现串口通信的星型连接,扼要地介绍四路UART 串口通信网络的星型连接的硬件和软件的实现。在实现多点串口通信时,星型连接比总线型连接具有

2009-05-15 15:24:57 38

38 在VXI总线系统中,为了能够获得大量实时数据,需要利用CAN总线快速可靠的传输数据的性能,设计一种混合VXI总线和CAN总线的系统。在这种混合系统中要实现CAN总线上各个节点采集

2009-07-06 16:27:58 13

13 基于CANopen协议从站设备快速实现方法

CANopen协议作为CAN总线的应用层协议,拥有复杂的网络管理、实时过程数据对象、服务数据对象、预定义连接和特殊功能对象等基

2010-05-23 12:03:20 1440

1440

Xilinx FPGA工程例子源码:实现基于spartan3与CAN总线连接后的的汽车时速的模拟仿真

2016-06-07 15:07:45 9

9 CAN总线快速入门

2016-12-13 17:15:19 22

22 进行信息传送的公共通道,常用外部总线有RS-232C、RS485和IEEE-488、USB、CAN 等现场总线、快速以太网、WIFI总线等。

2017-10-20 17:47:42 2

2 “快速连接器”是一个广泛的工业产品配件名词,分为液压管道快速连接器和挖掘机快速连接器。这里是指挖掘机快速连接器(也叫快换接头、快速连接头),快速连接器能在挖掘机上迅速安装各种配置件(挖斗、松土器、破碎锤、液压剪等),能扩大挖掘机使用范围,能明显的节约时间,提高工效。

2018-06-03 18:48:00 1140

1140 广成科技GCAN-204型号Modbus RTU转CAN模块可以实现将Modbus主站与CAN总线连接。

2018-10-25 11:29:57 7495

7495 聊一聊在SpinalHDL里时钟域中时钟的定制与命名。 相较于Verilog,在SpinalHDL里,其对时钟域有着更细致的描述,从而也能够更精细的控制和描述。而对于时钟域,我们往往关系的是: 时钟

2021-03-22 10:14:37 1854

1854 在SpinalHDL里,其Libraries里提供了关于总线相关的库。包含AMBA3、AMBA4、AVALON等总线类型,并提供了bus slave factory工具

2021-04-08 17:28:26 2839

2839

最近偶尔需要用到SPI模块。正巧看到SpinalHDL中所提供的SPI-Master设计。看完之后尤为佩服如此简洁而又全面的设计方式。本篇不对SPI协议进行讲解,仅针对SpinalHDL中的SpiMasterCtrl模块做使用说明。

2021-04-19 09:58:14 3283

3283 所有控制仪表的相关 CAN 总线,例如:舒适系统数据总线,都围绕在中心点。 插头连接 CAN 总线中心点。

2021-04-20 09:36:53 22

22 不点蓝字,何来故事? 学习SpinalHDL已有近半年,其诚然小众,但“小家碧玉”未尝不是绝代佳人。出坑Verilog遥想当年本科之时画过电路PCB、玩儿过单片机、PLC,亦学...

2021-12-20 18:56:13 3

3 CAN总线的应用越来越广泛,工程师在不同工况下,如何快速实现故障定位呢?本文将介绍CAN网络故障带来的麻烦,以及快速定位故障的几种方法,可以帮您快速完成判断并进行选择。

2022-03-10 09:09:47 3517

3517

针对SpinalHDL中的两大类型Reg、Wire,来梳理下在SpinalHDL中的对应关系及声明形式。

2022-07-03 11:02:05 1096

1096 每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

2022-07-11 10:51:44 1309

1309 通过bus slave factory,我们可以方便地实现寄存器读写,其提供了一系列寄存器读写方法。这里列举几个常用的方法(完整的方法列表可参照SpinalHDL-Doc):

2022-08-05 09:57:46 776

776 本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。自此仿真设计一体化不是问题。

2022-08-10 09:15:17 2038

2038 书接上文,趁着今天休假,采用SpinalHDL做一个小的demo,看看在SpinalHDL里如何优雅的实现Sobel边缘检测。

2022-08-26 08:59:48 963

963 UVM里面有前门访问,后门访问的概念。前门访问无非通过总线来实现寄存器/Mem的访问。而当在一些仿真中为了减少通过总线进行配置下发所需的时间,那么后门访问就非常便捷了,它使得无需通过总线即可修改寄存器/Mem的值。今天,就来看看在SpinalHDL的仿真中我们可以使用的后门读写操作。

2022-09-02 09:29:22 772

772 SpinalHDL中Bundle与SystemVerilog中的packed struct很像,在某些场景下,与普通数据类型之间的连接赋值可以通过asBits,assignFromBits来实现。

2022-10-17 09:51:40 947

947 作为SpinalHDL语法篇的第一节,我们也从最简单的开始。

2022-10-31 10:56:08 903

903 在之前写Verilog时,位拼接符是一个很常见的东西,今天来看下在SpinalHDL中常见的位拼接符的使用。

2022-11-12 11:34:23 838

838 最近做系统总线的定义,模块之间存在着大量的握手交互,在SpinalHDL中这类总线往往继承于SpinalHDL中的Stream。以下面的总线定义为例。

2022-12-07 21:03:02 291

291 在SpinalHDL中使用之前已有的Verilog等代码的时候需要将这些代码包在一个BlackBox里面,但是如果这些代码里面有时钟和复位,我们需要怎么将时钟和复位端口和SpinalHDL中已有的时钟域连接起来呢?

2023-05-04 11:13:14 489

489

作为SpinalHDL语法篇的第一节,我们也从最简单的开始。

Bool类型定义

2023-05-05 16:01:32 362

362 实现一个在ARM中通过APB总线连接的UART模块(Universal Asynchronous Receiver/Transmitter),包括设计与验证两部分。

2023-06-05 11:48:38 953

953

昨晚看SpinalHDL的Issues,其中有一个关于性能提升的case 吸引到了我,尝试实验到深夜,测试下在SpinalHDL以及cocotb下的性能优化手段。

2023-08-06 17:10:34 370

370

快速实现EG网关串口连接丰炜PLC

2023-11-27 17:28:05 228

228

中扮演着重要的角色。下面将详细介绍光纤快速连接器的作用、安装使用以及与冷接子的区别。 一、光纤快速连接器的作用 光纤快速连接器主要用于连接光纤的两端,实现光信号的传输。连接器的作用是提供机械接合,确保光信号能够稳定

2023-12-27 15:44:46 622

622 CAN总线星型连接器及特点 CAN总线星型连接器是一种用于连接CAN总线网络的设备,它具有一些独特的特点和优势。本文将详细介绍CAN总线星型连接器的工作原理、结构特点、适用范围以及与其他类型连接

2024-01-04 16:59:25 806

806 之前有系列文章介绍了SpinalHDL中Pipeline的使用,最近在一个功能模块中真实的使用了这个lib。

2024-03-17 17:31:36 474

474

电子发烧友App

电子发烧友App

评论