当今时代,随着云计算、AI、高性能计算等技术的发展,海量的数据从互联网的不同节点被汇集、处理、再分发,对存储、DPU、GPU、服务器等芯片在数据容量、速率、部署灵活性等方面提出了新的要求。结合Cloud AI、云计算向边缘网络的扩展趋势,又延伸出更加丰富的应用场景,使得数据可以更快更好地为人们提供服务和各种决策的辅助。

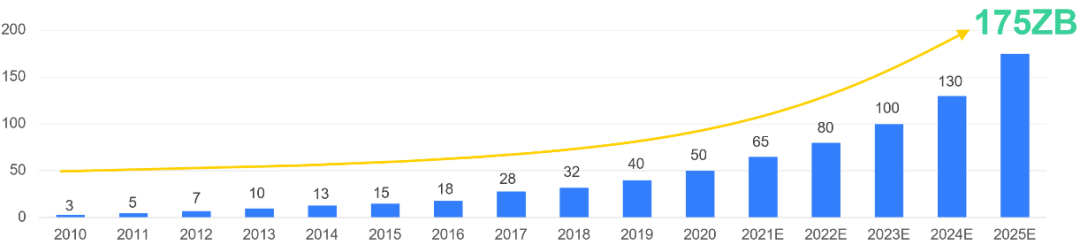

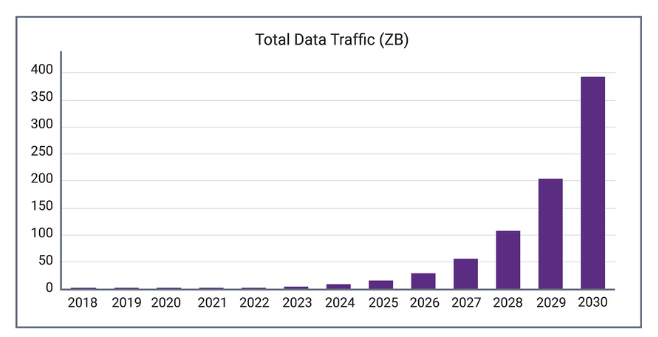

这些创新领域都需要处理大量的数据及计算。据IDC统计,2025年全球数据量将达到175ZB,对算力的要求每年增加10倍。换句话说,高算力的发展,成为支撑数字化世界的重要推手之一,是推动未来经济发展的重要指标与技术。

全球数据量年度规模及预测

(单位:ZB;来源: IDC)

高速增长的数据量,推动了更多加速器和计算架构的布局。在此背景下,通过数据接口技术的不断演进来满足上述应用对新性能和容量的需求,正在成为核心的关键技术。

因此,高速接口技术开始得到广泛使用,比如DDR、LPDDR、PCIe、CXL等,接口上的性能在不断地提升,标准的演进和更新周期也在不断地缩短。

“

数据安全是重中之重

与之伴随而来的,是数据安全保护的重要性被提到了一个新的高度。因为随着新应用的出现,很多数据包含隐私、敏感信息,同时由于不同人的数据可能会存储在同一个资源池当中,这就给数据窃取、篡改,甚至是伪造带来了比较高的风险。

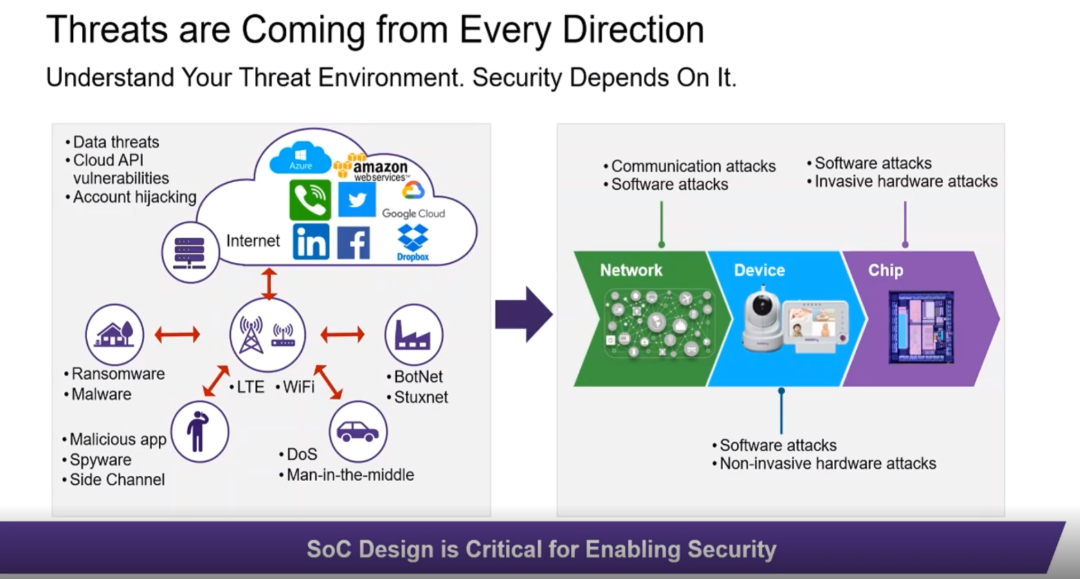

数据安全威胁来自四面八方。尤其随着当前密码分析技术、仪器自动化和量子计算等技术的发展,相比过去的攻击手段,攻击门槛已大大降低。

对此,通过政策法规和安全技术标准的演进,能够对数据安全问题加以限制和约束。以技术标准为例来看,PCIe和CXL组织在2020年底发布的最新标准当中首次加入了信息安全的功能——PCIe 5.0和CXL 2.0当中的IDE(Integrity and Data Encryption)数据完整性和加密保护。此外,下一代的PCIe 6.0、CXL 3.0当中的安全需求也得到进一步的强化。

这些都证明了数据安全接口的需求和重要性。除了最直观的性能、功耗、成本等指标外,数据安全作为一个重要的评判标准已经愈发成为了行业的技术共识。

高速接口成为实现数据安全的关键

从芯片开发者的角度来说,为了有效地保护芯片内的核心资产和数据安全,SoC设计是实现安全的关键。面对上述可能出现的数据安全威胁,芯片开发者需要关注攻击技术的演进,尽早在芯片设计中提前做出应对。

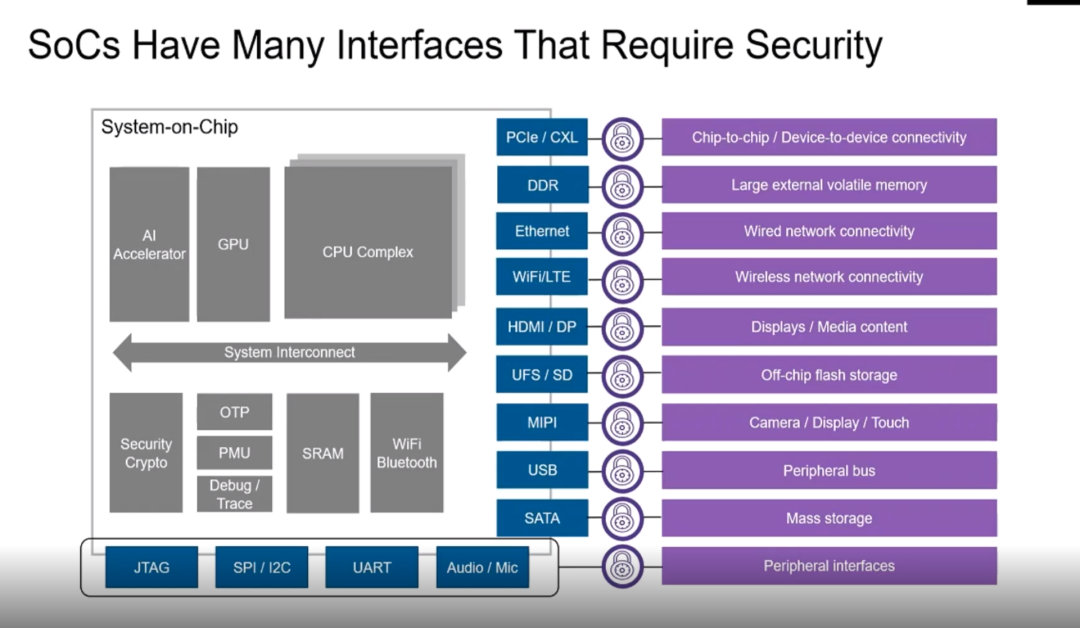

具体到芯片架构层面,各种接口作为芯片和外部世界的交互媒介,长期以来都是攻击者所关注的重要对象。行业最新的发展方向就是将安全功能融入到数据接口来实现传输和保护的高效结合。

如下图所示,芯片上有许多需要安全性的接口。

PCIe/CXL接口广泛用于实现芯片系统之间的高速互联,更是为Chiplet互连(UCIe)提供了坚实的技术基础;

DDR作为常用的存储媒介接口,安全需求非常清晰,一个典型的应用场景就是,当敏感信息写入DDR时会被加密存储,在读取载入芯片的时候才被解密恢复;

Ethernet、WiFi、LTE等有线、无线的网络接口,其技术标准本身已经是在不同的传输层去定义了安全协议来确保数据包的机密性、完整性和真实性;

HDMI/DP作为广泛使用的多媒体接口,它的安全需求主要来自于影音内容的版权保护,通过利用行业中比较成熟的HDCP 标准就可以很有效地保障版权影音在合法合规的设备中完成端到端传输,这也是全球影视创作传播得以持续健康发展的核心技术保障;

一些其他的接口,比如MIPI、USB等,基本上也已经有了标准化的数据安全保护技术,或是正在一些内部小组的主导之下,参考其他接口的案例来积极地草拟相关的安全协议。

整体而言,未来芯片数据接口的发展方向就是形成一个标准化、专门化的安全防护,来保证不同厂商的设备通过同类型接口在互通的基础之上强化各个数据链路上的信息安全。

那么怎样才能算是一个有效、完整的安全保护方案呢?

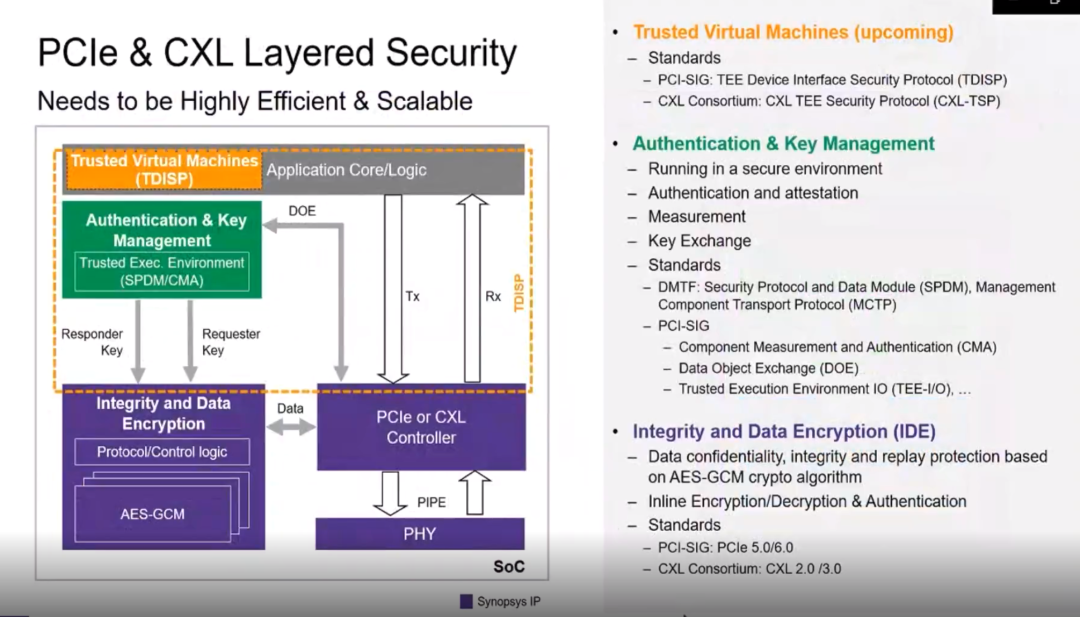

从本质上来说,一个优秀的安全保护方案需要具备两个核心要素:第一是认证鉴权以及密钥管理;第二是从端到端的数据完整性和机密性的保护。

认证鉴权以及密钥管理:认证鉴权和密钥管理模块的主要功能是在通讯节点之间实现身份认证以及安全能力的识别,确保通讯双方是可信任的,并且能够协商产生相应的密钥来支持后续的加解密操作。

数据完整性和机密性保护:在认证鉴权完成、确定这个设备的合法身份之后,负责对实际传输的数据进行加密保护,以防止数据被窃取或篡改。

除了这两个核心要素之外,在系统层面还有一个潜在需求,即上述功能要在一个受信任的安全边界内部来实现,即需要一个可信执行环境。从控制层面,比如安全启动、密钥管理等任务也要确保上述的鉴权和传输操作按照设计初衷来正确、安全地执行。

另外,一个优秀的安全防护方案还需要考虑到整体的性能、功耗、面积、成本(PPA)方面的影响和优化。比如在保护数据通路的同时,如何尽可能降低对通讯延迟的影响?在建立身份信任的时候,如何尽可能减少额外的通讯开销?在进行安全密钥管理的时候,如何尽可能降低面积的增加?……这些都给芯片开发者提出了新的挑战。

高速接口IP如何为数据安全赋能?

基于上述内容,以PCIe/CXL标准所定义的最新的安全规范为例,充分反映了安全设计理念在高速接口上的实现。

在接口IP设计中,首先需要一个运行在可信执行环境之下的设备认证和密钥管理模块,以及一个数据完整性和机密性的保护模块,来对链路上传输的大量数据进行保护。目的是为了增强系统的安全鲁棒性,防止数据的窃取、篡改、重放、恶意注入、删除等。

具体来看,上面框图从上到下分层描述了从应用层到硬件层几个主要的组成部分,来管理虚拟机和虚拟外设之间的信任关系,以及在PCIe、CXL上实现设备的认证和密钥协商,不仅要确认硬件设备的身份,同时还要验证软件、固件的真实性。

在建立设备之间的这种信任之后,在IDE标准的指导之下,在硬件层面上就要对链路上传输的数据进行在线的加解密处理。

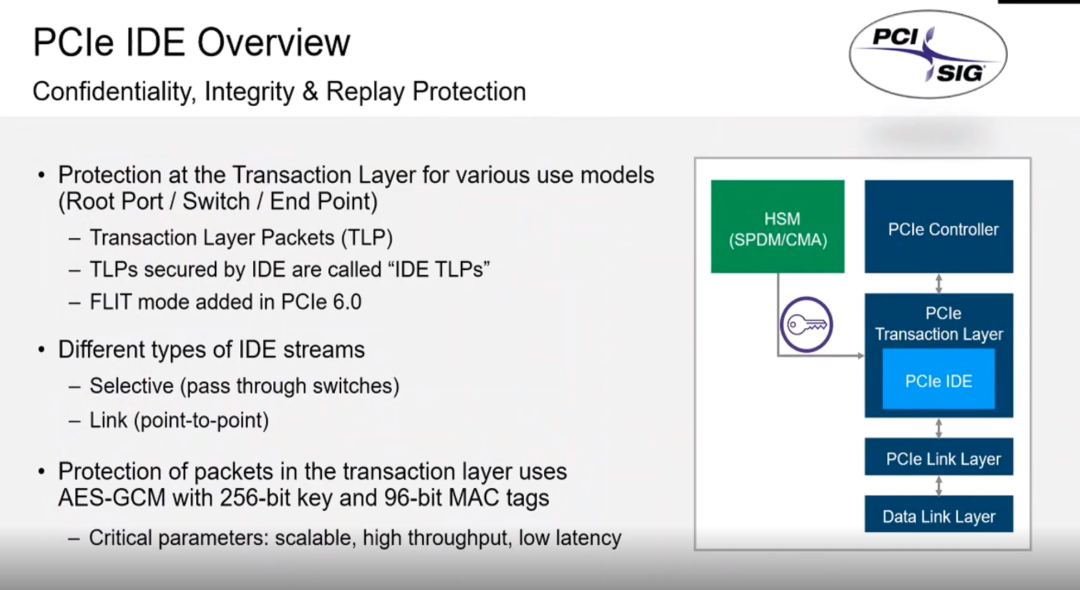

上文有提到,IDE是在2020年底PCIe 5.0发布的ECN当中所定义的,其功能是在传输层实现数据的完整性、机密性以及重放保护,可以支持包括Root Port/Switch/End Point等在内的不同应用场景。

IDE所处理的数据单元是PCIe传输的TLP包,而且在PCIe 6.0当中,将会看到以FLIT为单元的FLIT模式。

IDE所处理的数据可以分为Selective stream和Link stream两种不同的数据流。Selective IDE stream可以有选择性的对传输的TLP数据进行保护,并且可以穿越中间的Switch设备;而Link IDE stream会对所有TLP的数据进行加密保护,保护的是直连链路上的数据。

另外,IDE标准要求采用广泛部署的AES-GCM算法,256 bit的密钥长度,添加96 bit的完整性标识。IDE统一的功能定义和加密算法对于建立行业规范来确保不同厂商的设备之间互通互联非常重要。

“

新思科技IP为芯片数据安全保驾护航

作为半导体IP行业的领先企业,新思科技全面赋能芯片设计,拥有全线高速接口IP产品以支持高性能计算需要的高带宽、大吞吐量、低延迟及数据安全的需求。

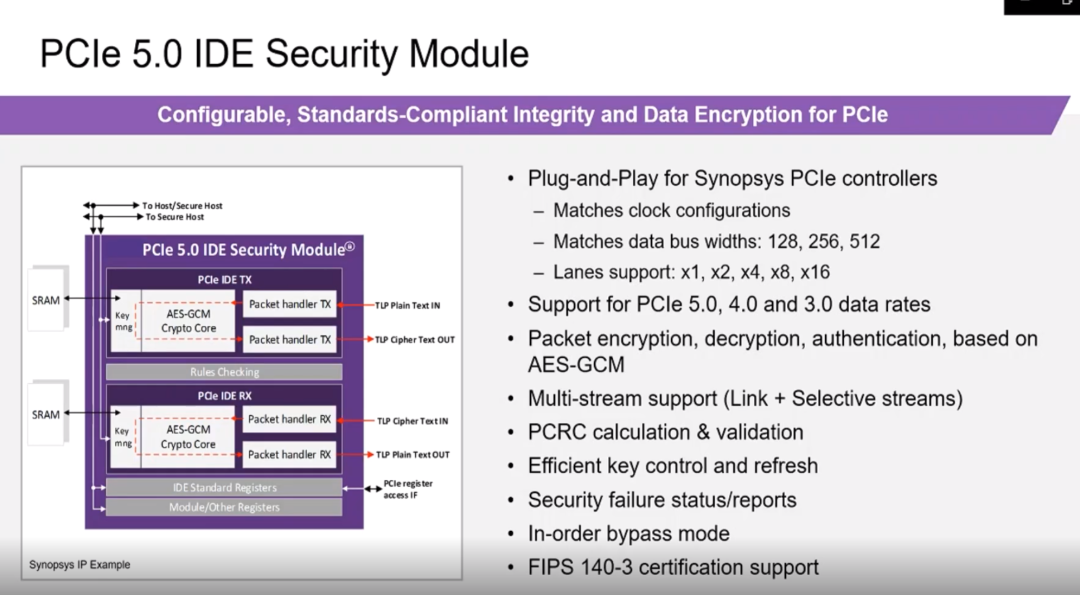

以新思科技针对PCIe设计的IDE IP产品为例,该IP支持TX和RX两个方向的数据保护,内部的AES- GCM引擎可以通过优化来匹配PCIe controller的传输速率。同时,它也是高度可配置的,以满足PCIe接口在不同芯片中的配置需求。

据新思科技技术专家介绍,IDE IP有专门的密钥接口用于和安全环境对接,从而支持比较高效的密钥切换,在实际使用场景中,根据数据类型的不同可以支持不同的密钥来进行相应的保护。

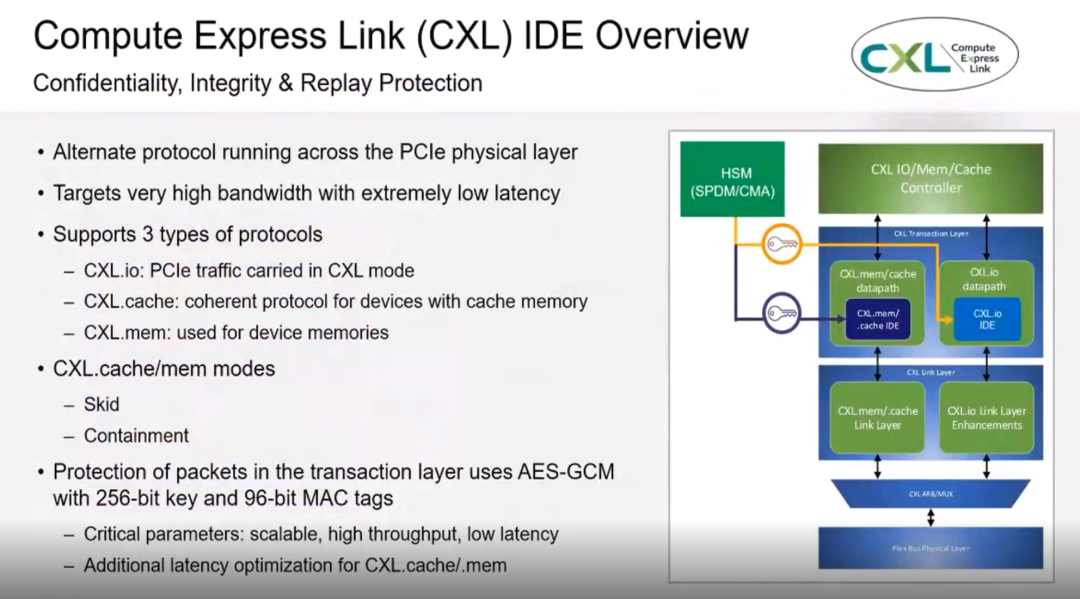

与PCIe类似,CXL协议也是于2020年年底在2.0版本当中同期发布了IDE的ECN。CXL以PCIe的物理层为基础,可以在host和device之间提供高吞吐率、低延迟以及缓存一致性等特性。

CXL标准自推出以来,越来越多地部署在高速存储、云计算的应用场景当中,比如数据中心的存储资源池、智能IO扩展卡,异构计算架构下的加速器等。类似于PCIe的IDE,CXL的IDE也是使用标准的256 bit AES-GCM,添加96 bit的完整性校验。

针对CXL,新思科技同样设计了IDE的IP产品。从示意图来看,CXL的功能模块基本上和PCIe的IDE一致。而对于CXL cache、mem,IDE针对CXL FLIT数据包的传输特点加入了新的模块来优化它的延迟。

CXL IDE同样支持TX和RX两个方向的数据保护,内部的AES-GCM的引擎经过优化之后可以匹配CXL controller的传输速出率。同时IDE IP也是高度可配置的,可以去满足CXL在不同芯片当中的配置需求。同时,IO、mem、cache对应的IDE也可以支持其任意组合,从而满足不同设备类型和业务场景。

除了PCIe、CXL IDE之外,接口安全作为一个被普遍采纳的设计集成趋势,在其他的基础协议上也有所体现。

比如针对包括DDR/LPDDR在内的各种存储接口,在行业中定义了AES-XTS算法模式来对其中的静态数据进行保护,为了降低相关加解密操作的延迟开销,可以把密码算法模块集成到存储控制器的数据通路内部,从而实现所谓的“内嵌”,或者说在线的数据保护,也就是IME (Inline Memory Encryption)的功能。

对于芯片开发者来说,新思科技既可以提供内置IME功能的DDR/LPDDR控制器,也可以提供单独的IME IP来支持用户自行集成到不同的存储接口上面,来保证敏感信息不会以明文的方式离开芯片。

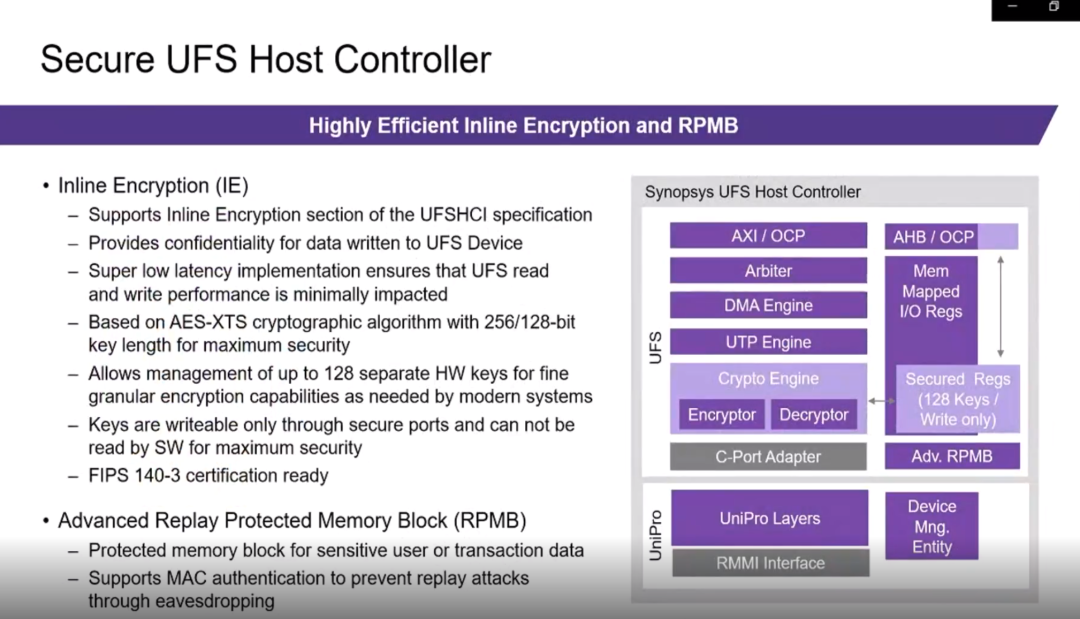

针对UFS,新思科技可以提供内嵌硬件加密功能的UFS控制器,支持标准的AES-XTS算法值和内嵌结构,来降低安全防护对原有数据传输的性能影响。

此外,UFS控制器还专门支持RPMB功能,可以有效地对内部存储的核心数据进行访问权限管理,并且利用校验技术来防止数据被窃取之后的重放攻击。

除了建立芯片接口安全的两个核心要素:设备认证、密钥管理以及数据完整性和机密性保护之外,可信执行环境的建立也是一个潜在的基础要求。

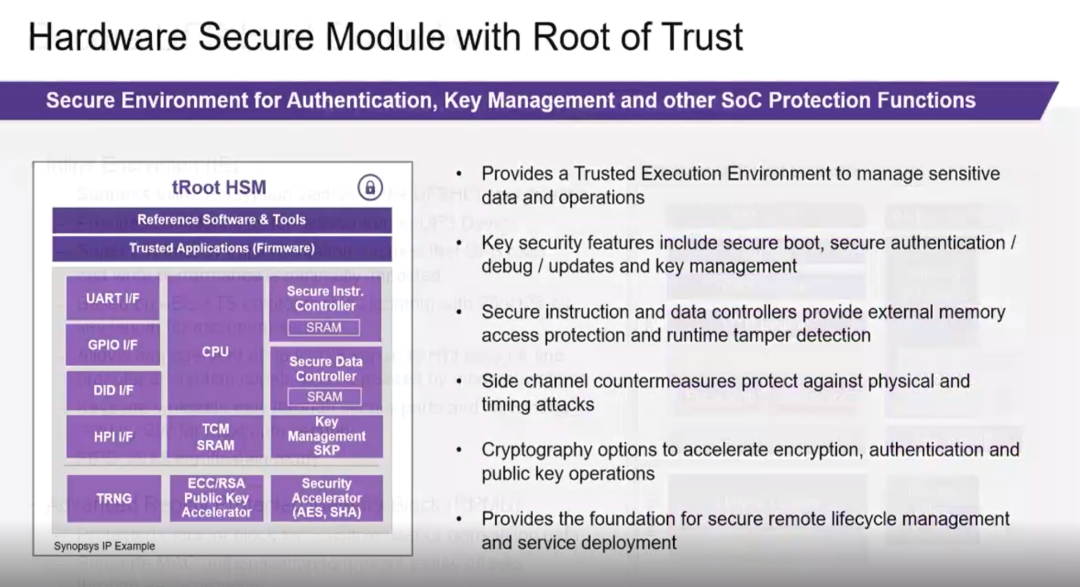

从芯片或者是系统安全的设计角度来讲,希望保护从静态存储到上电启动,再到运行阶段的数据和服务的访问等不同阶段的数据安全。针对这一功能,新思科技为开发者提供了tRoot HSM硬件安全模块。如上图所示,作为一个可编程的安全子系统,该模块内嵌了密码算法的硬件加速器和可扩展的外设接口,非常适合作为芯片当中的安全中枢,为其他的接口安全功能提供必要的可信执行环境的支持。

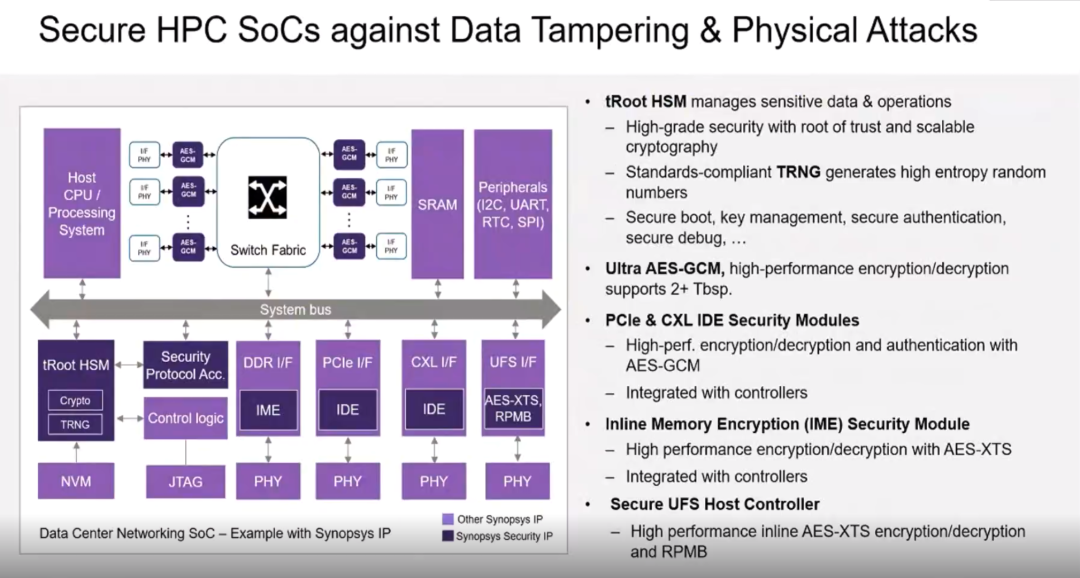

综合来看,新思科技的各种接口与安全相融合的设计理念正在被越来越多的芯片厂商和开发者所认可和采纳。从下图所示的SoC架构来看,其中浅紫色的部分是新思科技可以提供的各种IP解决方案,深紫色的部分则是他们在信息安全方面的解决方案。

其中,tRoot HSM扮演一个security manager的角色,作为一个硬件隔离的可执行单元,可以部署到SoC当中来掌控从安全启动、密钥管理到鉴权认证等不同阶段的任务,并且为其他分立的接口安全模块提供管理。

此外,除了上述提到的接口安全IP,针对尚未形成统一安全标准的其他接口,新思科技还可以提供一些独立的高性能密码算法和协议加速器来把密码算法和接口传输解耦合,来灵活的支持不同接口的传输技术和业务场景。

结语

随着技术的进步,高性能计算逐渐被应用在更广泛的领域,例如AI、机器学习、大数据分析、云端计算及网络通信等。高算力的发展及高性能计算的突破,成为支撑数字化世界的重要推手。

在这个过程中,大数据量、高吞吐率、低延迟的特性使得各种高速接口技术在芯片设计当中被广泛地部署。其中,数据作为核心要素,其安全性越发受到整个行业的普遍重视,已成为一个类似于性能、面积、功耗等传统指标的重要评估要素。

因此,为了进一步保护高性能接口的数据安全,需要在鉴权、数据完整性、机密性以及可信执行环境方面去寻求相应的解决方案,同时满足高性能计算在吞吐率和延迟方面的一些要求。

作为行业领先的方案供应商,新思科技致力于通过自主研发先进工艺芯片IP产品,响应高性能计算时代接口安全的发展新趋势,全面赋能芯片设计,通过提供包括PCIe、CXL、DDR、UFS等丰富的集成数据安全保护模块的接口IP,更好的帮助开发者应对接口安全和系统安全方面的需求和挑战。

编辑:黄飞

电子发烧友App

电子发烧友App

评论