2022 年 4 月 14 日,中国北京讯 - 全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布,率先推出符合PCIe Gen6严格标准的时钟缓冲器和多路复用器。作为业内先进的时钟

2022-04-14 15:33:49 1941

1941

Silicon Laboratories (芯科实验室有限公司, NASDAQ: SLAB)今日宣布推出业界首款通用时钟缓冲器(clock buffer),可以用单颗IC替代多颗LVPECL、LVDS、CML、HCSL和LVCMOS缓冲器,而无需多个不同格式缓冲器

2012-11-06 09:08:20 2237

2237 20路输出PCIe时钟缓冲器是下一代服务器、数据中心、存储设备及其他PCIe应用的理想选择。

2019-07-01 16:36:40 1028

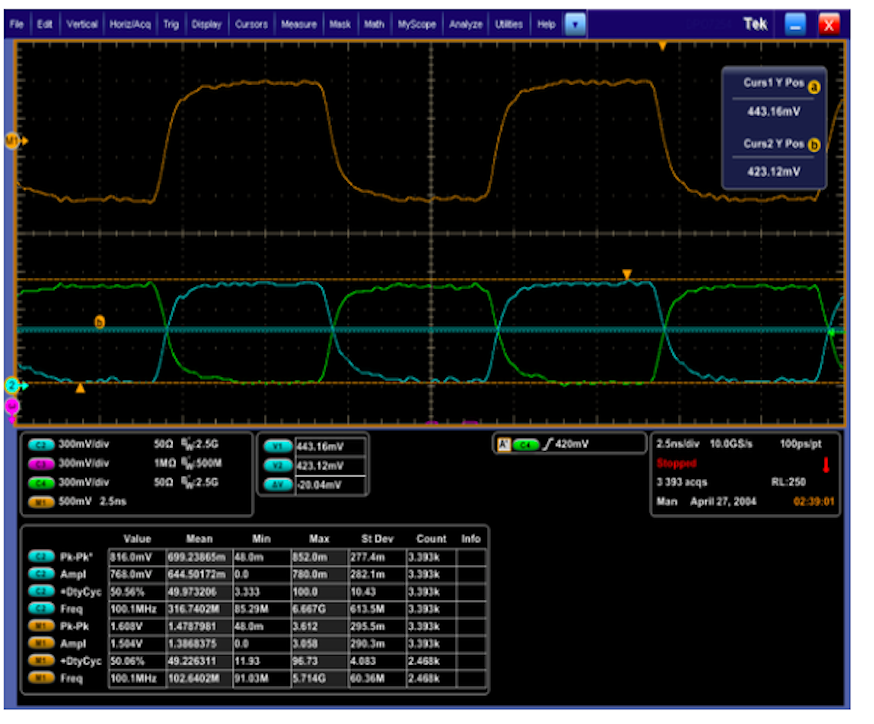

1028 毕设题目 :75mhz双路时钟缓冲器,求助

2021-02-27 21:45:00

差分信号传输的优势就是通过成对的差分线传输一个信号,只要它们一直亲密无间、步调一致,在接收端就能够消除掉沿途中遇到的任何干扰,原理参见下面的图示。差分时钟传输降低噪声在PCB板上走线避不开的就是因

2019-05-15 05:26:22

NB7V33MMNGEVB,差分时钟分频器评估板。 NB7V33M是一个4分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-21 09:44:22

大家好,在我的项目中,我有差分时钟输入。当我实现我的设计时,我打开了实现的文件。我已经习惯了I / O端口planninn菜单栏和从那里分配的引脚号和类型。另一方面,时钟输入仅显示为一个输入

2020-08-05 09:56:08

我用xilinxA735T,pcs的差分时钟管脚输入一个差分时钟,使用IBUFDS_GTE2得到一个单端时钟,把这个单端时钟引到外部管脚,用示波器没有看到。各位大神帮忙指点一下

2016-06-02 09:53:17

的。在I / O规划布局中,我可以看到该工具将这些信号视为单端信号。这是我在XPS中开发的自定义IP。有几个差分时钟信号和一些差分数据信号进入。我怀疑它希望输入缓冲区位于IP的顶层。这些输入缓冲区在

2018-11-02 11:38:13

ADCLK846 / PCBZ,ADCLK846评估板是一款高性能时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能差分地保持接近100欧姆

2019-02-21 09:54:43

AKD8181D,AK8181时钟扇出缓冲器评估板。因此,很容易评估DC / AC特性并确认产品功能

2020-08-25 15:26:54

(30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2022-02-23 06:32:02

NB7V32MMNGEVB,差分时钟分频器评估板。 NB7V32M是一个差分2分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-20 09:41:47

如果输入时钟时差分时钟信号,如何编写testbench?

2014-09-15 19:37:38

SI53159-EVB,用于PoE无线接入点的100至210MHz时钟发生器评估板。 Si53159是一款九端口PCIe时钟缓冲器,符合PCIe Gen1,Gen2和Gen3标准

2020-08-27 12:20:38

`请问什么是音频缓冲器?`

2019-08-23 16:27:28

100fs-300fs之间?

疑问3:是不是使用PLL类型的时钟发生器芯片带来的抖动误差会比较大?针对14位的ADC输入差分时钟有此类型的参考吗?

模拟输入部分:

疑问1:参考文档中使用AD8138差分驱动芯片

2023-12-22 08:19:31

具备SSTL_18输入与输出的25 位可配置寄存缓冲器的特性及应用25 位 1:1 或14 位 1:2 可配置寄存缓冲器适用于 1.7 V 至 1.9 V 的 VCC 工作环境。就 1:1 引脚配置

2009-10-28 14:41:58

嗨,我有一个来自2.5V LVDS时钟缓冲器的时钟(http://www.onsemi.com/pub_link/Collateral/MC100EP210S-D.PDF),我想在FPGA中使

2020-07-24 15:16:28

高端时钟缓冲器用户不再需要面对抖动与电流的折衷

2021-04-06 06:24:31

中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304 扇出缓冲器就是一个很好的例子

2022-11-21 07:25:28

大家好 我在设计中使用virtex -4 FPGA做了一个项目。从外部到我的FPGA只有单端时钟。但是,连接到FPGA的AD需要几个差分时钟。如何实现这个功能? 据我所知,DCM原语确实提供了两种

2019-01-21 08:52:16

你好我正在使用ML605板,差分时钟输入产生一个全局使用的时钟。但是当试图约束时钟时,我不知道如何设置它。有什么建议么?谢谢

2019-10-28 07:21:01

沿使其与ZDB输出同步的多PCIe参考时钟产生器)。 例如,NB3N1200K/NB3W1200L零延迟缓冲器(ZDB)带12路HCSL/NMOS推挽输出,特性包括:支持DIF SRC时钟;12个差

2018-10-09 11:38:19

嗨,我是第一次在Fpga工作。我为所有32个收发器提供125 MHz差分时钟。现在我需要为I / O bank提供125 MHz差分时钟。有没有办法使用GTX时钟用于这个目的(正如我读到的,MRCC

2020-07-15 09:48:46

我从赛灵思购买了ML405板。我需要在Virtex4中使用MGT做一些事情。从IP核生成器生成的文件中,看起来参考时钟由GT11CLK从一对差分时钟输入生成。但是我找不到ML405上的差分时钟源,我

2019-08-15 06:04:11

的不确定性,导致抖动增加。在实际系统中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304

2018-09-13 10:11:44

RS2CG5705B是一款符合PCI Express 3.0和以太网要求的扩频时钟发生器。该电路用于PC或嵌入式系统,以显著减少电磁干扰(EMI)。RS2CG5705B提供4对差分(HCSL)或

2024-01-24 17:31:16

有没有哪位大佬知道国产的高速差分时钟缓冲芯片型号以及单端时钟转差分时钟的时钟转换芯片

2020-04-03 15:43:18

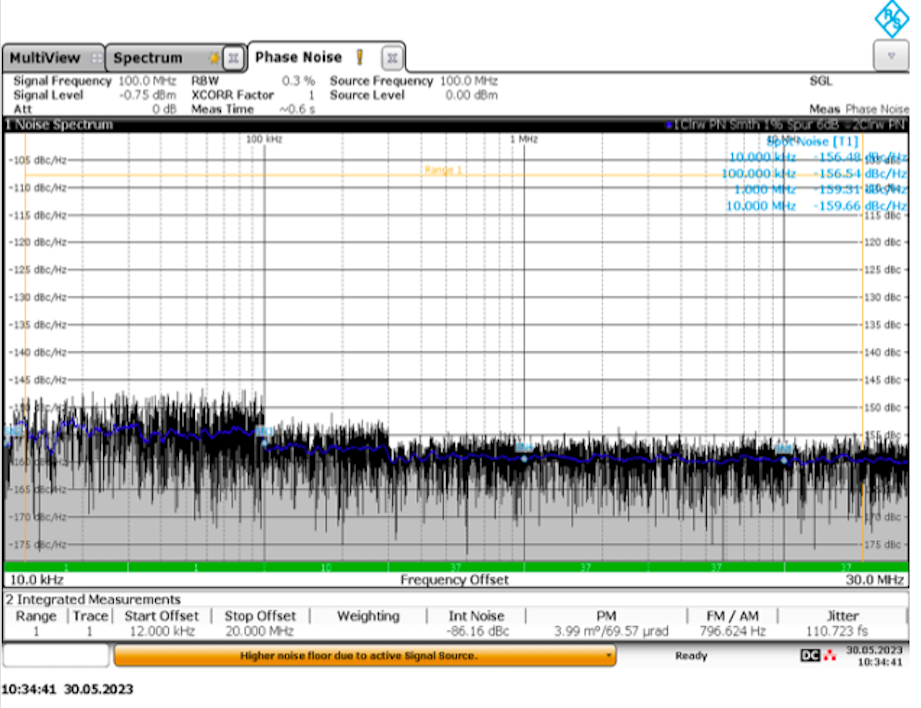

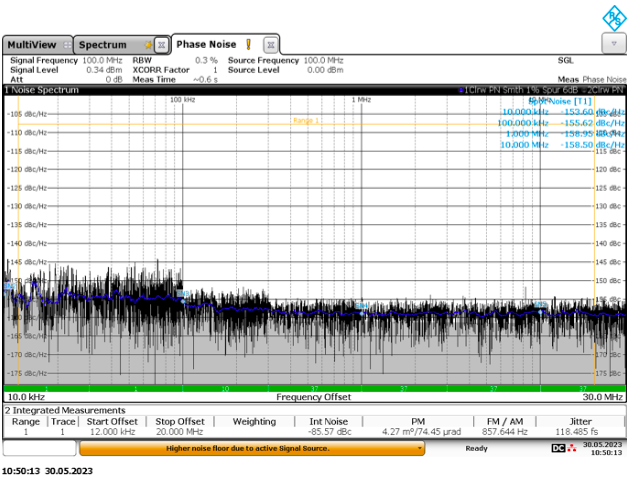

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

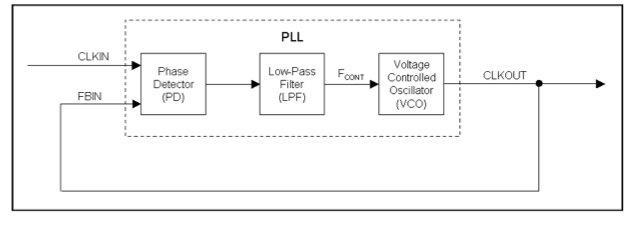

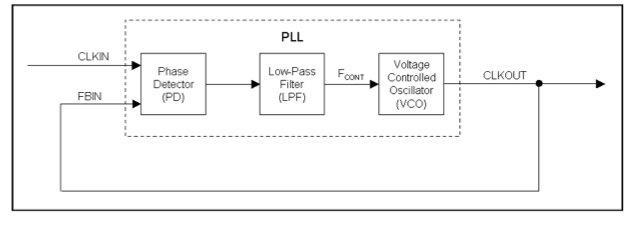

怎么设计一种用于多路输出时钟缓冲器中的锁相环?锁相环主要结构包括哪些?

2021-04-20 06:27:26

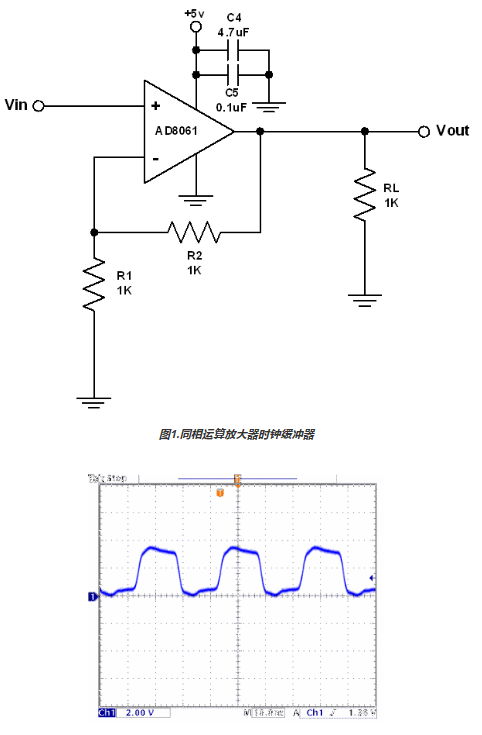

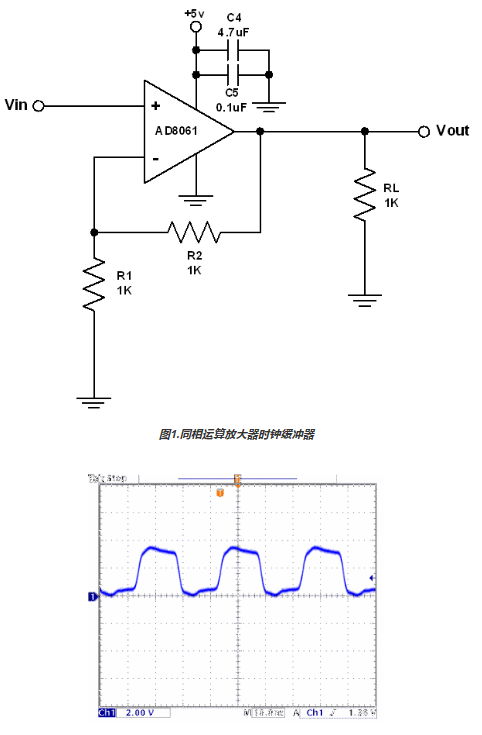

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

嗨,大家好! 我遇到了一个问题,希望能帮助我。当我使用chipcope分析我的设计时,我发现全局差分时钟引脚与chipcope端口没有连接,因为它没有端口与芯片内的差分时钟引脚相连,但它

2020-06-12 14:22:16

了就是下雨了。今天咱们来看看零延时缓冲器吧。也是由缓冲一词想到的。它是指一种可以将一个时钟信号扇出成多个时钟信号,并使这些输出之间有零延时和很低的偏斜的器件。此器件很适合用于要求输入到输出和输出到输入

2014-05-20 17:32:38

`请问高速缓冲器是什么?`

2019-08-23 16:32:59

US5D310是一款支持2.1GHz、2组10路差分输出的时钟缓冲器,每组输出可独立配置,适用于高频、低抖动时钟分配和电平转换。完全兼容

2021-09-27 16:54:19

US5D308是一款支持2.1GHz、2组8路差分输出的时钟缓冲器,每组输出可独立配置,适用于高频、低抖动时钟分配和电平转换。完全兼容TI

2021-09-30 10:13:18

US5D306是一款支持2.1GHz、2组6路差分输出的时钟缓冲器,每组输出可独立配置,适用于高频、低抖动时钟分配和电平转换。完全兼容TI LMK00306

2021-09-30 13:51:29

US5D304是一款支持2.1GHz、4路差分输出的时钟缓冲器,适用于高频、低抖动时钟分配和电平转换。完全兼容TI LMK00304。

2021-09-30 14:00:06

US5D210是一款支持2.1GHz、1分10路LVDS差分输出的时钟缓冲器,适用于高频、低抖动时钟分配和电平转换。完全兼容IDT 5T9310

2021-09-30 14:09:18

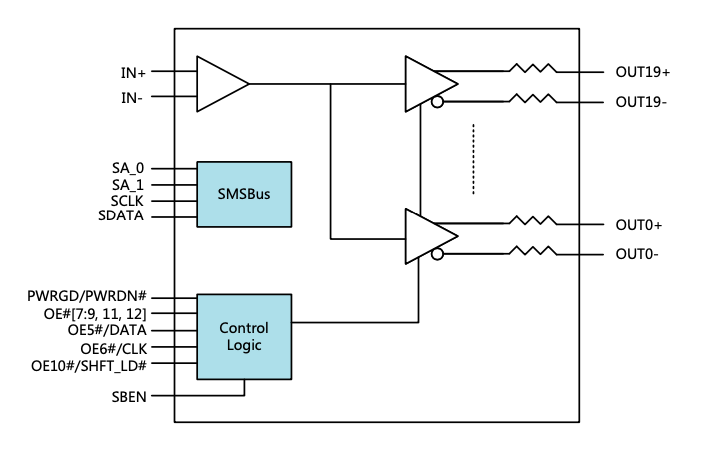

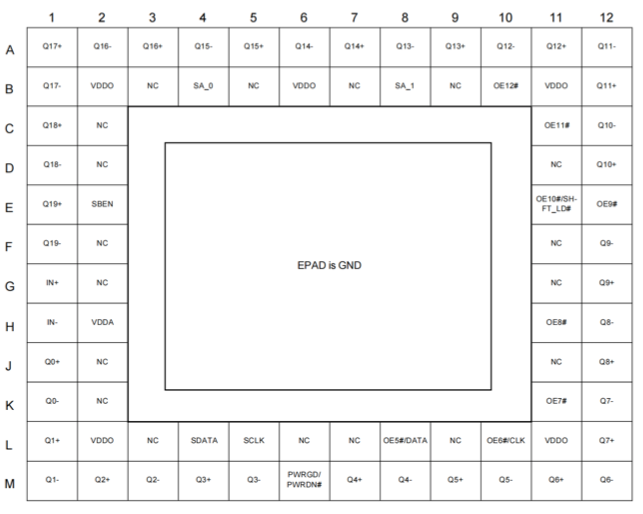

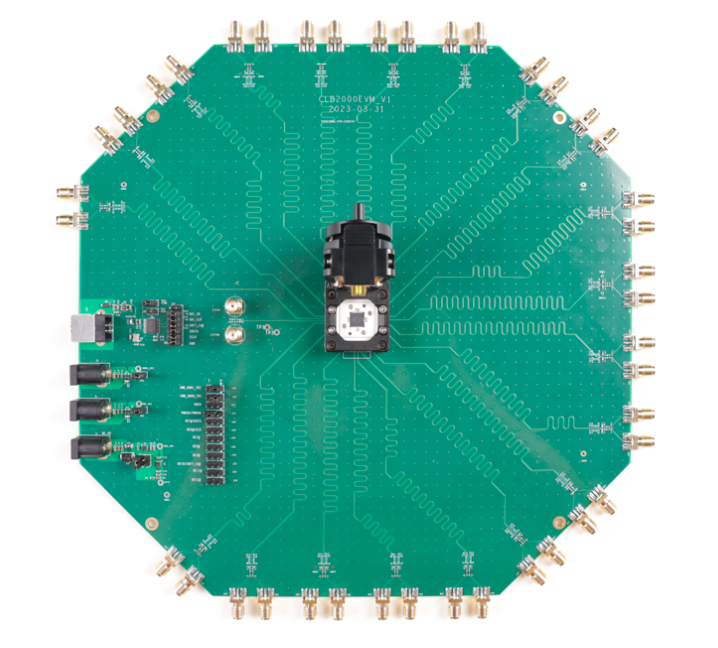

符合 DB2000QL 标准、适用于第 1 代到第 5 代 PCIe® 的 20 路输出时钟缓冲器 Function Clock buffer, Differential

2022-11-30 16:58:52

时钟缓冲器芯片 10路单端buffer是一款高性能、低噪声的LVCMOS房出缓冲器,此缓冲器可以从单端、差分或晶体输入中分配出10路超低抖动时钟。典型应用场景:· RRU基准分布· SONET

2024-01-26 11:09:00

MAX19996 具有片内LO缓冲器的完全集成、2000MHz至3000MHz下变频混频器

Maxim推出具有片内LO缓冲器的完全集成、2000MHz至3000MHz下变频混频器MAX19996。器件采用Maxim

2008-10-09 08:17:31 721

721 TI推出正弦至正弦波时钟缓冲器

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款

2009-11-30 10:53:51 815

815 TI新推高集成正弦波时钟缓冲器可显著降低成本,节省板级空间

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦

2009-12-01 08:43:11 1112

1112 缓冲器,缓冲器是什么?

buffer 中文译名: 缓冲,缓冲器,缓冲液 解释:1、 电信设备。在数据传输中,用来弥补不同数据处

2010-03-08 13:30:11 2253

2253 缓冲器,缓冲器基本原理是什么?

最基本线路构成的门电路存在着抗干扰性能差和不对称等缺点。为了克服这些缺点,可以在输出或输

2011-09-03 19:10:46 9257

9257 Silicon Laboratories (芯科实验室有限公司)日前宣布扩展其PCI Express(PCIe)时钟发生器和时钟缓冲器产品组合。

2012-02-02 09:31:56 1395

1395 日前,德州仪器 (TI) 宣布推出 2 款最新通用时钟缓冲器系列,进一步壮大其高性能时钟缓冲器产品阵营。CDCLVC1310 LVCMOS 时钟缓冲器可在晶振模式下实现 –169 dBc/Hz 的业界领先相位噪声

2012-04-05 08:47:28 1062

1062 中国,北京-2014年12月4日-为互联网基础设施提供高性能时钟解决方案的领导厂商Silicon Labs(芯科实验室有限公司,NASDAQ:SLAB)今天宣布推出PCI Express(PCIe) Gen1/2/3扇出缓冲器,此产品为包括服务器、存储器和交换机在内的数据中心应用而设计。

2014-12-04 10:54:49 1004

1004 三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器三态缓冲器

2015-11-16 11:59:30 0

0 LMK0033x是德州仪器(TI)推出的业界最低抖动的PCIe时钟扇形缓冲器。现在就让德仪的工程师向你介绍它的具体情况吧!

2018-06-13 11:52:00 4883

4883 EngineerIt-测量时钟扇出缓冲器的残余噪声

2018-08-13 00:23:00 3233

3233 面向下一代数据中心应用的四款全新20路微分时钟缓冲器,远超PCIe®第五代(Gen 5)防抖标准。新推出的ZL40292(终端电阻85Ω)和ZL40293(终端电阻100Ω)专门依据最新的DB2000Q规格设计,而ZL40294

2019-07-02 14:48:10 5207

5207 本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈时钟输入端的电容负载对生成早期

2021-06-15 10:48:41 2103

2103

电子发烧友网站提供《DC1954A 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 04:50:23 8

8 电子发烧友网站提供《DC1954A 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 04:54:37 9

9 电子发烧友网站提供《NB6N11SMNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 04:57:05 11

11 电子发烧友网站提供《NB6L611MNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 04:58:58 11

11 电子发烧友网站提供《NB6L72MMNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:00:15 12

12 电子发烧友网站提供《NB6L11SMNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:01:04 9

9 电子发烧友网站提供《NB6L14MMNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:01:59 11

11 电子发烧友网站提供《ADCLK846/PCBZ 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:02:52 7

7 电子发烧友网站提供《ADCLK944/PCBZ 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:03:49 12

12 电子发烧友网站提供《NB7L14MNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:04:39 13

13 电子发烧友网站提供《NB6N14SMNGEVB 时钟缓冲器参考设计.pdf》资料免费下载

2020-12-31 05:05:23 9

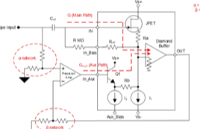

9 本文将探讨与全新BUF802 Hi-Z缓冲器单芯片实施相比,分立式缓冲器复合环路实施存在的设计难题。

2022-02-11 11:58:48 2745

2745

全球半导体解决方案供应商瑞萨电子(TSE:6723)近日宣布,率先推出符合PCIe Gen6严格标准的时钟缓冲器和多路复用器。

2022-04-15 11:18:51 1253

1253 IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1500

1500

KOYUELEC光与电子提供技术支持有容微电子GM50301:超低附加抖动差分输出时钟缓冲器

2022-05-07 11:38:45 2271

2271 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1070

1070 什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

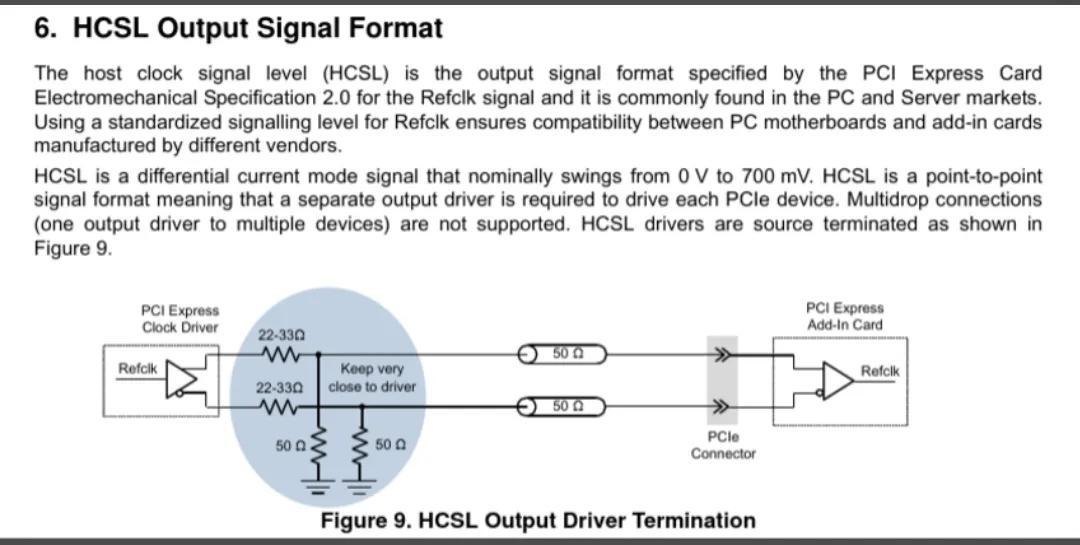

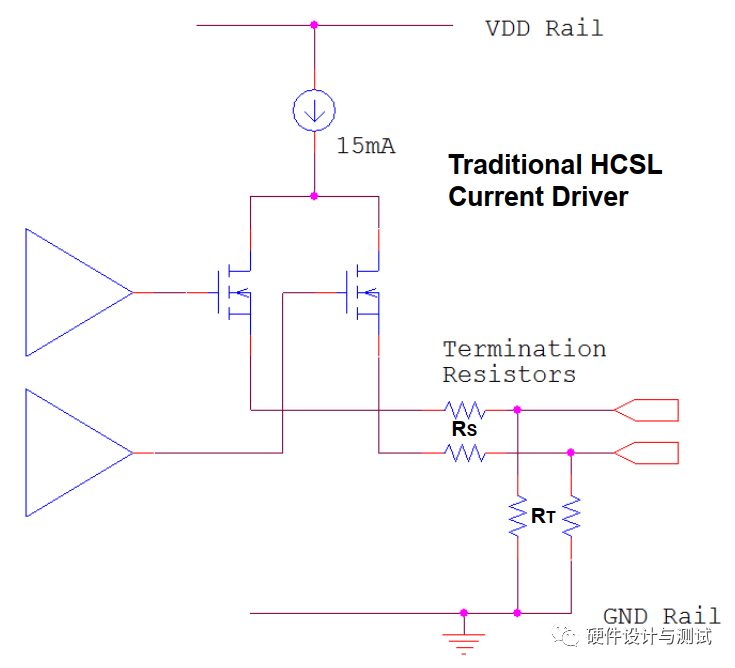

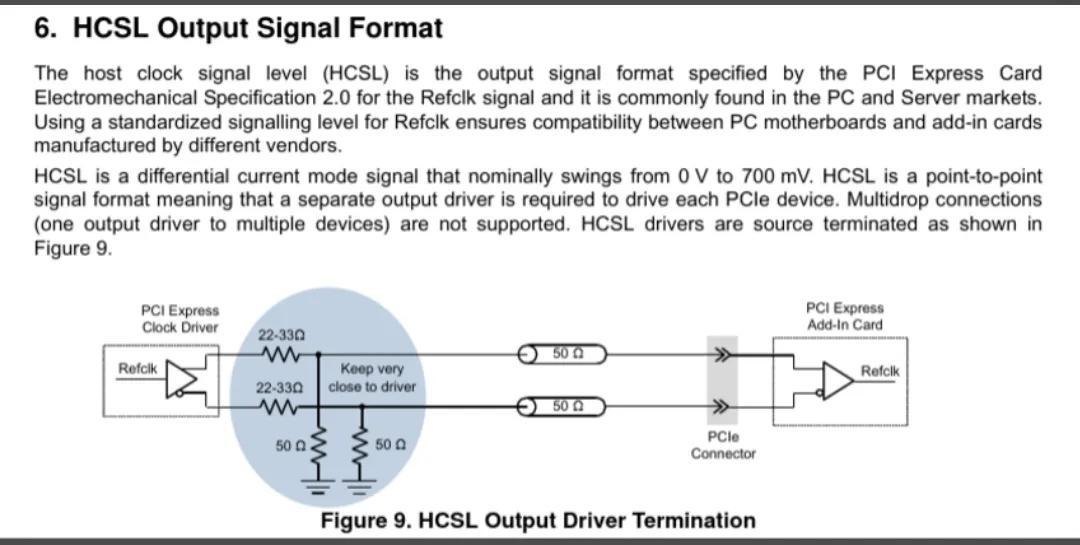

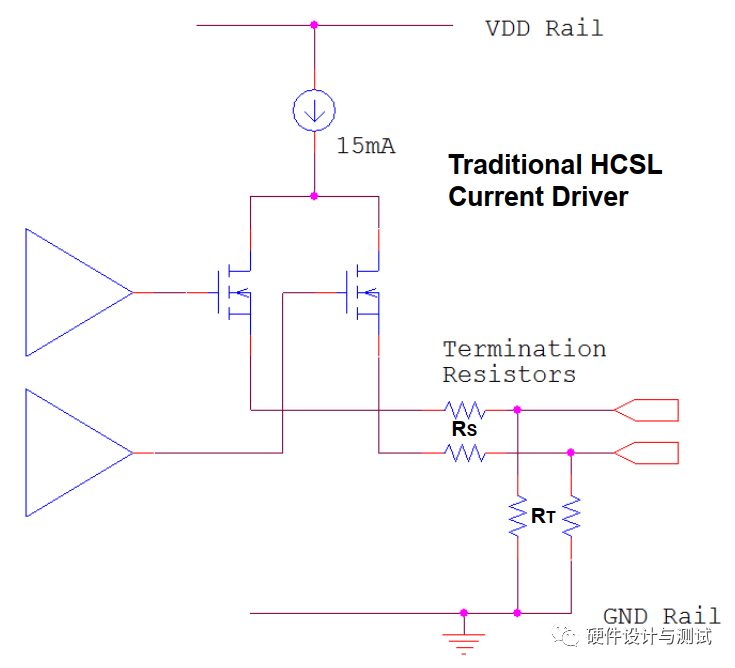

HCSL(HCSL--High−speed Current Steering Logic)一般用于PCIE参考时钟的电平类型,根据规范需要下拉电路,如下图HCSL之间的DC耦合。HCSL为电流输出驱动,输出结构由通常通过50Ω电阻器接地的15 mA开关电流源驱动。 标称信号摆幅为750 mV。

2023-04-20 11:39:38 1707

1707

液压缓冲器强度是否能够调节,取决于液压缓冲器的种类,目前市面上较为常用的液压缓冲器包括可调液压缓冲器、不可调液压缓冲器,这两种缓冲器调节强度的实际效果是不一样的。

2023-04-24 16:12:01 2158

2158 HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47:57 1636

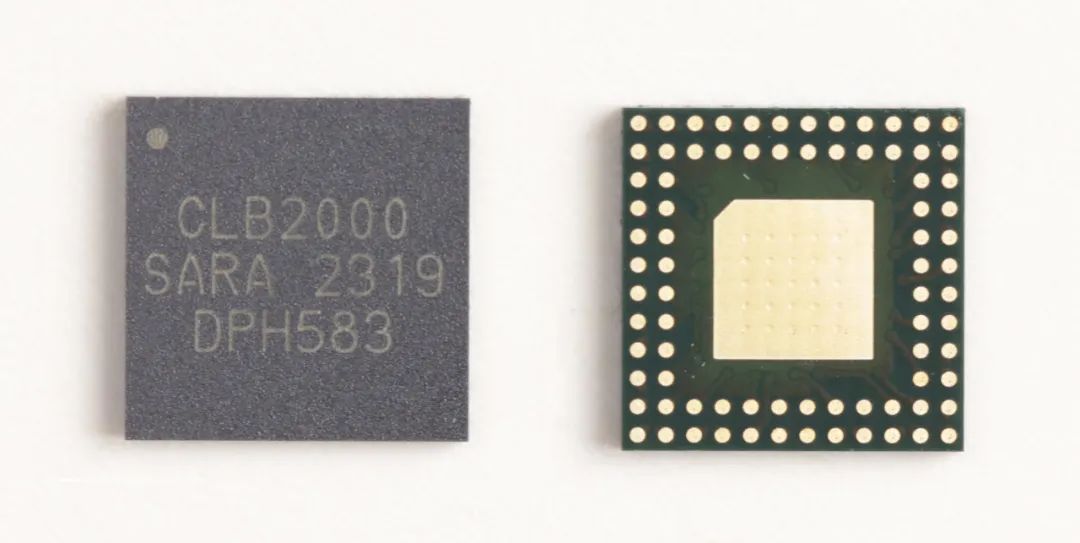

1636 高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29:55 805

805

在消费电子应用中,与典型的时钟缓冲应用相比,其频率往往较低,要求也更低,廉价的高速运算放大器(~100 MHz带宽)可以为传统时钟缓冲器提供有吸引力的替代方案。高速放大器可能比传统时钟缓冲器便宜,但它们可以适应各种设计配置。

2023-06-17 17:29:14 706

706

时钟缓冲器选型目录

2021-11-19 16:38:53 789

789

Diodes(达尔科技)是全球主要的差分时钟IC供应商。Diodes的差分时钟讯号缓冲器产品组合涵盖了多种不同输出讯号(LVPECL,LVDS,HCSL,LowpowerHCSL)与输出端口数

2022-10-19 11:08:24 350

350

HCSL:高速电流控制逻辑(High-speed Current Steering Logic)是Intel为PCIe参考时钟定义的差分时钟,用于PCIe2.0电气规范中定义对RefClk时钟所定义

2023-09-15 14:39:54 2447

2447

电子发烧友网站提供《低倾斜1到4时钟缓冲器524S数据表.pdf》资料免费下载

2023-12-21 10:37:32 0

0 电子发烧友网站提供《551S低倾斜1到4时钟缓冲器数据表.pdf》资料免费下载

2023-12-21 10:41:18 0

0 等应用已集成越来越多的PCIe终端,矽力杰新一代高性能PCIe时钟缓冲器SQ82100可以为系统提供20路超低附加抖动的LP-HCSL参考时钟,能够简化系统布局,进一步提高

2023-12-20 08:19:38 240

240

电子发烧友App

电子发烧友App

评论