AHCC2001PCI/CPCI 是能提供 4 路高速串行数据通信的模板, 完成系统内部计算机网络与外部多路串行接口的互连功能。它内含一片高性能的串行通信控制器,可以用于各种高速数据通信场合。每路

2019-04-25 09:40:07

74LS194引脚功能74LS194功能特征74ls194串行数据到并行数据的转换

2021-03-02 07:00:20

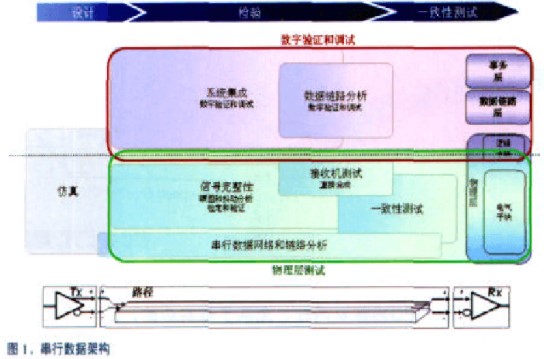

和其它8000 系列采样示波器上使用。关闭的眼图、接收端均衡和发送端目前,大量的串行数据链路设计和标准进入了信道(互连)严重限制高速信号、使接收端一端眼图关闭的时代。经过链路传输后可以使用均衡方法张开

2008-11-26 10:44:02

` 本帖最后由 Stark扬 于 2018-9-26 08:56 编辑

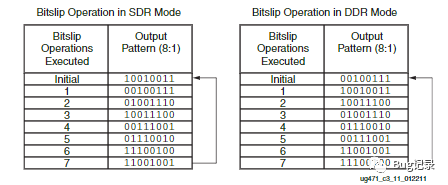

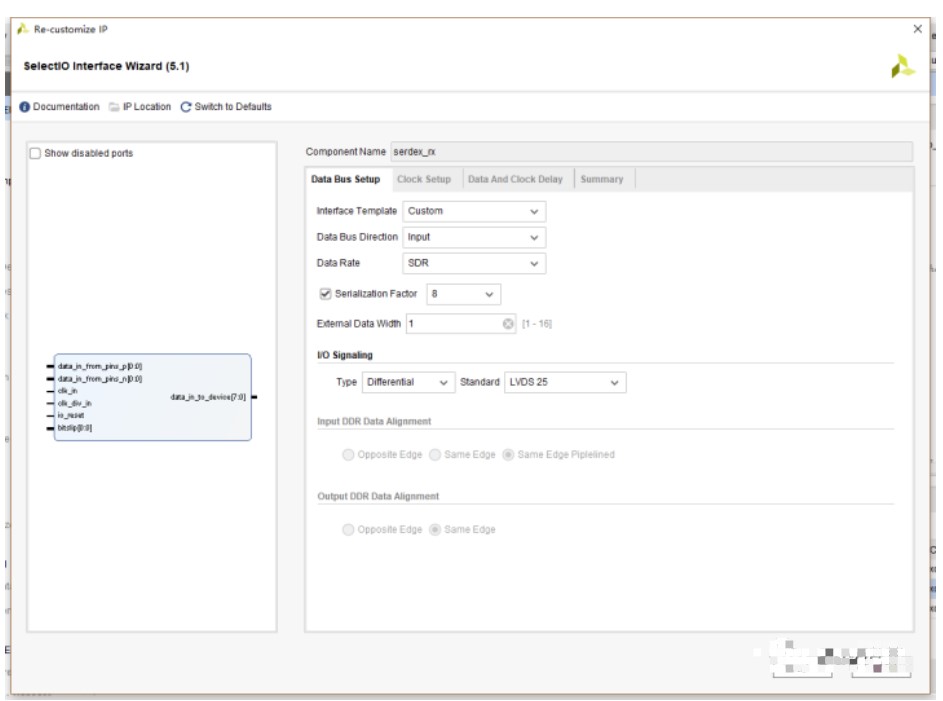

我使用的是序列因子为4的iserdes,数据输入形式为6bit的差分数据。我在对设计进行仿真时发现,转成单端后,只有最低

2018-09-22 15:51:22

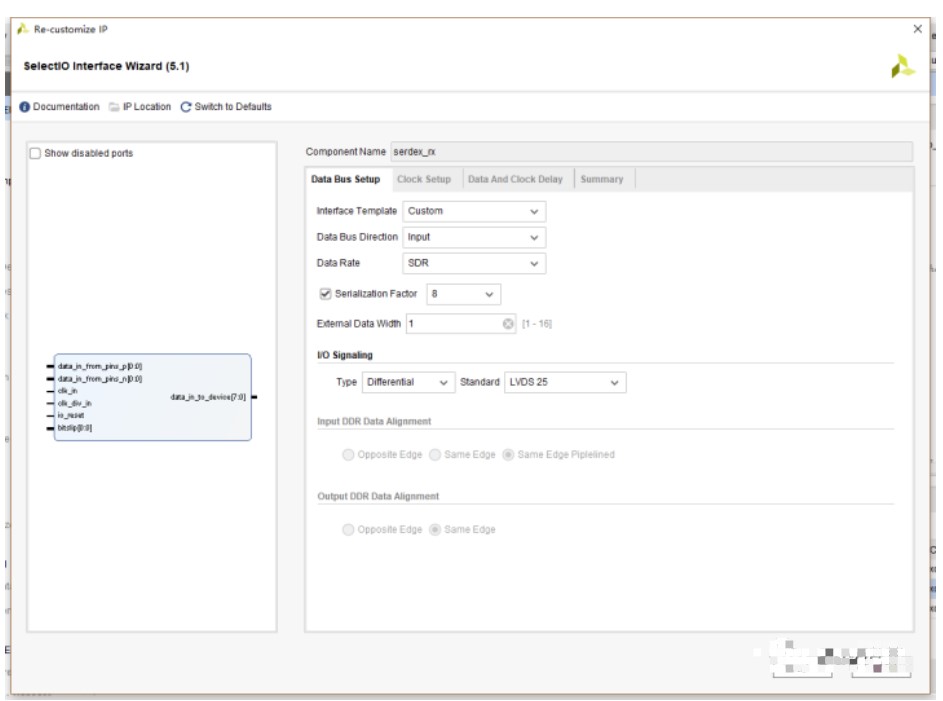

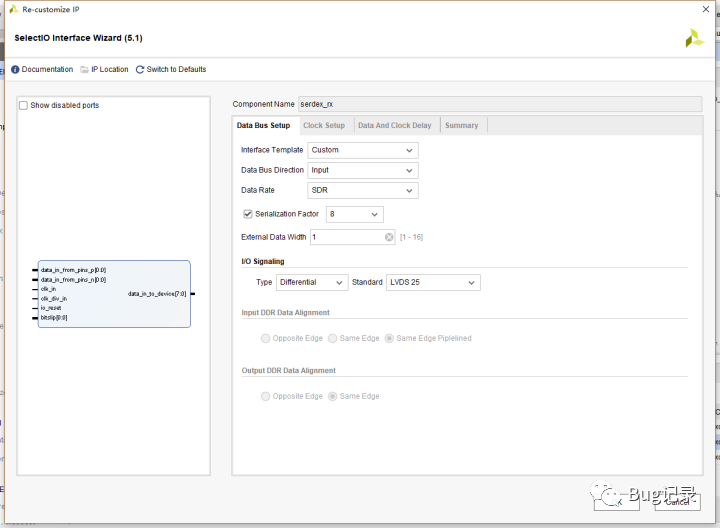

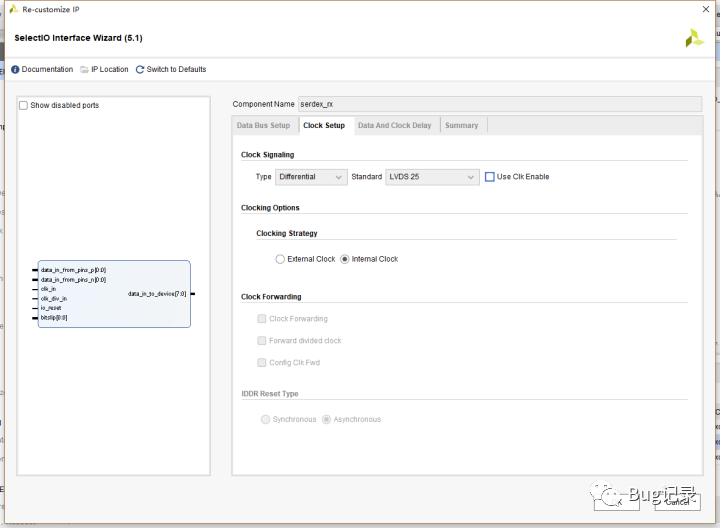

现在输入2路lvds串行数据和1路lvds时钟信号,频率480M,请问如何解出串行数据,并恢复成并行TTL信号

2013-04-28 18:08:32

摘要:串行数据通信要解决两个关键技术问题,一个是数据传送,另一个是数据转换。所谓数据传送就是指数据以什么形式进行传送。所谓数据转换就是指单片机在接受数据时,如何把接收到的串行数据转化为并行数据,单片机在发送数据时,如何把并行数据转换为串行数据进行发送。

2012-07-31 23:27:44

发送串行数据,后者用来接收串行数据。两者物理上是不同的,只是共用一个地址99H。2)输入移位寄存器:在接收控制器的控制下,将输入的数据位逐位移入接收SBUF。3)串行控制寄存器SCON:控制串行通信的工作方式,并反映串行通信口的工作状态。4)定时器T1:作波特率发生器,控制传输数据的速度。2.串行通

2021-12-06 07:30:10

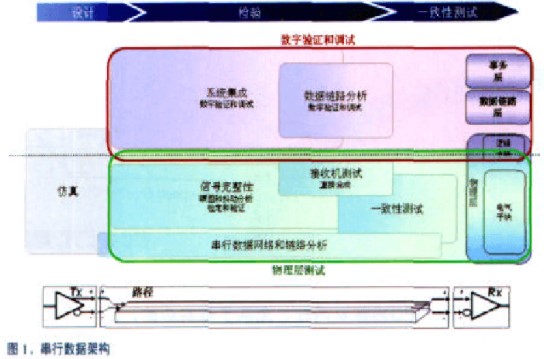

小弟这次给大家带来了串行数据一致性测试和验证测量基础知识其中提到了一些高速串行信号的测试测量方法和简单的原理性介绍,适合初学者使用。PS。这其中提到的一些测量设备现在已经升级为最新的仪器设备,但是测试的原理和技术还是可以让大家闲暇时候品一品的。如有任何问题,欢迎坛友们与小弟交流~~~

2013-04-16 16:17:23

想各位高手来指教一下串行发送字节和读取字节以及数据的写法,以及使用方式。

2013-08-25 23:34:27

由图所示,第一个脉冲唤醒作用,后面8个脉冲下降沿时发送数据。 我现在要写个程序来接收这串数据,用51单片机的INT0中断, 第一个唤醒脉冲的下降沿触发中断,进入中断后,在每个时间下降沿时读取数据口

2013-11-05 21:58:10

计算机主板上的典型总线结构有什么共同点?高速串行数据链路一致性测试的难点有哪些,该如何应对?

2021-04-09 06:47:14

高速CAN通讯总线接收到无效串行数据是何原因?怎么解决呢?

2023-05-09 10:39:29

32位并行数据转为串行输出时,出现部分数据错误,想请教一下可能是什么原因导致的

2017-09-12 10:46:53

我发现了一个错误,该错误使UART 中的串行数据无法传输

我使用

frightanic.com

分支的这些文件 NodeMCU 自定义构建:主

提交

2023-05-09 06:31:27

RS-232、RS-422、RS-485都是串行数据接口标准; RS-232:RS-232是全双工通信方式,采用不平衡传输方式,即单端通讯,收发端数据信号是相对于信号地的。有RX和TX两个信号端

2019-04-23 09:40:05

RocketIO高速串行接口本人在北京工作6年以上,从事FPGA外围接口设计,熟练使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX协议,Aurora协议

2014-03-01 18:46:35

我可以知道 SPC57S-Eval 套件板上的哪个引脚用于串行时钟和串行数据吗?我想将陀螺仪传感器连接到板上。

2022-12-01 06:13:04

如题,补充 由于下位机发送数据飞非常快,用中断接收数据的话,MCU一直进入中断,无法进行数据处理?如何解?小白求大神指点!!

2015-12-09 20:50:06

嗨,我正在使用XILINX IP-Core Generator的GTX。我正在使用Kintex-7。在接收器中,接收器接收串行数据并转换成并行数据,并行sync_header。 PMA如何将64位数据

2020-07-23 08:14:53

磨练设计思想:输入信号 clk 和 D【32】(32bit并行数据),经过FPGA转换后,输入m_clk和 D(1bit的串行数据)。要求传输速度高,可靠性好。大家各抒己见,写写自己的总体思想(当然是详细点好)。

2008-09-19 23:53:51

/*名称:并行数据转换为串行数据 说明:切换连接到并串转换芯片74LS165 的拨码开关,该芯片将并行数据以串行方式发送到 8051 的RXD引脚,移位脉冲由 TXD提供,显示在 P0 口

2012-03-02 09:38:12

/*名称:串行数据转换为并行数据 说明:串行数据由 RXD 发送给串并转换芯片 74164,TXD 则用于输出移位时钟脉冲,74164 将串行输入的 1 字节转换为并行数据,并将转换的数据通过 8

2012-03-01 09:40:49

若1bit串行信号data_in按高位先发的顺序传输一个8bit的数据,data_en为使能信号,请用位拼接符实现串行数据的接收并输出接收的8bit数据data[7:0]

2023-08-07 16:05:19

三种常用的串行数据传输总线一、SPI1.1 概念SPI(Serial Peripheral Interface - 串行外设接口)是一种用于短距离通信(主要是嵌入式系统中)的同步串行通信接口规范

2022-02-10 06:32:34

接口是外设和主设备连接的方式/规则/协议的名称;XX总线是主设备连接某一类接口的名称1.串口串行数据接口标准(根据时间发展顺序介绍):RS-232;命名为EIA-232-E标准;通信距离短、速率低

2021-12-17 08:29:16

联系的。不会因为这位有错误,使下一位不能传输。并行数据是一组数据其中一位不对,整组数据都不行。高速并行,串行布线的区别并行数据因为是一组一组一起传的,每一位都必须是一起传输到位,不能说有一位可以迟到一点

2019-10-01 07:00:00

接收器、控制器oller被设置为根据接收到的数据字节打开/关闭一个引脚,但是它没有工作。我试着将计算机输出的内容读到另一台计算机上的串行应用程序上,以调试串行数据,但是数据似乎被正确地发送出去。对此有

2019-06-06 07:07:07

描述JESD204B 链路是数据转换器数字接口的最新趋势。这些链路利用高速串行数字技术提供很大的益处(包括增大的信道密度)。此参考设计解决了其中一个采用新接口的挑战:理解并设计链路延迟。一个示例实现

2018-11-21 16:51:43

高速LVDS数据接收:接收时钟检测(检测接收时钟的存在),接收时钟对齐(对接收时钟进行移相),数据串行转并行,接收数据字节序对齐(Comma码对齐),接收数据Los-of-Sync状态机,8B

2014-03-01 18:47:47

多FPGA系统中自定义高速串行数据接口设计.pdf

2011-03-21 17:28:15

多FPGA系统中自定义高速串行数据接口设计为方便多FPGA系统中主从FPGA之间的命令与数据传输,节省连接的引脚数量,设计了一种基于FPGA的自定义高速串行数据传输模块。对主从串行模块进行了详尽

2012-08-11 11:49:57

你好,我必须发送3个长TIPE可变形式的PLC到CY8C KIT01,我应该使用这个工具包的串行端口,但我没有任何线索如何开始。我应该使用哪些组件来编程它来使用串行端口发送和接收数据。恳求帮助

2019-04-09 12:06:23

如何使用STM32与PC进行数据的相互发送接收?

2021-12-06 06:00:58

USART发送接收的基本方式是什么?如何使用STM32与PC进行数据的相互发送、接收?

2022-02-18 07:38:26

:串口按位(bit)发送和接收字节(byte)的通信方式,可以将来自CPU的并行数据字符转换位连续的串行数据流发送出去,同时可将接收的串行数据流转换为并行的数据字符提供给CPU的器件,一般...

2021-12-24 06:46:50

已知一串行数据,怎么样在这串行数据的头加一个开始标记(如“01111110”),尾部再加一个结束标记,请大家指导指导,谢谢啦

2014-05-26 16:15:28

各位前辈好,新人自学FPGA,现在碰到一个费解的问题,我例化了一个rom核,输出是十位的数据,现在需要接入到一个串行输入的DA模块上,在网上查到说需要将并行数据转换为串行数据输入到DA中,即把十位

2019-03-06 08:55:27

本文介绍了基于Xilinx Virtex-6 FPGA的高速串行数据传输系统的设计与实现,系统包含AXI DMA和GTX串行收发器,系统增加了流量控制机制来保证高速数据传输的可靠性。最后进行了仿真测试,测试结果显示系统可以高速可靠地传输数据。

2021-05-25 06:45:36

我想把一个串行数据发送到一个BLE模块,而BLE模块应该将接收到的串行数据广播到Mesh网络的所有节点(BLE模块)。那么我该怎么做呢????在没有编写任何程序的情况下,是否有任何应用程序可以完成此

2018-10-17 16:18:01

; P2=SBUF;delay(20); } } 用三个LS165,将并行数据转为串行数据,为什么第一个芯片控制的,控制的第二部分LED,第二个165控制第三部分LED,求助,这是为什么

2017-05-03 00:17:09

内容如题!就是串行数据输入430再从430并行输出数据,并将数据显示到液晶屏上去。求程序如何编写?在这里先谢谢大神了

2013-04-24 19:42:45

用于高速数据转换器的串行接口有哪些选择?

2021-04-09 06:55:28

串行数据系统的基本知识抖动的基本概念串行数据系统中误码率的概念抖动的来源

2021-04-07 06:19:00

怎么模电的方法设计一个红外串行数据传送整形电路?

2020-05-03 21:24:55

AD2S1200的串行数据输出波形及处理的角度波形是什么样的?

2023-12-20 06:07:28

各位高人! 请问at91sam7s64中,能否利用SSC进行18位串行数据接收?

2018-07-09 01:05:17

嗨,大家好,我正在使用ML550板的参考设计(xapp856),它使用V5,XC5VLX50T,1136引脚,速度等级-1。接收器侧的16个ISERDES执行1:4反序列化以产生64位的并行总线

2020-06-01 17:18:53

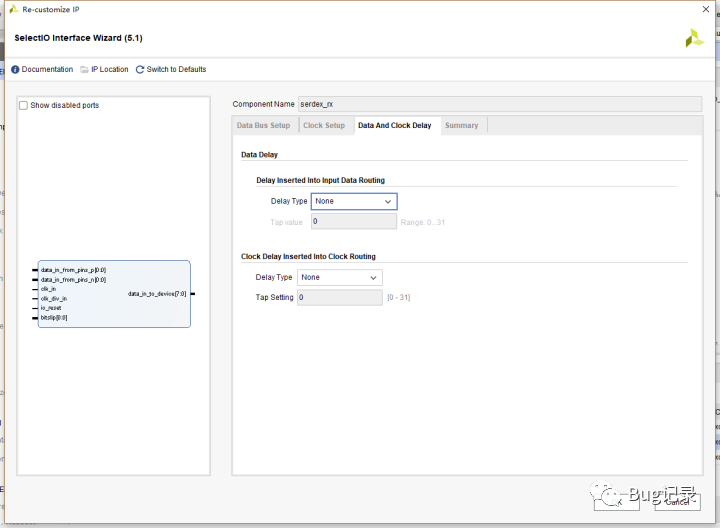

我可以推迟输入数据的Iserdes吗?或者我必须在V5中将IOdealy连接到Iserdes吗?

2020-04-24 09:47:19

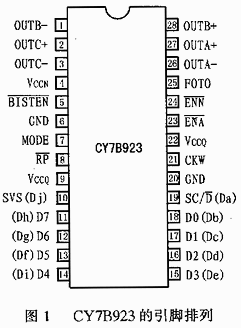

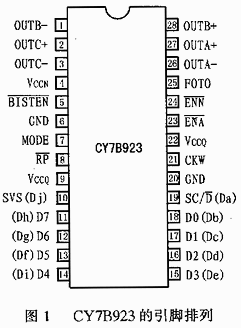

文章介绍了CYPRESS半导体公司推出的一种用于点对点之间高速串行数据通信的发送芯片CY7B923的原理及应用.较详细的介绍了CY7B923的管脚功能、内部组成、工作原理及工作方式.同时给出

2009-04-27 16:45:21 37

37 USB已经越来越被广泛的应用,因为它的高速传输性能和即插即用特性已逐渐取代了传统的串行总线.而如果使用USB实现并行数据的高速传输,同时为MCU、DSP等处理器开发USB接口以实现与PC

2009-04-27 16:55:19 23

23 本文提出了一种串行数据通信系统的设计方案,利用MATLAB 提供的仪器控制工具箱serial 类对象来实现串行数据通信,硬件设计中采用TL16C550C 芯片使设计具有很好的可扩展性,用信号

2009-06-12 15:23:08 23

23 介绍基于Matlab 环境的微机与单片机串行数据通信方法。该方法利用Matlab 的Instrument Control 工具箱的serial 类对象实现串行数据通信,

2009-09-03 12:10:55 25

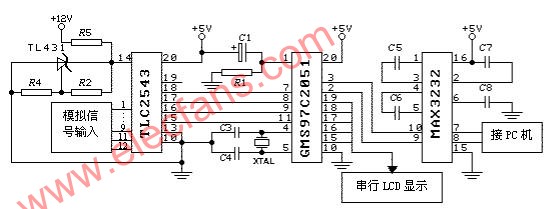

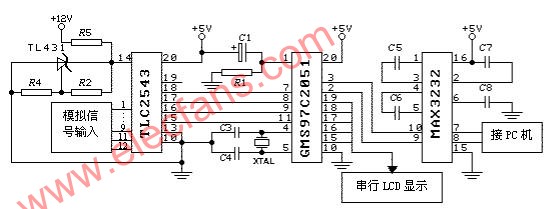

25 以GMS97C2051单片机为核心,采用TLC2543 12位串行A/D转换器,设计了一个串行数据采集/传输模块,给出了硬件原理图和主要源程序。关键词:串行A/D转换器;串行数据传输;GMS97C2051单

2010-06-08 07:53:17 49

49 本基础指南旨在帮助您了解串行数据传输的一般方面,并介绍适用于这些新兴串行技术的模拟和数字测量要求。 串行数据一致性测试和验证测量基础知识本手册将帮助您理解串行

2010-08-05 15:14:53 32

32 摘 要:介绍了FPGA最新一代器件Virtex25上的高速串行收发器RocketIO。基于ML505开发平台构建了一个高速串行数据传输系统,重点说明了该系统采用RocketIO实现1. 25Gbp s高速串行传输的设

2010-09-22 08:41:18 43

43 串行数据转换器接口

问:我现在需要安装节省空间的数据转换器,认为串行式转换器比较适合。为了选择 和使用这种转换器,请问我需要了解些什

2010-01-04 17:40:44 1719

1719

一个单片机串行数据采集/传输模块的设计 摘 要:以GMS97C2051单片机为核心,采用TLC2543 12位串行A/D转换器,设计了一个串行数据采集/传输模块,给

2010-04-24 22:41:42 1778

1778

对于现代的高速串行系统,系统之间的协调工作显得更为突出,协议间的任何冲突也会导致整个系统出现问题,本文将为大家重点介绍力科示波器针对高速串行信号物理层、链路层和协议层的解决方案。

2011-03-16 10:09:29 1628

1628

摘要 RS-232 或许是PC 和电信应用中最成功的串行数据标准RS-485 和RS-422 则是工业应用中最成功的标准这些标准并不是直接兼容的但是在控制场合和仪表应用中常常需要在它们之间进行数据

2011-07-11 18:02:44 94

94 高速串行数据链路的一致性测试是个复杂的课题,既要求测试设备厂家能提供高性能的仪器,又要求测试工程师能充分利用仪器去解决问题。

2012-04-24 16:00:20 994

994 本文讨论了RS232串行数据截取器的设计方案,并做出了产品,进行了实验。系统稳定、可靠,可以有效地截取串行通信数据。该系统可以为有相关需求的人员提供帮助。

2012-06-01 16:46:35 3980

3980

。。。。。。串行数据转换为并行数据。。。。。。。

2015-11-10 10:01:10 9

9 。。。。。。并行数据转换为串行数据。。。。。。。

2015-11-10 10:00:07 0

0 多FPGA系统中自定义高速串行数据接口设计

2016-05-10 11:24:33 24

24 基于8051的Proteus仿真-串行数据转换为并行数据

2016-09-01 23:32:32 10

10 基于8051的Proteus仿真-并行数据转换为串行数据

2016-09-01 23:32:32 16

16 本文介绍了TDR阻抗测试和高速串行链路分析,首先介绍了高速串行数据链路的挑战,然后对高速串行数据链路时域-TDR和高速串行数据链路频域-S参数:IConnect 进行了分析,最后提出了泰克TDR与S参数的解决方案。

2017-10-12 16:42:16 7

7 随着现代工业科技飞速发展,某些特定的大容量数据系统要求有很高的采样频率及较高的通信效率。本文通过ADC12D800RF实现高速采样,并基于Xilinx Virtex6 FPGA的GTX高速串行接口

2017-11-17 04:37:01 11284

11284

移位寄存器是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。本文主要介绍了74LS194引脚功能与特征,其次详细的说明了74ls194串行数据到并行数据的转换。

2017-12-22 14:18:52 24814

24814

12864液晶串行和并行数据显示的源程序

2018-04-08 17:51:55 57

57 在数字视频中,为了便于数字信号的远距离传输,将并行数据转换成串行数据,经电缆驱动器通过电缆传输给接收端。SDI就是这种串行数据接口的简称。本文以1080i/50系统为例,对HD-SDI的原理做简单

2018-09-04 09:38:00 14121

14121 计算机、消费电子和通信行业设计核心正采用最新的高速串行技术,数据传送速率持续提高,如10Gb/s以太网的出现、PCI Express已经从1.0版演进到2.0版,速率也从2.5Gb/s提高到

2019-09-11 08:03:00 1353

1353

本文档的主要内容详细介绍的是单片机并行数据转换为串行数据的仿真电路图

2020-01-10 14:37:35 12

12 本文档的主要内容详细介绍的是单片机串行数据转换为并行数据的仿真电路图免费下载

2020-01-10 14:37:00 12

12 本文档的主要内容详细介绍的是单片机串行数据转换为并行数据的C语言程序和仿真资料免费下载。

2020-06-11 17:30:39 9

9 本文档的主要内容详细介绍的是单片机并行数据转换为串行数据的C语言程序和仿真资料免费下载。

2020-06-11 17:30:36 10

10 CY7B923是CYPRESS半导体公司推出的一种用于点对点之间高速串行数据通信的发送芯片。CY7B923采用的是基带传输通信方式,并支持带电插拔(热接插)。其内部电路主要包括时钟产生器、输入寄存器、编码器、移位寄存器、三对差分PECL输出对以及测试逻辑等。

2021-05-22 17:20:17 3598

3598

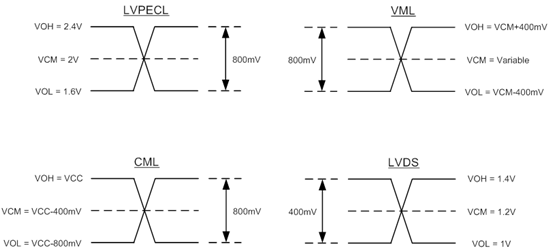

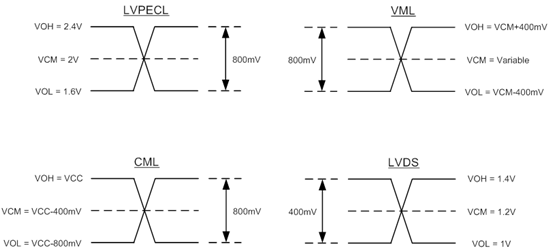

系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通道或时钟通道的传输线路是一项非常重要的技能。

2022-01-28 09:33:00 1333

1333

但是,在内部处理信号时,数据信号往往是多bit信号,而传输过程中需要用到单bit串行传输技术,所以,中间需要有一个转换器,实现并串转换,这就需要用到SERDES技术。

2022-08-20 11:11:09 4044

4044

眼图医生(Eye Doctor)是力科于2006年推出的用于高速串行数字电路设计的强大工具,包括了虚拟探测(virtual probing)与接收端均衡(receiver equalization

2022-09-30 09:08:41 976

976 基于AT89C51单片机并行数据转换为串行数据仿真及代码

2023-05-04 17:50:20 0

0 基于AT89C51单片机串行数据转换为并行数据仿真及代码

2023-05-05 10:32:01 0

0 OSERDES实现并串转换,只需要管发送并不需要管接收到的数据如何,所以它的操作相对于ISERDES来说简单;

2023-06-16 14:14:53 708

708

SerDes是Serializer/Deserializer的缩写,即串行器和解串器,顾名思义是一种将并行数据转换成串行数据发送,将接收的串行数据转换成并行数据的”器件“。

2023-12-13 10:02:42 516

516

电子发烧友App

电子发烧友App

评论