PCI-e包括Card Electromechanical、SFF-8639 Module、oCUlink、Mini Card和M.2,External Cabiling,Label & usage guidelines、Firmware Specification、225/300W High Power Card。

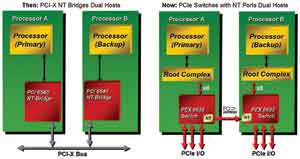

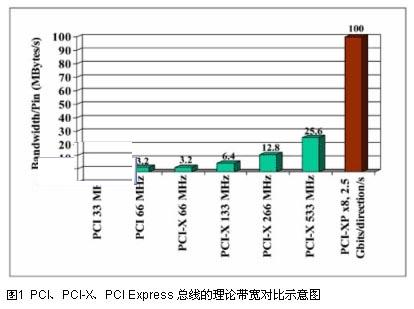

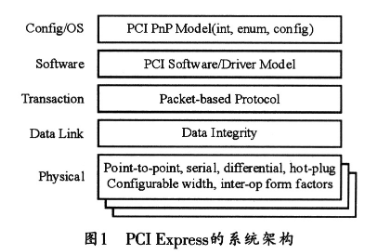

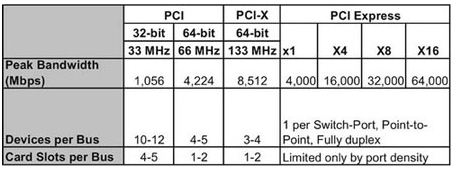

说明:PCI-Express是一种高速串行计算机外设扩展总线,是当前主流的总线和接口标准,它原来的名称为“3GIO”,INTEL交由PCI-SIG(PCI特殊兴趣组织)认证发布改名为“PCI-Express”。这个标准全面取代了旧的PCI,PCI-X和AGP总线。它们的前2代分别为PCI和PCI-X。PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

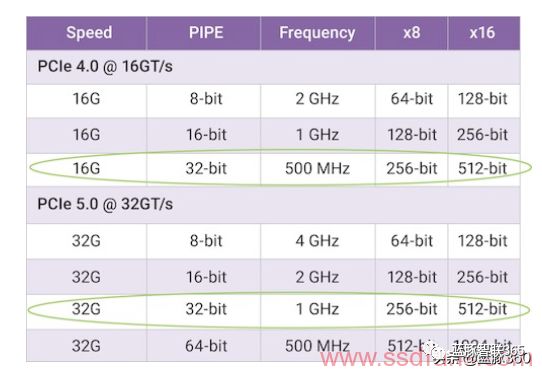

最高速率:32 GT/s,16通道配置时速率可达128GBps.

图片来自网络

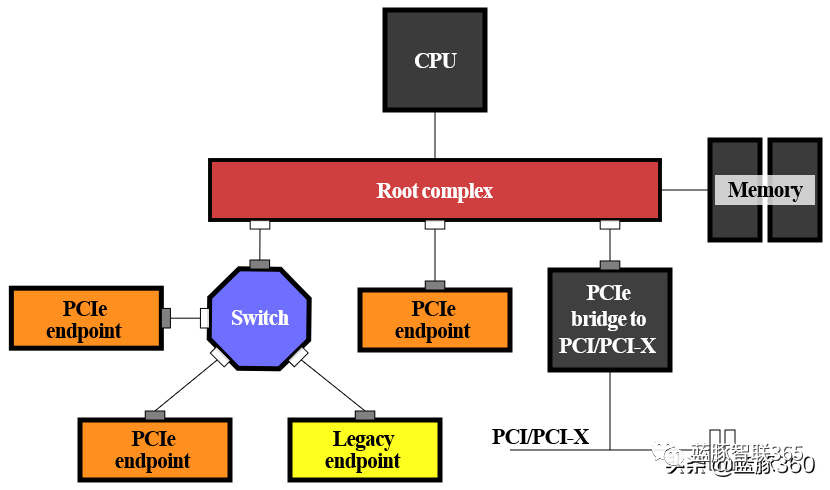

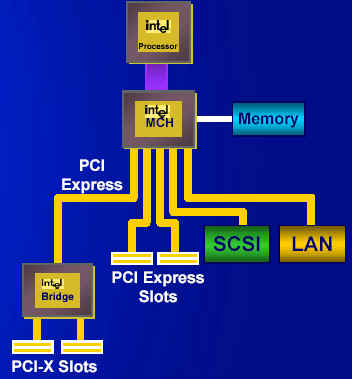

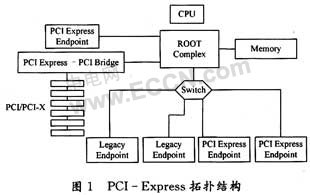

一、接口架构

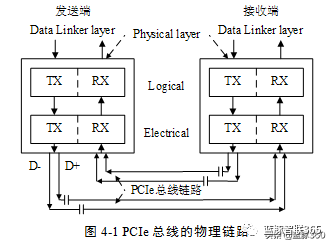

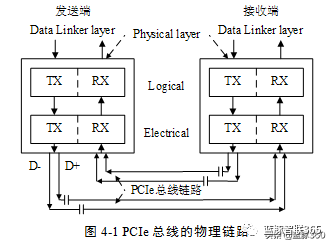

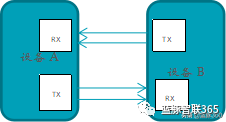

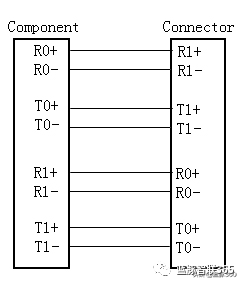

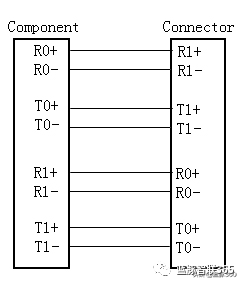

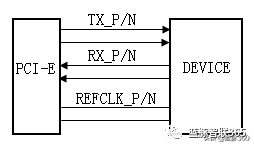

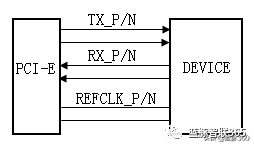

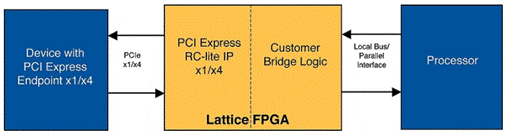

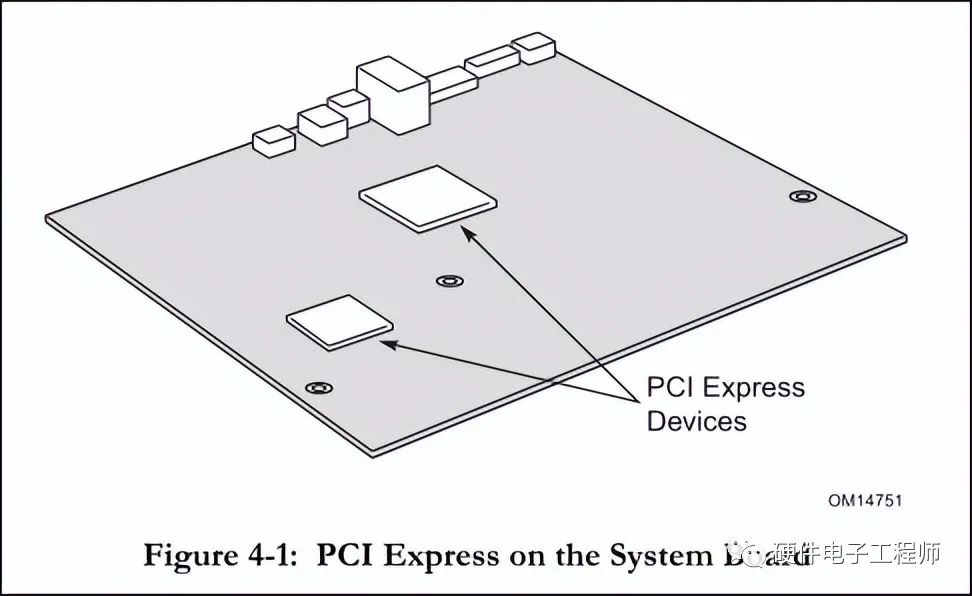

PCIe总线使用了高速差分总线,并采用端到端的连接方式。与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。如下图4-1为PCIe总线的物理链路模型。

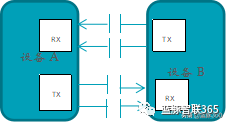

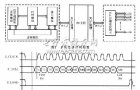

PCIe有差分对1~32对,它义了1、2、4、8、12、16和32对等各种配置,它为全双工通信。比如Wi-Fi 可以使用低速链路(只要1个LINK)而3D图形卡则需要多个链路。1条LANE有4根信号线,有两个差分对,分别负责发射2根,负责接收2根。在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。如下图所示,它们之间是交流耗合(通过电容)。

图1 PCI-Express系统拓扑结构

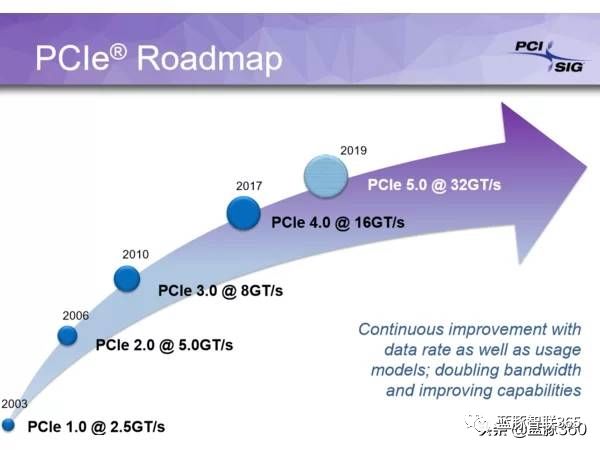

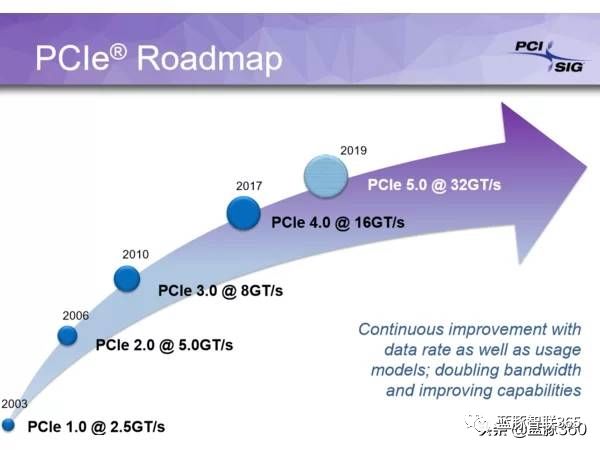

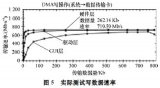

截止当前,PCI-Express已经推出了5个版本,分别是:

1)2002年4月推出的PCI-Express 1.0,单通道带宽为2.5Gbps *2 (因为PCE-Express收发通道独立,可以同时工作,所以带宽加倍),有效带宽为2.5Gbps 20.8=4Gbps

=500MByte/s(PCI-Express通道中传输的数据经过了8B/10B编码,编码效率为80%)。

2)2006年推出的PCI-Express 2.0,单通道带宽为5Gbps *2,有效带宽为5Gbps 20.8=8Gbps=1GByte/s。

3)2010年推出的PCI-Express 3.0,单通道带宽为8Gbps *2,有效带宽为10Gbps

20.8=16Gbps=2GByte/s。

4)2017年推出的PCI-Express 4.0,单通道带宽为16Gbps *2,有效带宽为16Gbps

20.8=24Gbps=3GByte/s。

5)2019年5月推出的PCI-Express 5.0,单通道带宽为32Gbps 2,有效带宽为32Gbps2*0.8=51.2Gbps。

使用LVDS,each lane consists of two unidirectional LVDS pairs。

二、工作原理

在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率;此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCI-e总线特点:

1)双单工,点对点传输,每个Lane包含4根线,2收2发,使用LVDS差分信号,最小差模电压175mV,共模电压3.5V,最长可传输3m。

2)基于包的数据传输方式,支持QOS、VC、TC等特性,支持热插拔,支持电源管理。

3)对传输的数据进行8B/10B变换,调整码流的DC特性,方便接收端的时钟信号恢复。

4)接口带宽可裁减,使用灵活,可根据实际带宽需求选择合适的Lane数量。PCI-Express支持1X、2X、4X、8X、16X、32X(每个“X”代表一个Lane),并且向下兼容其他PCI-E小接口产品。如PCI-E 4X可以插在PCI-E 8X或16X插槽上使用。中国通信人博客v#~.h kg!Y JL9E

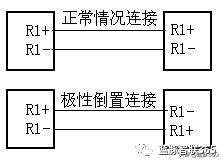

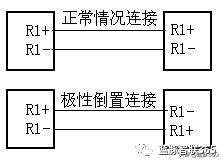

5)支持通道反转,给PCB走线带来更大的灵活性。(此特性并非PCI-E规范强制要求),

6)支持极性倒置功能,方便PCB调线。

PCI-Express总线物理层由逻辑子层和电气子层构成。逻辑子层负责链路的复位,设置链路的速率和带宽,Deskew的测量和补偿,8B/10B编码和解码。

发送端包括:

接收端包括:

- 接收PLL

- 串行/并行转换器

- 弹性缓冲器

- 10B/8B解码器

- 去扰频器

- 字节反拆分逻辑

- 控制字节删除电路

- 数据包接收缓冲

PCI-Express总线的每个Lane有3对信号,其中参考时钟信号可选。如下图所示。

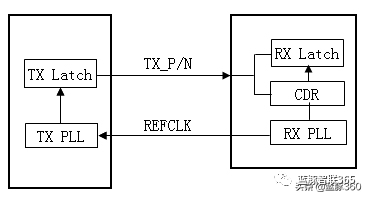

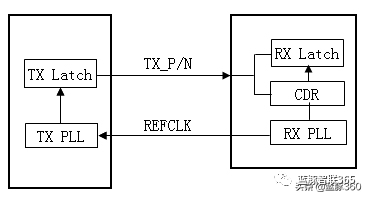

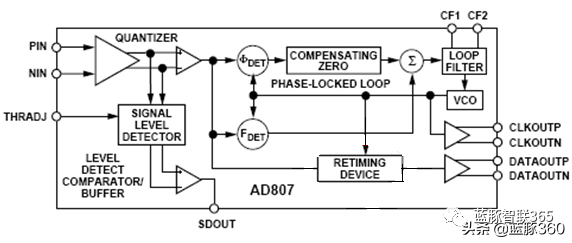

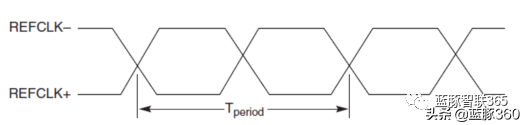

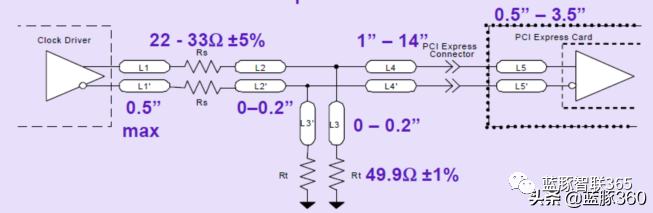

PCI-Express总线的参考时钟为100MHz,精度要求为±300ppm,收发两端的参考时钟可以独立,也可以连接在一起,如果连接在一起,则收发两端参考时钟可以保持同步。如下图所示。

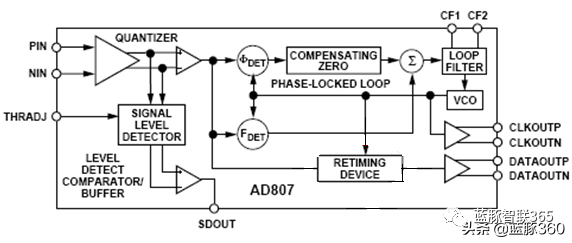

PLL是锁相环,用来锁定收发通道的参考时钟,CDR的英文全称是Clock Data Recover,时钟数据恢复的意思。CDR的典型框图如下。

PCI-Express总线100MHz时钟的电平匹配方式如下所示。

下拉电阻的取值范围为40~60ohm,一般取49.9ohm,串阻的阻值一般根据实际信号幅度进行调整,一般取33ohm,串阻和下拉电阻都放在始端。PCIE信号一般用AC耦合方式,耦合电容放在始端(这里需要特别注意下,一般高速信号的AC耦合电容都是要求放在终端的,PCIE信号AC耦合电容的位置很特别的),电容取值范围为75nF-100nF。

PCIE通道的Deskew,所谓的Deskew是指通道与通道的相位偏移,其主要来源有:

1)芯片驱动端和接收端的差异;

2)印制电路板的阻抗变化;

3)通道线路长度的不匹配;

4)串行化和反串行化逻辑所引入的延迟。

PCIE接收端为了能并行处理数据,必须要去除通道与通道的相位偏移,此动作称为链路的相位补偿,具体方法是通过微调芯片内部的自动延迟电路来实现的。PCIE规范要求,在发送端需要拥有1.5nS的Deskew补偿能力,在接收端需要拥有20nS的补偿能力。所以PCIE总线对个通道的走线长度约束非常宽松,不需要像并行总线那样做等长处理。

PCIE总线支持SSC(拓展频谱时钟)技术,SSC是一种缓慢调制时钟频率的技术,以便降低中心频率处的EMI发射,有了SSC,辐射能量就不会产生2.5GHz或5GHz的噪声尖峰信号,因为辐射被分散到中心频率周围的小频率范围上。使用SSC时,链路两端的最大时钟差异必须在±600ppm,这就几乎强制要求发送端和接收端使用同以参考时钟。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含有时钟恢复模块CDR(Clock Data Recovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传递。

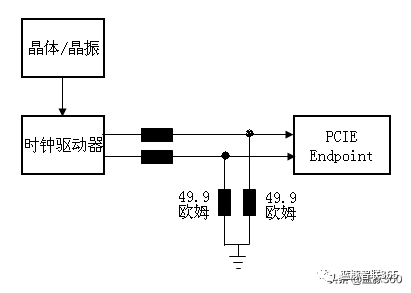

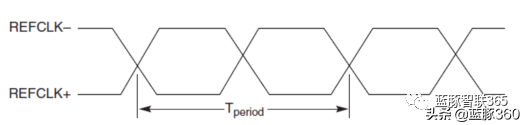

值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟, 时钟信号为差分对REFCLK+和 REFCLK-,如下图所示:

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰值带宽。GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率×数据位宽×2。

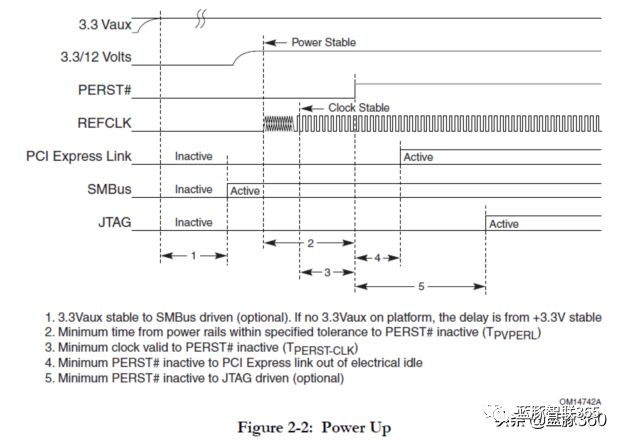

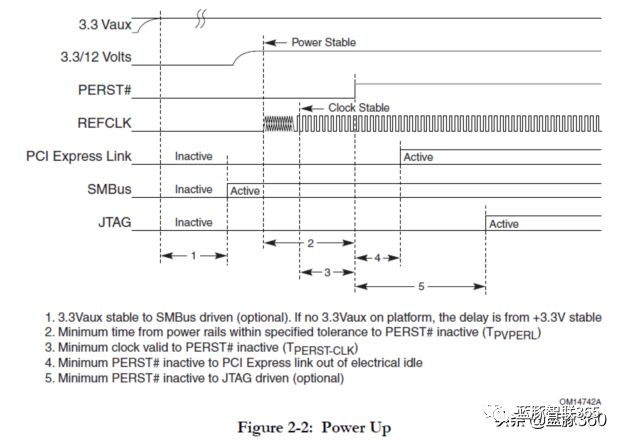

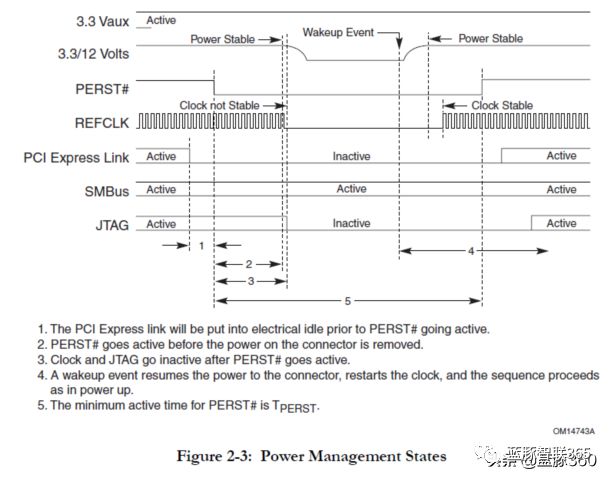

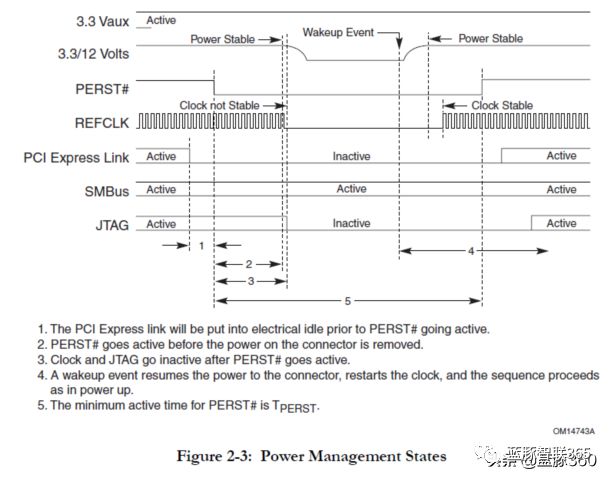

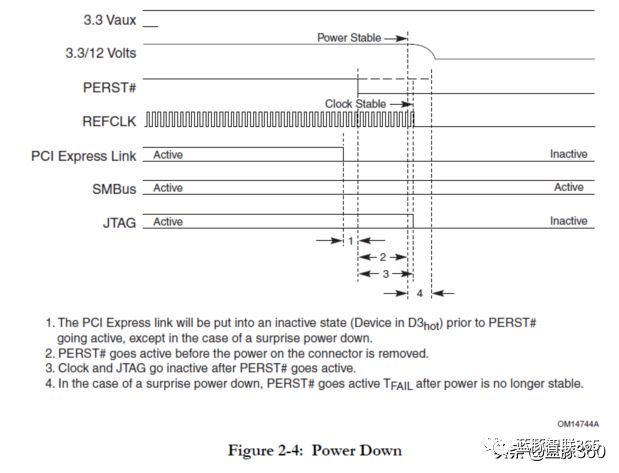

2.2 上电和掉电时序

2.3 复位

PCIe系统复位信号是异步、低电平有效输入信号。系统输入时钟的频率必须是100MHz或250MHz,PCI-Express系统的时钟控制方式有两种:其一就是使用同步实时控制,其中所有器件共用一个时钟源,另一种是使用非同步控制,其中各器件使用自己的时钟源.

2.4 供电

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的最大宽度为×32,但是在实际应用中,×32的链路宽度极少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用PETp015、PETn015和PERp015、PERn015共64根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。

三、应用设计

3.1 通用与PCB要求

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。Vaux 的使用降低功耗和缩短系统恢复时间。

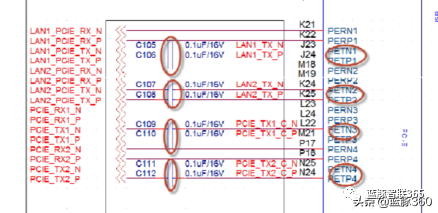

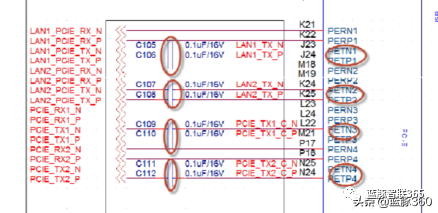

在应用设计时,注意差分线之间的耦合电容(如下图中的C105~C112,0.1uF/16V)要靠近TX端放置。根据PCIe标准,同一个差分对(如TX或RX)中的+(P)与-(N) 可交换使用。注意TX 和RX 差分信号阻抗控制为100 欧姆+-20%,单端阻抗为60欧+-15%。

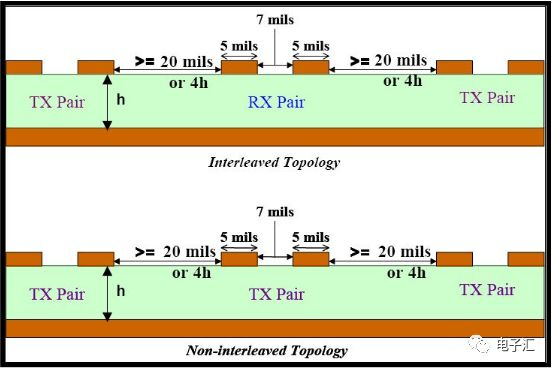

为保证信号质量,要求PCB LAYOUT时保证:

a. 完整的参考平面;

b. 信号间距不小于20mil;

c. 走线尽量走off-angle 线,或者是圆弧线;

d. 在换层的地方添加回流地via;

e. 尽量避免出现stub 的情况;

f. 如果PCI-e 信号线通过金手指进行通信,则金手指下面需要全部掏空;

g. 信号线长度尽量短,关于长度,对于芯片之间,若是MICROTRIP LINE最长15.5英寸,如是STRIPLINE则最长为18英寸;对于芯片与连接器之间,长度限制为12英寸;对于边缘金手指到芯片之间,长度限制为4英寸。

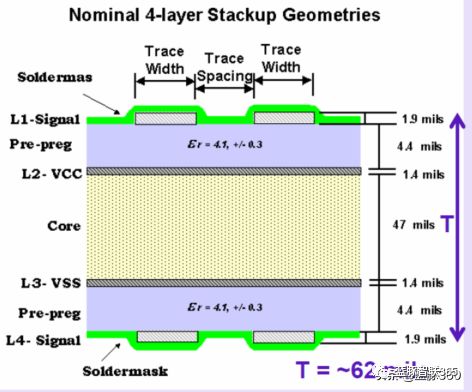

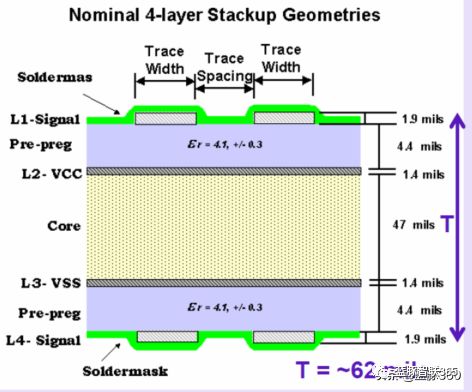

对于PCB Stackup堆叠要求,TX一般放在Top Layer,普通FR-4 4层板也可以,其顺序为S/P/G/S(S为信号,P为电源,G为地)。微带线MICROSTRIP LINE使用0.5 OZ铜厚,STRIPLINE使用1 OZ铜厚。下图为一示例参考。注意:条件允许时,尽量把差分对与对之间的间距拉开以减少串扰。

3.2 时钟要求

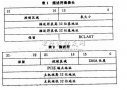

时钟为100MHz,支持SSC。如下图所示。

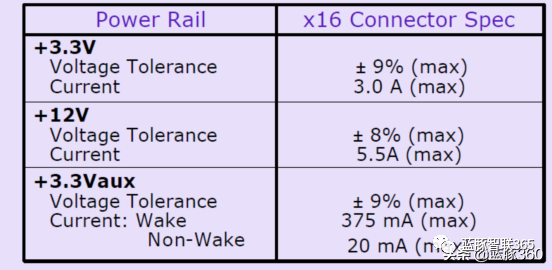

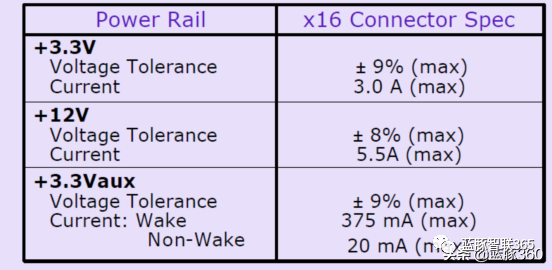

3.3 供电要求

供电如下。

四、测试与验证

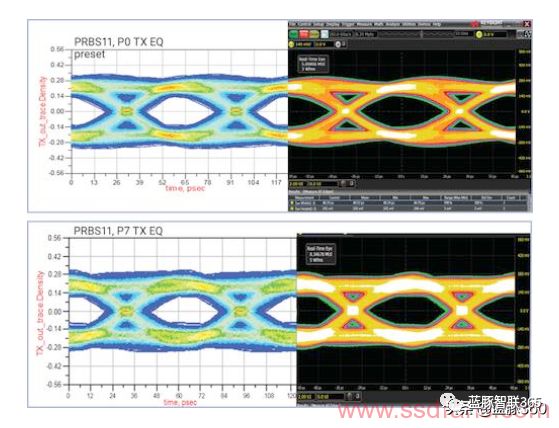

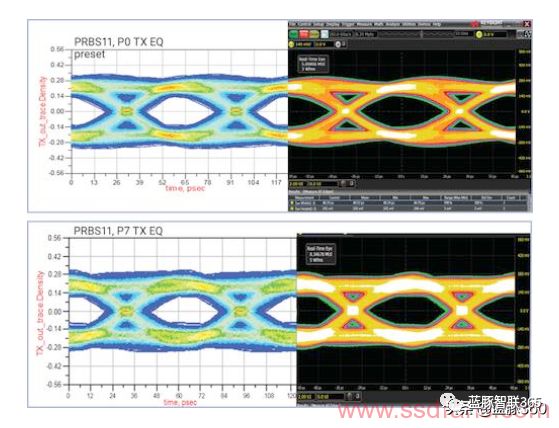

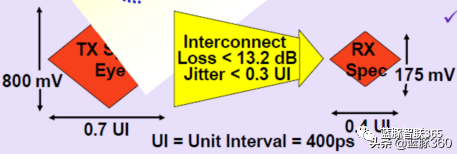

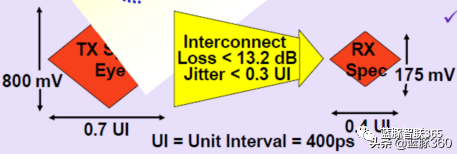

根据PCI-SIG提供的CTS测试要求,要求TX和RX眼图规格大致如下。

测试与验证主要关注信号完整性SI,其中Loss损失和Jitter抖动特别关键。

测试时,必须使用以下辅助控制板才能完成SI的验证:

- Compliance Base Board (CBB) for add-in card measurements

- Compliance Load Board (CLB) for system board measurements

使用实时数字示波器测试眼图,其要求是6GHz模拟带宽analog bandwidth,20G以上的抽样带宽sampling bandwidth,并且此种示波器必须具备眼图eye diagram信号分析的软件工具 SW tool。

探头位置:在测试Tx Signals时,连接到50欧负载上;在测试Rx Signals时,在测试包的输入脚上。

示波器的后处理:

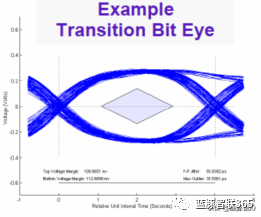

- Create transition bit eye建立过渡比特的眼图

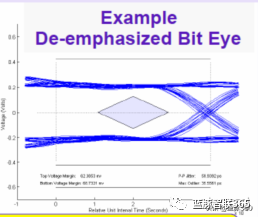

- Create de-emphasized eye建立去加重的眼图

测试的目的是确定以下参数:

- Max jitter 最大抖动

- Min eye voltage margin (high/low)最大眼图电平(高/低)

- Max AC common mode voltage 最大交流共模电压

电子发烧友App

电子发烧友App

评论