`1602LCD在仿真时数据线尽量要接上拉电阻,否则可能不能显示`

2013-08-12 23:53:25

在看数据手册的时候看到I2C Boot Device Configuration中有这么一个选项

10 address 0

2018-06-24 01:28:22

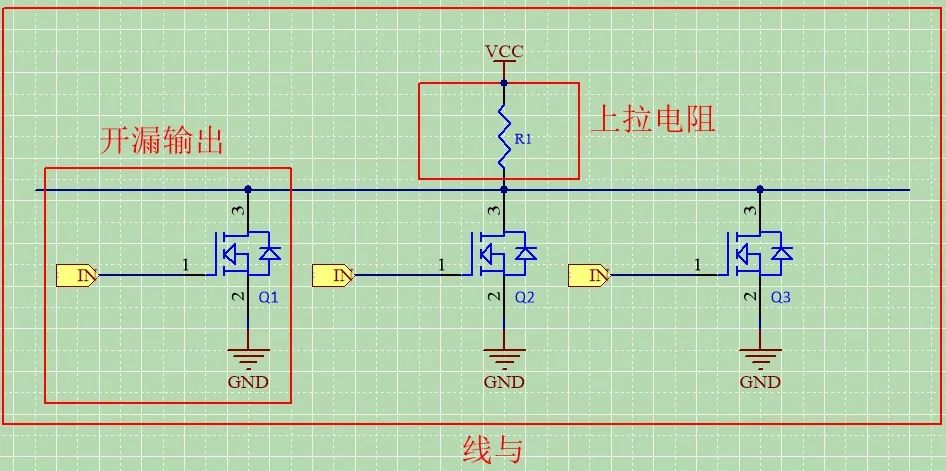

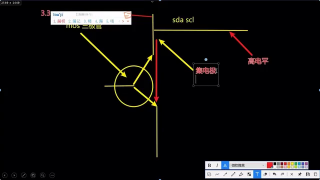

器件都有一个唯一的识别地址,而且都可以作为一个发送器或接收器。当连接在I2C总线上的多个主机器件同时传输数据时,通过仲裁来避免冲突。SDA和SCL都是双向线路,通过一个电流源或上拉电阻连接到电源。器件输出级必须是漏极开路或集电极开路,当总线空闲时,两条线路处于高电平,执行线与的功能。

2019-08-05 06:33:00

I2C总线协议图解1I2C总线物理拓扑结构 I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的控制,来

2019-08-01 16:12:45

我发誓我再也不能忍受了。我就是不能让I2C工作!真是几个月了我不是故意说PIC的坏话,因为我喜欢他们,但AVR和PSOC只是工作。我试过代码配置器,我尝试过互联网上可以尝试的每一段代码。我试着编写我

2019-09-29 07:34:13

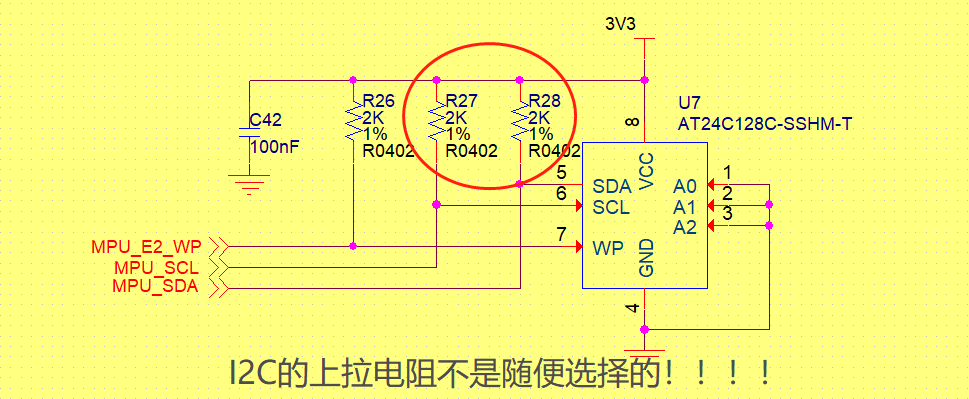

、I2C设计数学:电容和电阻了解I 2 C及其随之而来的一些设计挑战,包括逻辑阈值,影响电容的因素以及最小和最大上拉电阻。本文介绍了哪些变量会影响总线的电容。它还考察了用于确定上拉电阻器尺寸并确定电路

2020-09-22 09:31:41

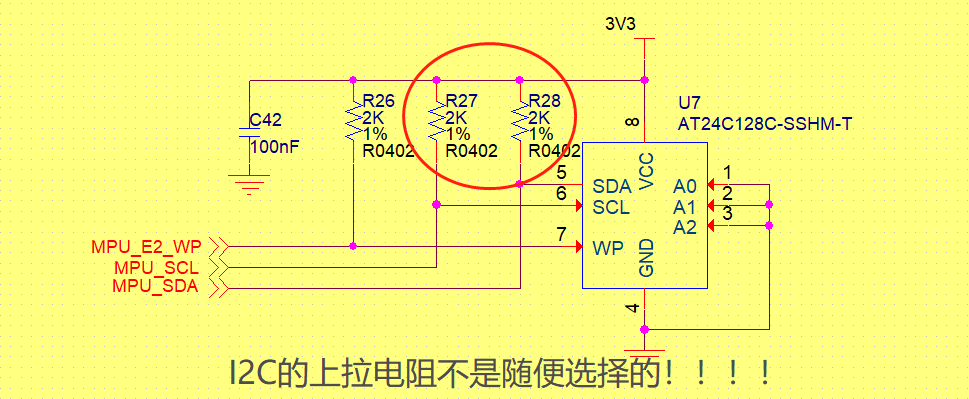

如图,像这种IIC的电路为什么要加这些4.7kΩ、100Ω的上拉电阻?

2019-02-15 09:58:53

文章目录一、I2C简介软件I2C硬件I2C软件I2C和硬件I2C的区别二、使用步骤1.引入库2.读入数据总结一、I2C简介I2C 通讯协议(Inter-Integrated Circuit)是由

2021-08-23 06:22:51

I2C信号一般需要外接上拉电阻,如果主控内部有上拉电阻,是否可以省略外部上拉?这个是否需要上拉根据什么来决定?是根据从器件的输入电流来决定的吗?芯片的输入电流参数(Ii 即input current)怎么理解,设计电路时针对这个参数需要注意什么?

2018-06-07 10:01:00

。I2C的两根线SDA(串行数据线)和SCL(串行时钟线)都是双向I/O线,接口电路为开漏输出,需通过上拉电阻

2022-01-20 08:04:17

在设计时对产品进行静电干扰测试时,出现I2C的CLK被异常拉低,接上位机读取I2C状态寄存器,发现寄存器值有变化,这种问题如何解?

2020-02-07 15:23:49

的情况下工作在I2C链接上,但是当我使用STM8作为从属时它失败了。时钟和数据线在示波器上看起来不错,漂亮和正方形。我比较了32-32和32-8的信号,在32-8中'ACK'脉冲保持高电平而不是拉低

2018-12-18 16:29:08

硬件I2C(中断方式)以STC8F2K08S2单片机为例一、I2C相关的寄存器STC8系列单片机硬件I2C使用教程(一)二、I2C中断相关的寄存器① I2C中断源② I2C中断允许位③ I2C中断

2021-12-02 08:16:27

,I2C上拉电阻最小值确定为什么I2C需要上拉电阻才能通讯呢?因为SDA和SCL是开路漏极或者开路集电极输出,所以如果没有上拉电阻,芯片是无法输出高电平的,可参见图2。图2 I2C硬件框图要理解I2C上拉

2022-11-29 08:00:00

NXP的母公司)在80年代开发,用于主板、嵌入式系统连接周边低速设备。I2C由两条双向开漏线组成,这是一个很大的优势,接线简单。两条线利用上拉电阻将电位上拉。典型电位为+3.3V或+5V。标准传输速率为

2020-08-25 11:16:05

SDA,另外一根时钟线SCL,接上拉电阻,总线空闲为高电平。只要有低电平,总线就会被拉低电平。主机通过I2C总线来传输数据给挂载的器件。通过总线仲裁,来判断哪一台主机来控制。SCL...

2022-01-18 07:36:05

数据线,为OD门,与其它任意数量的OD与OC门成\线与\关系。I2C总线通过上拉电阻接正电源。当总线空闲时,两根线均为高电平(SDL=1;SCL=1)。连到总线上的任一器件输出的低电平,都将使总线的信号变低,即各器件的SDA及SCL都是线“与”关系。二、协议1.空闲状态 I2C总线总线的SDA和SCL

2022-01-19 08:05:15

避免I2C, 如果吞吐量是一个主要关心的问题; SPI支持更高的时钟频率,并使开销最小化。而且,SPI(或UART)的底层硬件设计要简单得多,因此,如果您使用FPGA并从头开始开发串行接口,则应该将I

2020-09-06 10:16:10

在硬件上,I2C 总线是由时钟总线 SCL 和数据总线 SDA 两条线构成,连接到总线上的所有器件的 SCL 都连到一起,所有 SDA 都连到一起。I2C 总线是开漏引脚并联的结构,因此我们外部要

2022-01-07 06:03:45

慢于从高到低的过渡,从而产生经典的I2C“锯齿”波形:这两个示波器捕获显示了具有1kΩ上拉电阻和最小电容(总线上只有两个器件,且PCB走线短)的I2C时钟信号的从低到高和从高到低的跳变。上拉电阻的尺寸

2020-09-20 08:37:42

请教下I2C 的Clock stretching功能吗,比如新唐MCU硬件I2C做主机,外部从机带clock streching功能,如果从机将SCL拉低,主机这时候需要怎么配置。

2023-06-26 08:47:45

的外部收发设备,现在被广泛地使用在系统内多个集成电路(IC)间的通讯。I2C是半双工通信I2C只有两根双向通信线: 一根是时钟线SCL, 一根是数据线SDAI2C总线通过上拉电阻接电源,当总线空闲的时候,两根线均为高电平。各器件之间的SCL与SDA 都是 “线与” 关系二、I2C的时序1、数

2021-08-20 06:58:20

................................................................... 3016.1 标准模式I2C 总线器件电阻Rp 和RS 的最大和最小值

2009-04-09 18:34:35

可以帮助你找到合适的值,但是,如果你确实要优化I²C总线,则可能需要使用示波器测量信号(如果可能,请使用低电容探头)并调整上拉电阻,直到获得所需的时序特性为止。

2020-09-21 09:00:00

这一届爽是真的爽,hal库和cubemx节省一半时间工作量23333终于学到I2C了,单片机的时候就没把I2C学好,现在来恶补,,,这个博主把为什么I2C读、写要先设置0xA1、0xA0讲得很到位

2022-01-11 07:12:02

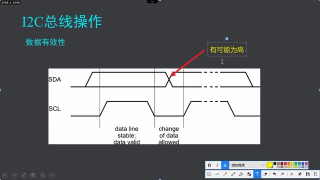

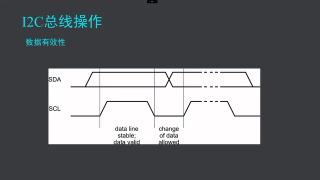

I2C通信协议I2C通信原理I2C通信原理:I2C是一种半双工通信方式,主要时钟线SCL和数据线SDA构成,速率一般为400Mbps总线信号有三种:开始信号;结束信号;应答信号当时钟线SCL和数

2022-02-17 07:16:28

的设备都有一个独立的地址,主机利用地址进行不同设备的访问多个主机同时使用总线时,为防止数据冲突会通过仲裁的方式决定哪个设备占用总线具有三种传输模式:标准模式(100k/s)、快速模式(400k/s)、高速模式(3.4M/s)总线通过上拉电阻接到电源,当I2C设备空闲时输出高阻态,当所有设备都空闲

2022-01-13 07:20:43

我的I2C通信需要被拉到3.3V,但是我不知道我应该使用什么尺寸的上拉电阻。我读过的其他论坛的帖子,建议2.7k欧姆或4.7K欧姆,但这似乎只是让高可以在3.3V和是在3.0V低。这是正常的吗?我用

2019-04-03 15:13:49

一 、I2C物理层I2C 通讯设备之间的常用连接方式见图:有以下特点:(参考数据手册:上拉电阻一般4.7k~10k ,一般4.7k)(1)由两条总线控制:一条双向串行数据线(SDA) ,一条串行

2021-08-03 07:43:57

1.STM32单片机,I/O电阻怎么取值?2.手册上说I/O引脚做为输出的时,单个I/O电流在 16mA,总I/O电流在90mA。3.比如,一些I2C,SPI串口,都会加电阻,100R、1K等。电压

2018-12-21 13:41:02

是FPGA生成的数据信号在约束.ucf文件中,无论我将sda位设置为i2c还是上拉它,都没有变化。在硬件设备中,i2c总线直接连接到FPGA的引脚。根据传感器数据表,SDATA通过1.5kΩ电阻上拉至VDD

2019-07-01 09:15:23

................................................................... 3016.1 标准模式I2C 总线器件电阻Rp 和RS 的最大和最小值

2008-08-13 17:16:42

个8位的数据。器件地址的组成:4(设备ID)+3(可编程地址)+1(读写控制位)总结:i2c通信协议是同步通信,MCU通过器件地址查找要通信的i2c从设备。 i2c通信协议时序:空闲信号、 起始信号

2020-03-06 16:15:03

原理图是这样的我的想法是把所有的i/0口引出来,同时用i/o口链接tft lcd,看这个原理图的话 i/o口引出来,没有接上拉电阻,下面几个i/o口的话接一个vcc是为了提高i/o口的驱动电流吗?,吐过似的话,那引出来的引脚应该也是接了上拉电阻的,对不对?

2019-03-20 21:49:23

)是一种两线式串行总线,可用于微控制器及其外围设备之间的通信。I2C总线由数据线SDA和时钟线SCL构成,可进行数据发送和接收,其通过上拉电阻接电源,当I2C总线空闲时,会输出高组态,此时数据线SDA和时钟线SCL均处于高电平。

2023-04-23 16:04:22

亲爱的大家, 我在我的电路板上使用LSM330DLC陀螺仪,我忘记了SPI / I2C选择引脚上的上拉电阻。但它工作正常。我的问题是我可以在没有这些上拉电阻的情况下开发我的项目吗?在数据表中提

2019-05-16 13:50:24

LTC4311 I2C逻辑缓冲器的典型低压应用电路。利用LTC4311低压I2C / SMBus加速器,利用低功耗总线加速器提高I2C或SMBU数据速率并降低功耗,LTC4311的强上拉电流允许用户选择更大的总线上拉电阻值以降低VOL

2019-06-05 09:06:39

` 谁来阐述一下Lcd1602必须接上拉电阻吗?`

2019-09-23 16:46:11

stc89c52哪些接口需要接上拉电阻?新手求教啊

2013-04-06 22:21:58

最近在用stm32f401re做一款热成像设备需要用到I2C,这里总结一下遇到的坑。一开始调试我用的是开发板飞线接传感器,SCL SDA加4.7k上拉电阻。使用硬件I2C时读写大量数据时经常会遇到

2020-03-05 19:02:15

感觉SPI配置起来要比I2C配置起来要简单多了,I2C还没搞懂!!!!!

2013-03-23 16:12:58

本帖最后由 松山归人 于 2021-6-18 09:29 编辑

作者:黄忠老师(张飞实战电子高级工程师)I2C是一种简单的双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送

2021-06-18 09:27:37

查找从机。因为I2C 通信IO口输出结构都是配置为漏极开路或集电极开路输出。所以时钟线和数据线必须外部都接上拉电阻,当一对多输出的时候,很多GPIO口会连接在同一根线上,可能会存在某个GPIO输出高电平

2021-09-07 14:22:56

一、 I2C总线知识 (1)I2C总线物理拓扑结构 I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低

2017-07-20 22:29:02

要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。 5、关于I2C的上拉电阻:因为I2C

2018-10-19 16:30:19

,考虑到这个项目是带模拟电视芯片的,以前就出现过模拟电视芯片的I2C地址没有去配,导致出现漏电情况,遂立马去看是不是这个问题,结果是遗憾的,配了!那再仔细检查了基带的GPIO口和其他的I2C,发现都配

2011-12-15 18:34:39

接上拉电阻R5是因为芯片IO口开漏输出要求吗?还有没有其他原因?

2016-10-31 21:07:39

隔离可防止系统两个部分之间的直流电和异常的交流电,但仍然支持两个部分之间的信号和电源传输。隔离通常能够阻止电气组件或人员遭受危险电压和电流浪涌的伤害;用于保护人员的隔离称为增强型隔离。I2C已成为许多系统中流行的全球标准;因此,隔离I2C已经扩散到大多数高压市场。

2019-08-01 08:45:04

51单片机中P0口作I/O使用时,为什么要在外部接上拉电阻1、当TTL电路驱动CMOS电路时,如果电路输出的高电平低于CMOS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉

2022-01-14 07:43:57

学习I2C总线通信协议,完成基于I2C硬件协议的AHT20温湿度传感器的数据采集,并将采集的温度-湿度值通过串口输出。具体任务:1)解释什么是“软件I2C”和“硬件I2C”? (阅读野火配套教材的第

2021-08-23 06:19:16

它输出高电平时,它就断路,什么也不输出,由外接电平决定这个引脚的电平)。如果芯片内部带有上拉电阻(比如BBB的芯片就自带上拉电阻),那不外接上拉也可以。BBB系统自带了一个Linux下的I2C工具

2014-10-22 13:52:44

I2C分为哪几种模式?I2C的上拉电阻取值是什么?上拉电阻的上限如何确定呢?关于I2C有什么问题吗?那么一般如何解决呢?

2021-06-27 06:59:35

各位大侠大姐们,下午好!小弟刚接触I2C方面的知识,想用LABVIEW 来编写VI来控制I2C工作,有外围IC(RELAY CARD 之类的)通信的,如何实现,请大侠大姐帮帮忙,如果现成的VI,可以给我一个吗!!!谢谢拉!!!

2012-03-31 13:17:41

89C52的单片机,在实际使用时P0需要外接上拉电阻,那么P1、P2、P3还需要接上拉电阻吗?4组IO口,接不接上拉电阻有什么区别?

2017-06-05 20:51:07

我在设计中使用LSM6DS3组件。我过去曾经使用过这个组件(并且总是喜欢它),但从来没有使用过这个组件。我正在使用I2C与10k上拉电阻进行通信,并且使用与我的微控制器相比的独立电源总线来打开/关闭

2019-03-07 15:42:24

单片机 I2C 时序介绍在硬件上,I2C 总线是由时钟总线 SCL 和数据总线 SDA 两条线构成,连接到总线上的所有器件的 SCL 都连到一起,所有 SDA 都连到一起。I2C 总线是开漏引脚并联

2022-01-07 06:19:47

I2C上拉电阻 在一些PCB的layout中,大家往往会看到在I2C通信的接口处,往往会接入一个4.7K的电阻,有的datasheet上面明确有要求,需要接入,有的则没有要求。 I2C接口 对于

2022-01-14 07:22:21

CYSTART();I2CysCLSSEDRIVEVMODED(I2CYSCLIL DMYRESIUP);/ /使用内部上拉I2C电阻器I2CysSDAsStudioDrimeMod(I2CsSdAydMyRESIUP);因此,问题是如何在4100系列中做到

2019-10-08 07:43:07

想这在其他地方都有介绍,但我还没有找到。

可能最简单的事情是加载一个 I2C 扫描程序,以查看 ESP8266 看到的 OLED 地址。确保 I2C 引脚上有上拉电阻。还要将引脚更改为您的设置。在此

2023-04-26 08:12:24

漏应用来说,时序常数比较大会对I2C总线产生负面影响,从而使其串行数据线(SDA)和串行时钟线(SCL)达到所需的波特率。从数学上讲以下是计算电阻值的方法:Rp(min)为可接受的最小电阻值,由下面

2018-11-30 09:12:02

向来实现这一点:如果我们将管脚配置成输入,那么实际上在管脚输出上会出现高电平的输出,因为我们有定义为上拉电阻器的上拉电阻。根据I2c规范,如果我们想把引脚设置为低输出,我们可以把引脚设置为输出,写0,这是

2019-07-26 14:29:14

大家好,我们用i2c来加速这个配置:*分开VDD和VDDIO(这个连接到CS)。* SDA和SCL安装有10K的外部上拉电阻。* SDO / SA0未连接(应该有内部上拉)。是否有任何上电顺序以确保

2019-03-04 11:37:27

开发板I2C连接到RTC(RX8010)芯片,I2C总线上没有接上拉电阻,LS1012A手册上说它的I2C是open drain输出的,为什么没有上拉电阻? 哪位能帮助解释一下,谢谢

2022-01-05 06:28:48

使用STM32的GPIO模拟I2C总线时序,GPIO设置为开漏模式,SDA和SCK外部必须使用上拉电阻,一般是4.7K。开漏模式的好处是,可以同时读取输入电平,而无需切换输入/输出模式。注意事项:在

2022-02-22 06:48:21

一个上拉电阻接到正电源,因此在不使用的时候扔保持高电平。使用 I2C 总线进行通信的设备驱动这两根线变为低电平,在不使用的时候就让它们保持高电平。每个连到 I2C 的设备都有一个唯一地址,这个设备可以

2018-11-30 11:50:53

使用的从器件。要获得正确的上拉电阻值,请参考器件数据表。多个从器件可以共用一条I2C总线,单个上拉电阻器 I2C软件协议 不论何种应用,每个支持I2C器件都需要遵守针对全部I2C器件所定义的共同

2020-12-14 14:17:25

硬件I2C对应芯片上的I2C外设,有相应I2C驱动电路,其所使用的I2C管脚也是专用的,因而效率要远高于软件模拟的I2C;一般也较为稳定,但是程序较为繁琐。硬件(固件)I2C是直接调用内部寄存器进行

2022-02-22 06:02:46

。但是,I2C总线拓扑要依赖于阻值合适的上拉电阻才能实现稳定可靠的通信。电阻值选择错误不仅会造成电能浪费,还可能导致总线状态和传输过程由于噪声、温度变化、工作电压变化以及器件间的制造差异而出

2012-12-17 11:52:52

请问用TMS320C5515的GPIO口模拟I2C是否需要加上拉电阻?

2018-07-31 07:48:20

换个说法,如何将28335的GPIO设置成开漏输出呢?之前使用硬件I2C接口,工作正常,但是因为I2C外设管脚和另外一个外设管脚重复了,只能将I2C接口转移到其它GPIO上,使用软件模拟。使用软件

2018-10-08 17:10:19

stm32f051的i2c需要外接上拉电阻吗,直接用内部上拉行不行,还有库中的I2C_Init函数中有这么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;为什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥帮帮忙,看看是什么问题。

2019-03-12 07:14:31

请问为什么有时在I2C中将SDA和SCL 上加各加个上拉电阻呢?

2023-05-08 18:01:37

如图,请问这个电路图的以太网phy的差分线为什么要接上拉电阻?R79~R82。因为上拉电阻很小,导致功耗很高。是不是这个电路图有问题?

2017-03-10 19:50:21

stm32普通的I/O接口是否需要接上拉或下拉电阻? 接了会更稳定一些吗?

2019-04-24 01:44:05

请问用TMS320C5515的GPIO口模拟I2C总线需要接外部上拉电阻吗?需要的话阻值为多少比较合适呢?

2019-10-28 09:37:43

I2C为什么要接上拉电阻?因为它是开漏输出。 1 为什么是开漏输出? I2C协议支持多个主设备与多个从设备在一条总线上,如果不用开漏输出,而用推挽输出,会出现主设备之间短路的情况。 所以总线一般会使

2021-06-21 10:30:02 14117

14117 I2C为什么要接上拉电阻?因为它是开漏输出!

2021-06-21 16:34:33 11773

11773

如果上拉阻值过小,VDD灌入端口的电流将较大,功耗会很大,导致端口输出的低电平值增大(I2C协议规定,端口输出低电平的最高允许值为0.4V)。

2023-02-06 10:53:18 769

769 I2C协议支持多个主设备与多个从设备在一条总线上,如果不用开漏输出,而用推挽输出,会出现主设备之间短路的情况。所以总线一般会使用开漏输出。

2023-02-24 09:18:48 1167

1167 相信很多人都清楚,在I2C总线上需要接上拉电阻?但是您针对对I2C上拉电阻足够了解吗?本文带您详细掌握一下I2C的上拉电阻。

2023-07-25 10:37:59 945

945

电子发烧友App

电子发烧友App

评论