现在来讲soc的神经末梢,它们依附在骨架上,受和调控制,并将外部信息分享给核心以及其他成员。它是什么呢?

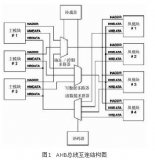

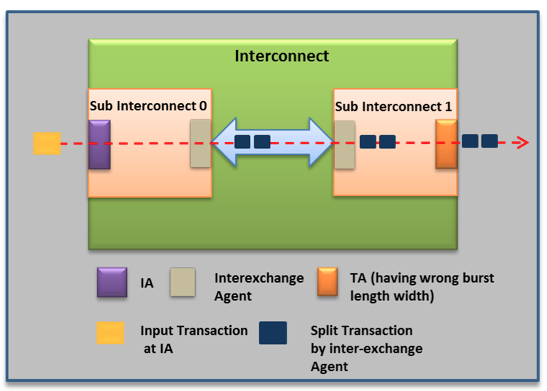

它就是我们所说的标准总线。soc上所有模块想要被核心控制,都需要挂载到crossbar上,以便cpu下配置,以及cpu和dma进行数据传输。我们以最简单的APB总线入手,来进一步了解标准总线的工作原理。

1、APB协议简介

APB(Advanced Peripheral Bus) 作为高级外设总线是AMBA协议之一,也是最基本的总线协议。按照ARM官方定义,APB是一种低成本的接口协议,可以实现低功耗以及精简的接口设计,降低接口设计的复杂度。

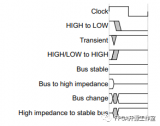

APB协议不支持流水线设计,它主要应用在低带宽设计需求的接口中,高性能带宽需求可以使用AXI总线。APB协议的实现与时钟沿对齐,以简化外设接口的设计。每次传输至少需要消耗两个时钟周期。

在SOC设计中,AHB一般作为IP的配置接口,包括低速IP如I2C,UART,I2S等,也包括DDR,PCIe,Ethernet等高速IP,可以方便的实现CPU对外设IP的寄存器配置。系统中一般会实现一个AXI2APB或者AHB2APB的转换桥将APB口挂载在系统上。

APB的传输信号只与时钟上升沿有关,故其具备以下优点:

·易于实现高频操作;

·性能与时钟占空比无关;

·静态时序分析简单;

·易于与基于上升沿的寄存器访问;

·易于集成到基于周期的仿真器中。

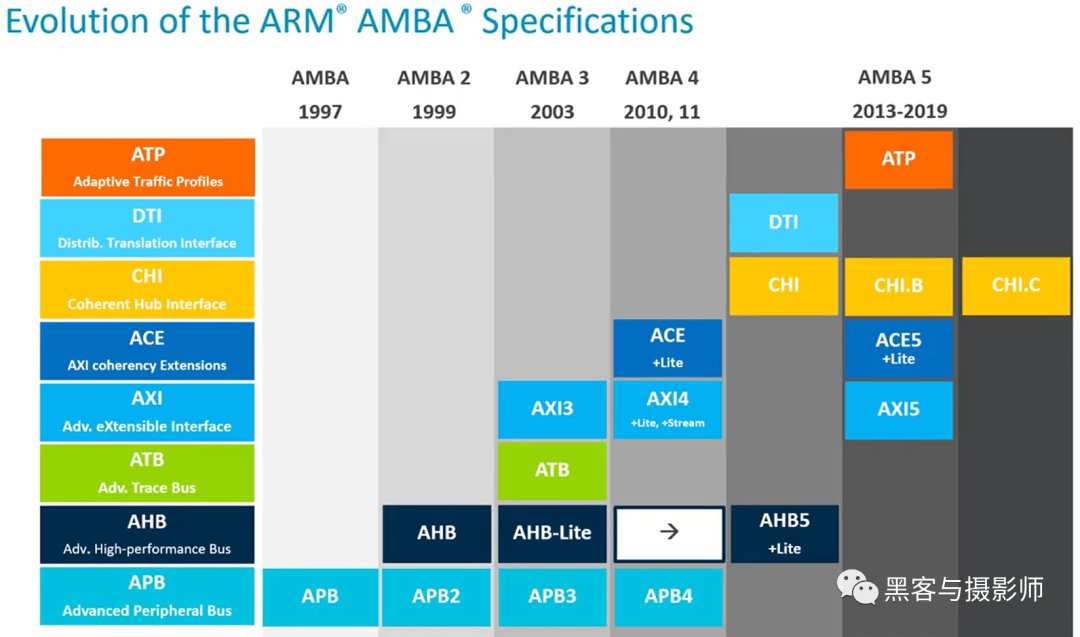

1.1、APB的发展史

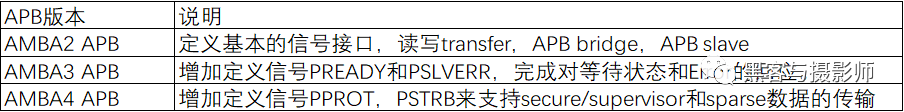

协议已经从APB2.0发展到现在的APB4.0。具体区别如下:

·APB2.0 :该版本协议定义基本的接口信号(具体可见端口信号章节,删除APB3.0有的接口就行);

·APB3.0:增加信号PREADY用以指示slave准备好数据,增加信号PSLAVERR代表传输错误;

·APB4.0:增加信号PROT保护类型,增加信号PSTRB来支持byte级的访问;

2.0和3.0的区别是什么?

APB2.0和APB3.0的差别:APB3.0提供了一个低功耗的接口,并降低了接口的复杂性。且APB3比APB2增加了两个信号:

PREADY:来扩展APB传输,主要是增加延时;

错误信号PSLVERR:来指示传输失败。

3.0和4.0的区别是什么?

·增加了PROT和PRSTB两个信号。

·PPROT一种保护信号,用于支持APB上的非安全交易和安全交易。

·PSTRB一个写选通信号,用于在写数据总线上进行sparse data transfer(稀疏数据传输)。APB4用的比较少。

APB协议向下兼容。

目前soc上最常用的是APB2.0和APB3.0,下面我们主要介绍这两个版本。

2、APB 2.0

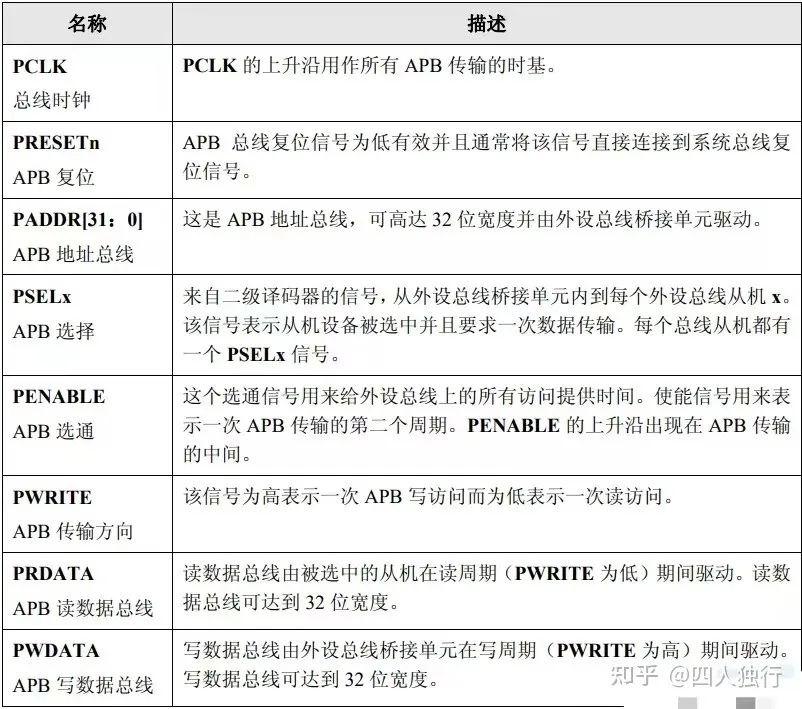

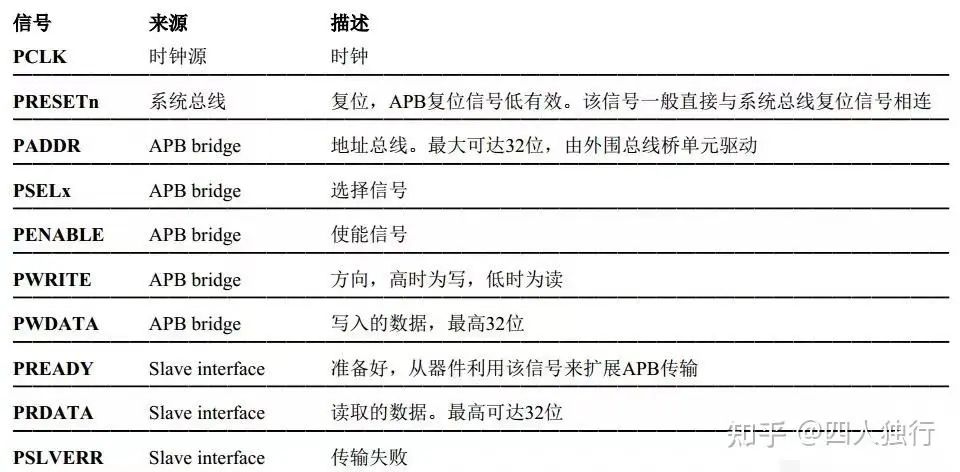

2.1、APB2.0信号列表

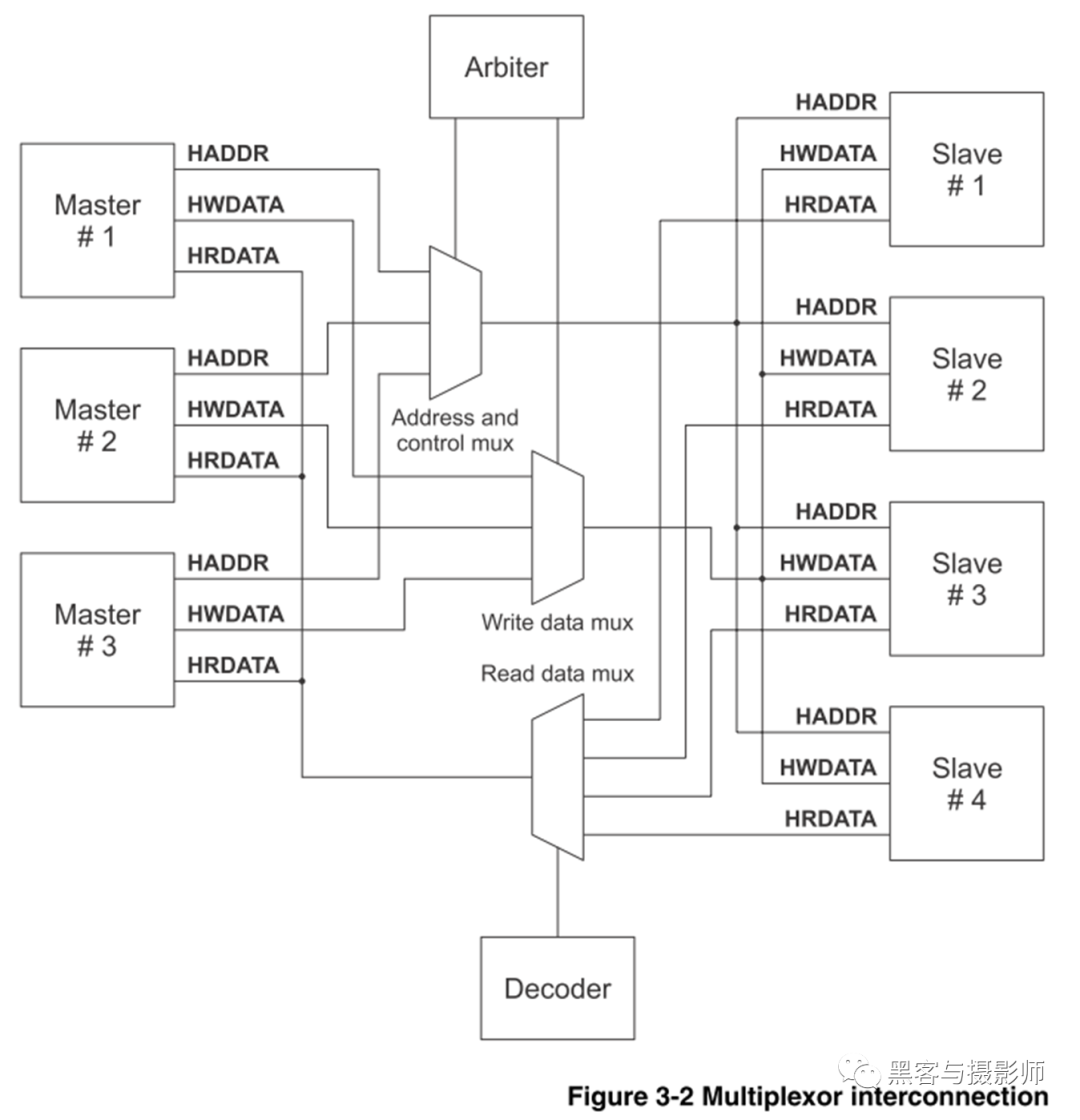

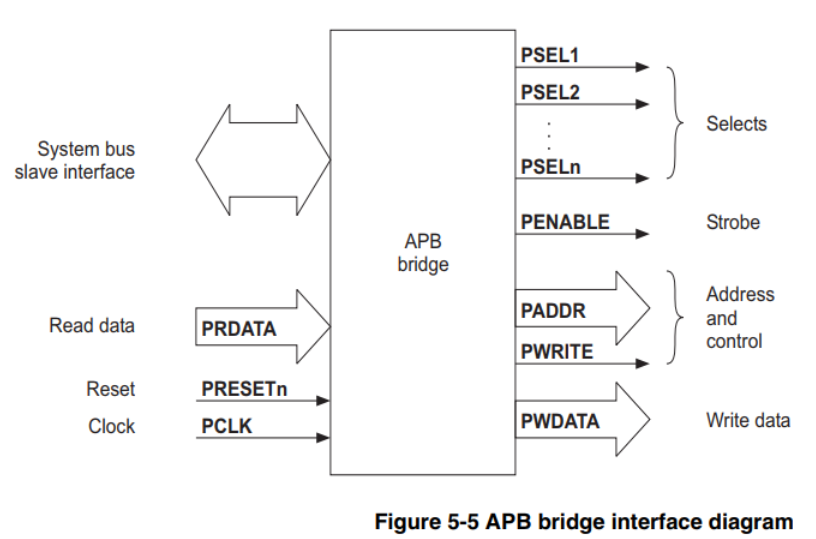

这里需要区分Master和Slave的区别,Master是主机,Slave是从机,一个总机下可以有n个从机,所有的数据传输都是master来控制的,slave来回应。这里需要用到APB 1TO多bridge,APB bif不需要仲裁,只需要对地址的decode,如果地址处于某个slave的域内,就拉高它的PSELn等控制信号,n为slave号。

APB2.0信号

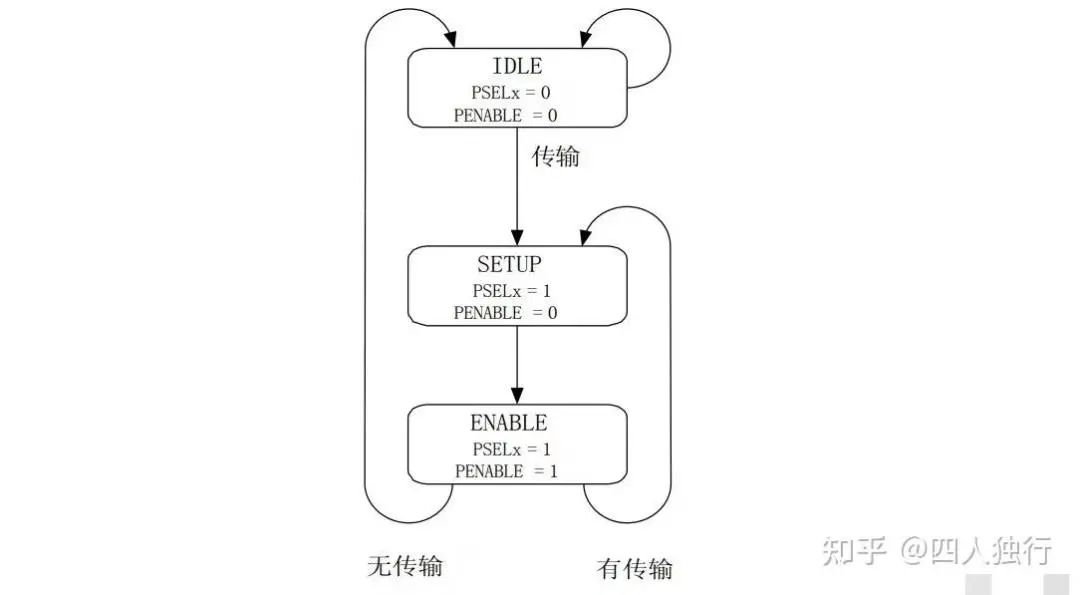

2.2 、状态机

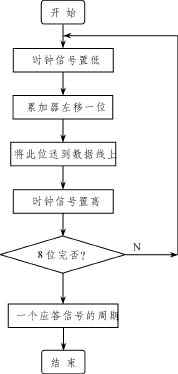

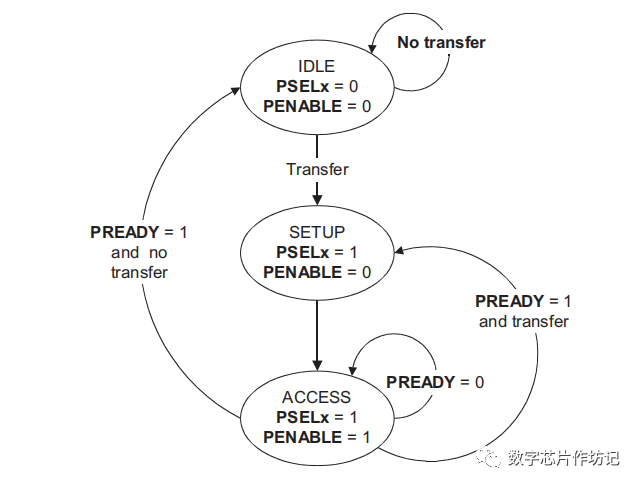

通过PSELx和PENABLE信号的变化,使APB总线处于下面3个状态:

状态机

·IDLE:PSELx和PENABLE都为0,表明master和slave之间无通信请求,因此处在该状态。

·SETUP:当master和某一个slave之间准备进行数据传输时,会进入该状态,这时PSELx=1,PENABLE=0。意思是master选中某一个slave告诉slave我准备要和你交换数据啦,请你准备好!这个状态会保持一个时钟周期然后进入ENABLE状态。这个状态可以直接给wdata。

·ENABLE:这个时候PENABLE拉高,master和某一slave进行数据传输,持续一个时钟周期。这个状态开始等待rdata。

在自己写master时,就按照这个状态输出控制信号就可以了。

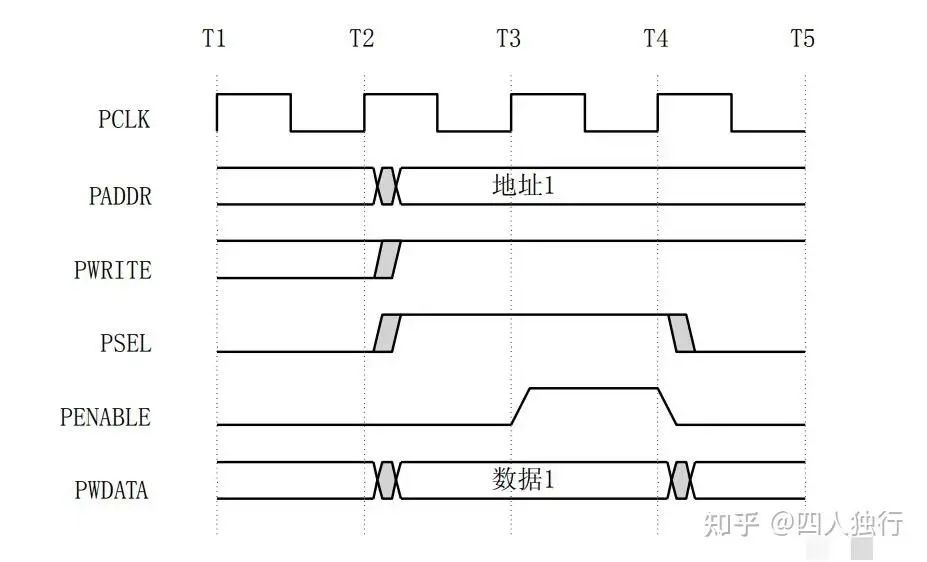

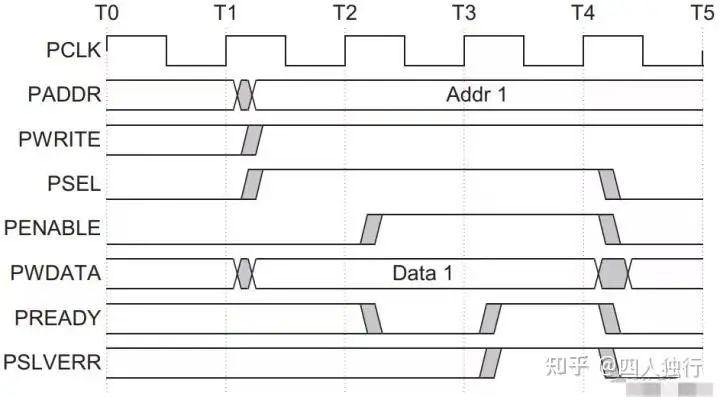

2.3 、写操作

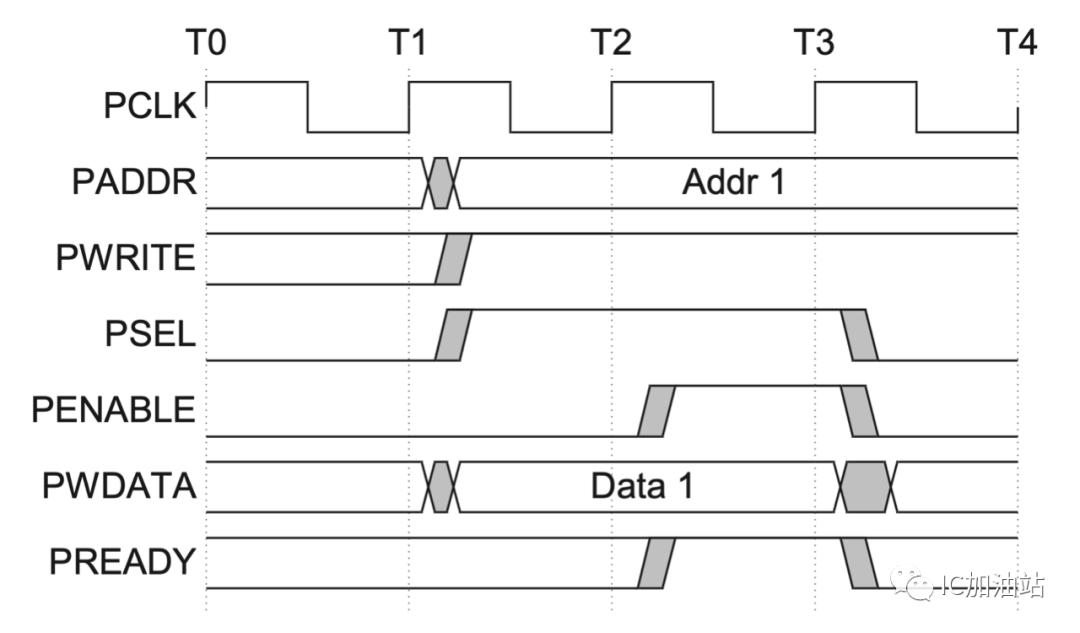

下面就是写传输的时序图:

写时序

·T1~T2:这个阶段master和某一slave无交互数据,因此处于IDLE状态。

·T2:在该时刻,master准备将数据写入某一slave中,因此进入SETUP状态,同时把某一slave的PSEL信号拉高,PWRITE信号拉高,这表示master告诉某一slave:我即将要和你进行数据传输,是我把数据写到你里面,请你准备好!同时改变PADDR和PWDATA信号,这是为了满足下个上升沿的时序。

·T2~T3:保持一个时钟周期。

·T3:此时将PENABLE信号拉高,真正将wdata写到addr。

·T3~T4:保持一个时钟周期。

·T4:数据传输结束,再次回到初始状态。

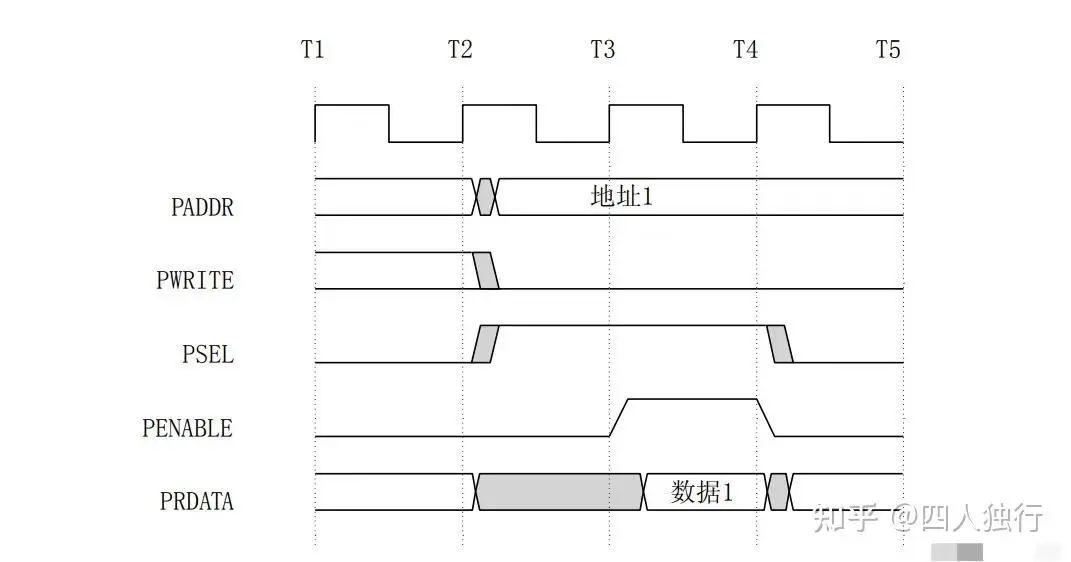

2.4、读操作

读时序

·T1~T2:这个阶段master和某一slave无交互,因此处于IDLE状态

·T2:在该时刻,master准备从某一slave中读取数据,因此进入SETUP状态,同时把某一slave的PSEL信号拉高,PWRITE信号拉低,这表示master告诉某一slave:我即将要和你进行数据传输,是我要读你的数据,请你准备好!同时改变PADDR,这是为了满足下个T4采样沿的时序。

·T2~T3:保持一个时钟周期。

·T3:此时将PENABLE信号拉高,表示master正式把某一slave之中的数据读出来,注意,数据在ENABLE周期末尾的时钟上升沿被采样,也就是T4时刻。

·T3~T4:保持一个时钟周期。

·T4:数据传输结束,再次回到初始状态。

3、APB 3.0

APB 3.0协议是在APB 2.0协议的基础上新加了2个信号,PREADY和PSLVERR组成的;PREADY信号是slave设备用来表示slave是否准备好的信号,PSLVERR是表示slave接收的数据是否有误。

信号表

APB3.0信号

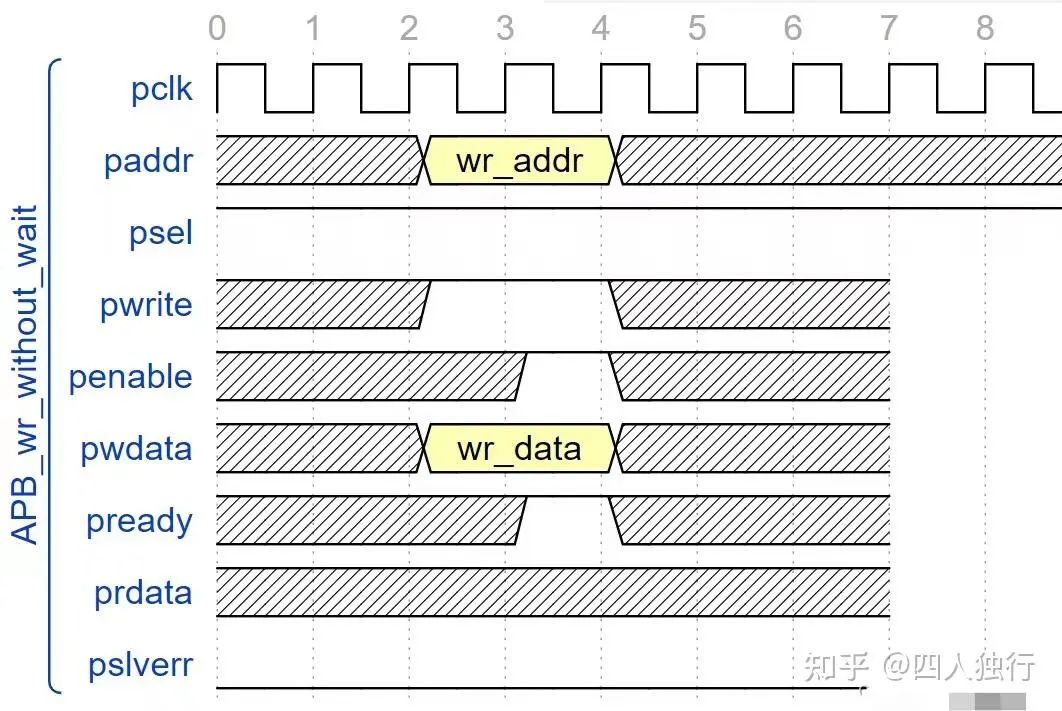

3.1、写操作

写操作,无等待

写无等待时序

该种情况和APB2.0没有任何区别,当PENABLE拉高后,会检查PREADY是否拉高,如果拉高表示slave当前准备好了数据传输,则在上升沿3将数据写给salve。

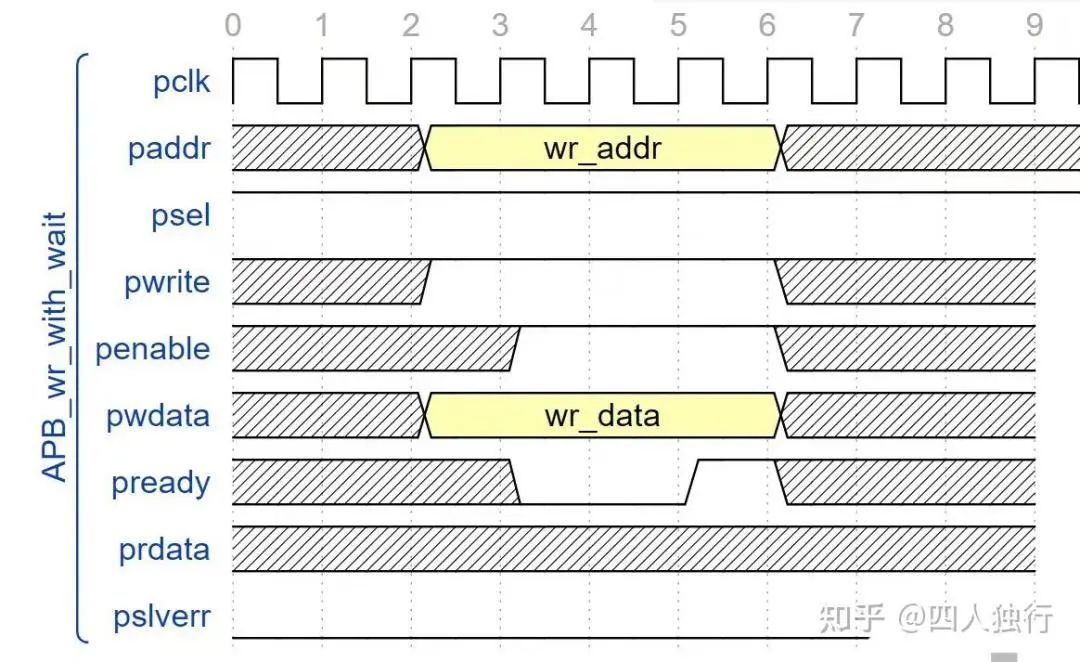

写操作,有等待

写有等待时序

如果PENABLE拉高后,发现PREADY没有拉高,则表示slave还没有准备好数据传输,这时所有信号保持不变直到PREADY拉高,在上升沿5将数据写入。

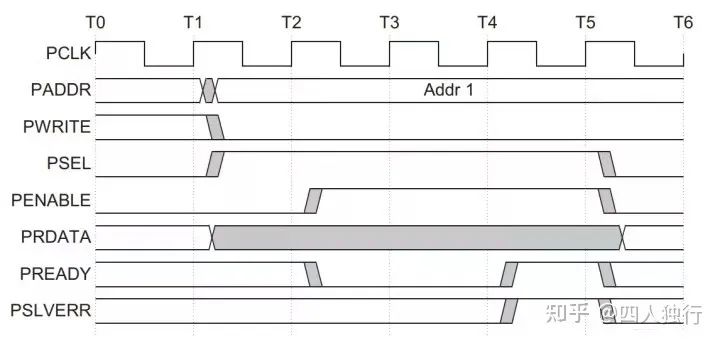

3.2、读操作

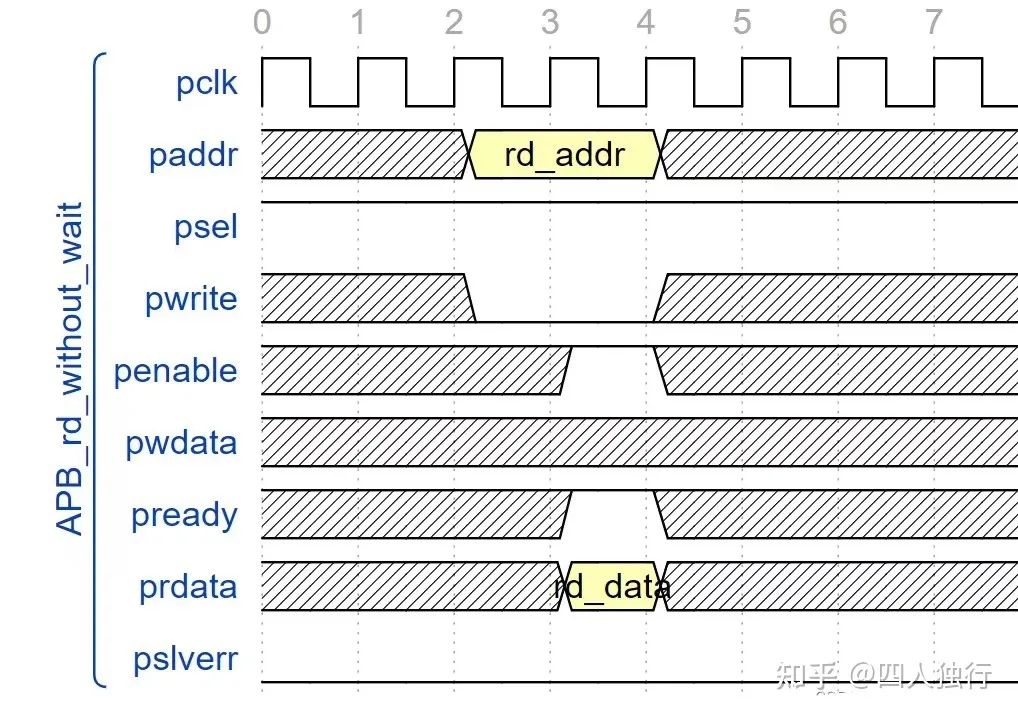

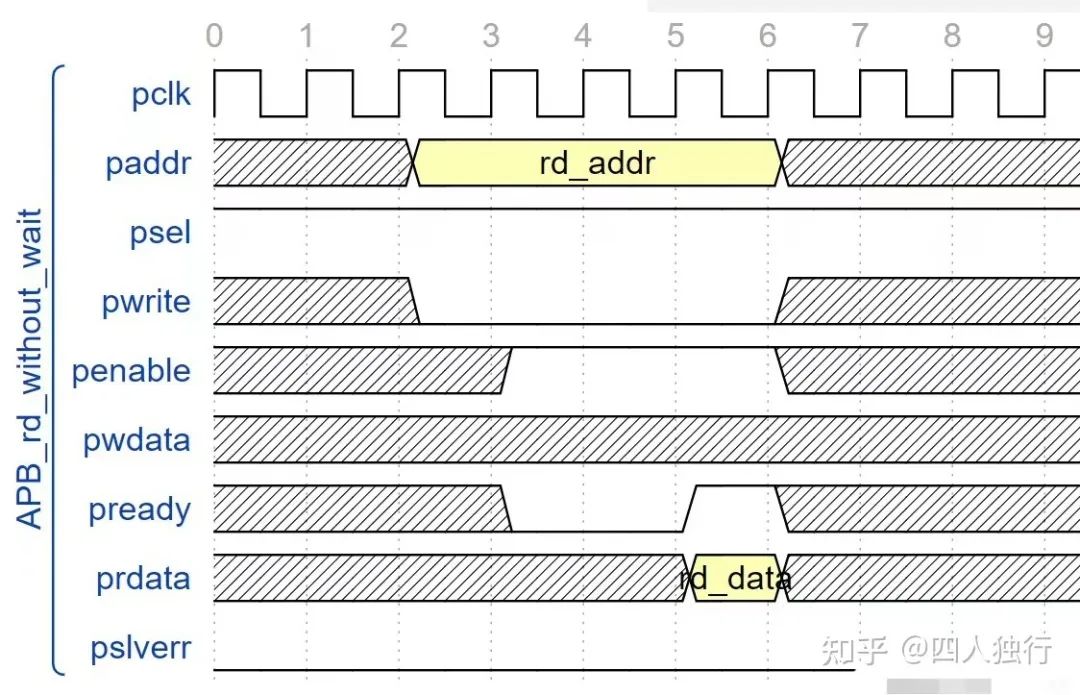

读操作,无等待

读无等待时序

该种情况和APB2.0没有区别,与写操作无等待类似,不再细说

读操作,有等待

读有等待时序

当PENABLE拉高后,发现PREADY信号还没有拉高,表示slave还没有准备好,这时会等待直到PREADY信号拉高,在上升沿6时刻采样数据

3.3、错误反馈

PSLVERR来指示APB传输上的错误情况。读取和写入事务都可能发生错误。当PSEL,PENABLE和PREADY均为高电平时,仅在APB传输的最后一个周期内才认为PSLVERR有效,其他时间不考虑PSLVERR。

写操作

slverr写时序

在前面的有等待的写操作的基础上,添加PSLVERR,也就是在T4时刻采样,发现PSEL,PENABLE和PREADY均为高电平的前提下,PSLVERR为高,说明这次数据传输有错误。软件决定后续行为。

读操作

读slverr时序

在前面的有等待的读操作的基础上,添加PSLVERR,也就是在T5时刻采样,发现PSEL,PENABLE和PREADY均为高电平的前提下,PSLVERR为高,说明这次数据传输有错误。软件决定后续行为。

4、APB应用场景。

APB因为其面积小,接口少,经常用在外设上,为什么呢?

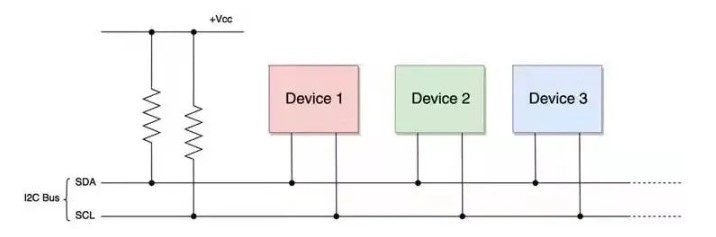

因为soc上外设很多,包括spi,i2c,uart,timer,wdt等,他们对时钟要求不高,如果使用APB接口,可以省面积,降低芯片的复杂度。这也是为什么外设优先的标准接口是APB。

这里主要讲一些APB在SOC上的特殊用法。

·某些IP预留用户控制信号,我们需要用寄存器控制此信号,一般soc每个子系统都会有一个模块专门做这个事情,这是就可以选择APB接口用来配置这些寄存器。

·某些IP,例如SRIO,serdes预留用户配置接口,synosys叫做cr配置口,用于配置或者debug。这时候我们可以自己写一个APB2CR的桥。

·核间通讯模块。通过写寄存器产生中断输出,这时候可以使用APB接口,因为中断发生次数少,无性能要求,可以使用APB,简单。

·APB转sram接口或者APB转fifo。某些模块对外接口是sram,需要我们使用转接桥,根据性能我们选择使用合适的AMBA总线;自研模块数据缓存时,涉及到异步处理,这时候可能用到APB转FIFO的设计。

但是他也有局限,带宽低且不支持pipeline,所以module有这些要求不要使用APB。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论