关键词:嵌入式系统,MPC850,硬件开发平台

1 MPC850简介

Motorola公司的MPC850通信控制器芯片基于PowerPC内核,以精简指令集计算RISC的体系结构为基础,集成了32位微处理器和多种外设接口,具有强大的通信和网络协议处理能力,可广泛应用于各种通信和网络产品,如ADSL modem、SOHO路由器、低速ISDN、T1/E1终端、ATM线卡控制、局端交换、无线接入等。

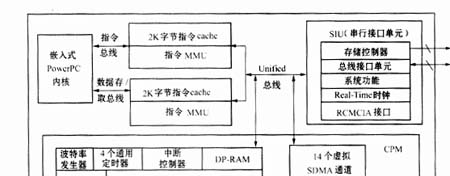

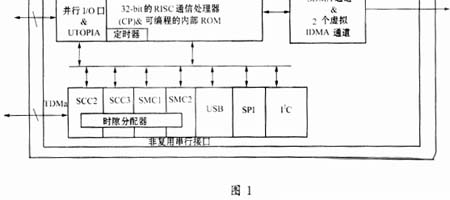

MPC850的功能结构主要包括:嵌入式PowerPC内核,系统接口单元(System InterfaceUnit,SIU)和通信处理器模块(Communications Processor Module,CPM)。其体系结构的框图如图1所示。

从图中可以看出,通信处理器模块CPM支持7个串行信道,包括:2个串行通信控制器SCC,2个串行管理控制器SMC,1个USB接口,1个I2C和1个串行外设接口SPI。因此,MPC850通过灵活的编程方式可实现对Ethernet、USB、T1/E1等的支持,以及对IEEE802.3/Ethern-et、UART(同步/异步)、HDLC、Transparent、App-leTalk、IrDA等多种通信模式/协议的支持。

另外,MPC850还具有增强型在片仿真调试功能,功能齐全的接口单元,可进行优先级编程的中断控制等特征。本系统正是基于MPC850的这些特点来进行通信开发平台的硬件设计的。

2 系统硬件总体设计

设计MPC850多功能通信开发平台的底层,在硬件方面需要提供全面的通信接口、足够的内存容量、调试功能以及测试显示功能。根据设计,本系统主要由CPU、存储器、通信接口、调试以及测试显示等几部分组成。

CPU部分的设计包括了系统的硬件启动与复位、MPC850总线信号分配与定义等。存储器部分包括SDRAM、FLASH ROM和E2PROM。通信接口部分提供了2个Ethernet接口、2个RS232接口、1个RS485接口、1个USB接口、ISDN用户开发板接口以及ATM UTOPIA接口。另外,还提供了MPC850 BDM调试口以及测试口、LED显示等。

3 系统的硬件启动与复位

MPC850的复位方式包括:上电复位、外部/内部Hard Reset、外部/内部Soft Reset、调试口的Hard Reset等。这些方式都由Reset控制器处理。本系统采用了上电复位和外部Hard Reset的方式。

上电复位的过程由芯片内部完成,MPC850需要确认

MPC850在从数据总线上采样硬件复位配置字信息的过程中,

4 存储器设计

MPC850中存储器管理器负责控制管理GPCM和UPMs两种存储器控制机制,针对不同的存储器提供灵活的时序支持和无缝连接。其中,GPCM提供了一种简单的、不支持突发方式的低层次的存储器资源和内存映射接口,因此,GPCM控制的内存槽主要用于系统的启动和不支持突发方式的数据存取。而UPM方式支持突发方式,同时包括外部总线的地址复用、周期定时以及DRAM器件可编程的行列地址选通信号的产生,因此,UPM多用于支持高性能的实时存储器。

在本系统的存储器设计中,采用了1片Intel公司的FLASH ROM 28F320J5,2片SAMSUNG公司的SDRAM K4S281632B。其中,BANK0用于FLASH ROM,对应于

FLASH ROM的容量设计为32Mbit,用来存放实时操作系统和用户应用程序。对BYTE#(ByteEnable)管脚的设置,可以使28F320J5工作在×8或×16模式。

SDRAM的读写以及突发模式的时序控制通过对MPC850

MPC850

5 各种通信接口的硬件设计

CPM通过以下途径减少core的计算任务,包括:减少中断产生率;执行一些OSI第2层处理;支持多缓存存储器数据结构等。

在CPM功能基础上,外围通信电路只需提供物理层收发器和驱动器。在本系统的设计中,Ethernet收发器采用Intel Level One公司的LXT905,RS232与RS485收发器分别采用MAXIM公司的MAX232与MAX488,USB收发器采用Philips公司的PDIUSBP11A。其中,2个Ethernet收发器分别使用与MPC850的SCC2、SCC3两个串行通信控制器接口,2个RS232收发器分别使用与MPC850的SMC1、SMC2两个串行管理控制器接口,RS485复用了SMC2接口,USB收发器使用与MPC850的USB接口。

由于LXT905本身提供了与MPC850的无缝接口能力,于是通过RJ45实现与外界的通信主要集中在协议的实现和数据收发的控制上。其数据接口信号包括:

·RCLK与TCLK:接收与发送时钟信号。由LXT905提供,连接到MPC850的时钟信号CLKx。

·RXD与TXD:接收与发送数据信号。由MPC850提供,连接到LXT905的RXD与TXD。

·TEN:发送使能信号,同时启动LXT905看门狗定时器。

·CD:载波监听信号,监听LAN是否正在使用。

·COL:冲突监测信号,驱动控制器的冲突监测输入。

本系统设计的ISDN端口总线使用了MPC850串行接口TDMa和SPI接口,用户可以在此基础上设计开发自己的ISDN接入系统。其中,SPI接口提供了SPII/O数据信号SPIMOSI与SPIMISO、SPI时钟信号SPICLK、SPI从设备选择信号;TDMa接口提供的信号包括收发数据、时钟、同步等。

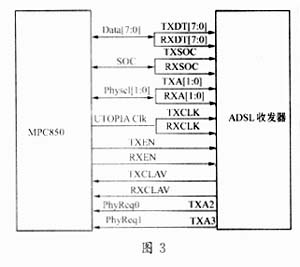

MPC850的ATM控制器支持两种接口模式:UTOPIA接口和串行ATM接口。本系统以支持ADSL收发器为目的,采用了目前ADSL收发器通常使用的ATM UTOPIA LEVEL1/LEVEL2接口。这种接口允许不同速率和性能的传输媒质以一种统一的物理层接口到ATM子系统中,并且有利于向支持多用户的ADSL局端设备扩展。

一个UTOPIA接口包括收发数据端口、控制信号和地址信号。UTOPIALEVEL1和LEVEL2主要在地址信号的定义上有所不同。其中LEVEL1未定义地址信号,主要针对single-PHY的情况;LEVEL2针对multi-PHY的情况,比LEVEL1多了两组地址信号。MPC850的UTOPIA接口支持LEVEL 1标准,加上外部控制逻辑即可实现LEVEL2的multi-PHY接口(最多支持4个物理层设备),因此,本系统的设计实现了兼容UTOPIALEVEL1/LEVEL2的接口电路,如图3所示。关于调试与测试部分的叙述这里从略。

MPC850的多功能通信开发平台在底层设计的基础上,选择相应的嵌入式操作系统,再进行相关驱动程序和上层应用程序的开发,通过所需接口与用户各自的开发系统相连,最终可设计实现各种通信与网络产品。

参考文献

2 Wayne Wolf.嵌入式计算机系统设计原理.北京:机械工业出版社,2002,2

电子发烧友App

电子发烧友App

评论