AMCCS5933 在PCI板卡设计中的应用

PCI总线是计算机主机中最常见的总线。它是一种高性能的32/64位地址数据复用总线,支持猝发传输,传输峰值速率可达528MB/s,而且还支持自动配置。由于PCI总线协议的复杂性,其接口电路实现起来并不容易。但采用通用PCI接口芯片却能达到事半功倍的效果。PCI通用接口芯片对于PCI协议的良好支持及其提供给板卡设计者的良好接口都大大减小了PCI板卡设计者的工作量。现有的PCI接口芯片主要有AMCC公司的 AMCCS59XX系列和PLXTECH公司的PLX系列。本文将对AMCC公司的AMCCS5933芯片的原理及其在PCI板卡设计中的应用进行介绍。

1 工作原理

AMCCS5933的原理框图如图1所示。由图1可知AMCCS5933起到的是一个桥路的作用,即它是PCI总线与本地总线之间的一个桥路。

AMCCS5933既可以作PCI从设备,又可以作PCI主控设备。PCI配置空间可以通过一EEPROM来配置。AMCCS5933为设计者提供了三种数据传输方式:PASS THRU方式、FIFO方式和MAILBOX方式。通过驱动程序对总线控制寄存器设置来控制总线操作和数据的传输。总线控制寄存器有两组:PCI总线控制寄存器和本地总线控制寄存器,分别用来控制PCI总线和本地总线的操作。

2 AMCCS5933 引脚

AMCCS5933引脚图如图2所示。

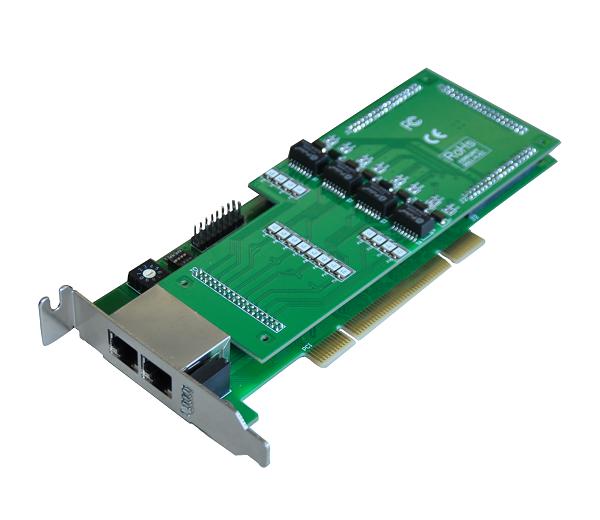

3 AMCCS5933在PCI板卡设计中的应用

3.1 配置空间

每一个PCI设备都要有相应的配置空间,AMCCS5933通过EEPROM来设置配置空间,AMCC公司提供一个NVBUILDER的软件,可以通过AMCCS5933对EEPROM进行读写。EEPROM可以为串行,也可以为8位并行。设计者只需使用NVBUILD就可以完成PCI配置空间的设置。

3.2 总线控制寄存器的访问

PCI总线控制寄存器只有主机才能访问,主机通过PCI总线进行I/O读写操作来访问这些寄存器。

本地总线控制寄存器只有本地逻辑才能访问,与其有关的引脚有ADR[6..2]、BE[3..0]#、SELECT#、WR#、RD#和数据地址总线DQ[31..0]。

读时序如图3所示,写时序将图中RD#替换为WR#即可。

ADR[6..2]提供被访问寄存器的地址,BE[3..0]#制定访问是双字中的哪些字节,WR#为写使能,RD#为读使能,SELECT#为操作使能,都为低电平有效。

3.3 MAILBOX方式的使用

AMCCS5933内部有8个MAILBOX:4个输出MAILBOX,四个输入MAILBOX。PCI方的输入MAILBOX对应于本地的输出MAILBOX,输出MAILBOX则对应于输入MAILBOX。

MAILBOX主要用于主机方与本地逻辑之间的通信,例如传输一些自定义的控制字、状态信息等。

主机对MAILBOX的访问通过I/O读写来完成,本地逻辑对MAILBOX的访问则通过访问本地控制寄存器的方式来完成。

MIALBOX的空满状态由控制寄存器MBEF(PCI)和AMBEF(本地)来表征。

3.4 FIFO方式下的数据传输

3.4.1基本数据传输

AMCCS5933内部有两个单向FIFO:输出FIFO和输入FIFO,主机和本地逻辑可以以访问控制寄存器的方式来访问FIFO,也可以通过WRFIFO#、RDFIFO#、WFULL、RDEMPTY、BPCLK这几个引脚来直接读写FIFO。在设计当中一般采用后一种方法。直接读写FIFO有两种工作方式:同步方式和异步方式。在同步方式下,WRFIFO#、RDFIFO#为FIFO读写使能信号,在BPCLK的上跳沿写入和读出数据,输出引脚BPCLK输出33MHz信号。在异步方式下,WRFIFO#、RDFIFO#为FIFO读写信号。WRFULL为输出FIFO满信号,RDEMPTY为输入FIFO空信号。

3.4.2 DMA的实现

在FIFO方式下可以实现DMA传输。

DMA传输的实现步骤:

(1)通过NVBUILD软件设置DMA传输的控制方为主机或本地逻辑,以下假设为主机控制。

(2)设置有关的PCI总线控制寄存器。

MWAR DMA写地址寄存器 填入接收数据存放的起始地址

MWTC DMA写计数器 填入接收数据的字节数

MRAR DMA 读地址寄存器 填入发送数据起始地址

MRTC DMA 读计数器 填入发送数据的字节数

(3) 启动DMA传输

通过设置MCSR寄存器启动DMA传输。

由本地逻辑控制的DMA传输步骤,只需将控制方式改为本地逻辑控制,然后由本地逻辑来设置相应的寄存器。

3.5 PASS THRU方式下的数据传输

配置空间中的基址寄存器为PCI系统资源分配(内存和I/O空间的分配)提供了一种机制,PCI设备在基址寄存器中填入所需资源的类型和大小,基址寄存器的0位为1表示为内存空间,为0则表示为I/O空间,1、2位则指定内存或I/O空间是分配在1M地址以下,还是分配在任意地址空间,3位表示能否预取,4~31位表示所需分配的内存或I/O空间的大小。PCI BIOS启动后读取各个PCI设备配置空间中的基址寄存器,获取每个PCI设备分配所需的资源类型和大小等信息,并且为这些PCI设备分配好所设定的资源,然后再将分配的内存空间或地址空间的基地址回写到PCI设备的各个基址寄存器中。

配置空间中有6个基址寄存器,与PASS THRU方式有关的是基址寄存器1~4,基址寄存器0被指定为AMCCS5933分配I/O资源,基址寄存器6保留不用。

PASS THRU 方式下的数据传输的有关引脚:PTATN#、PTRDY#、PTNUM[1:0]、PTBE[3:0]#、BE[3..0]#、PTADR#、 PTWR、PTBURST#、DQ[31..0]

PTNUM[1:0]表示由哪个基址寄存器所分配的内存空间或I/O空间。

PASS THRU方式下的数据传输主要由AMCCS5933芯片与本地逻辑电路通过上述引脚信号的交互、握手来完成,时序如图4所示。

PASS THRU的握手时序可以通过可编程逻辑以同步状态机的方式实现,用ALTERA的AHDL硬件编程语言可以很容易地实现它。

3.6 中断的设置与产生

AMCCS5933有两个中断引脚:INTA#和IRQ#。INTA#为PCI总线信号用于产生系统PCI中断,IRQ#是本地总线信号用于产生本地逻辑的中断。

MAILBOX的空满变化、DMA读写传送的完成都可以产生中断,中断的使用方法如下:

A PCI设备中断INTA#

(1)在配置空间中断引脚寄存器填入中断引脚,单功能设备选INTA#。

(2)从配置空间矢量寄存器中获取中断矢量。

(3)在PCI总线控制寄存器中,设置产生的条件,如MAILBOX变满产生中断、DMA写完成产生中断等。

(4)在中断处理程序中,读取PCI总线控制寄存器INTCSR和MBEF当前值,确定中断源并做相应中断处理。

(5)清中断及退出中断处理程序,清中断通过往INTCSR相应的中断标志位写“1”来完成。B 本地设备中断 IRQ#

(1)在本地总线控制寄存器AINT中,设置产生的条件,如MAILBOX变满产生中断 、DMA写完成产生中断等。

(2)在本地中断处理程序中,读取本地总线控制寄存器AINT和AMBEF当前值,确定中断源并做相应中断处理。

(3)清中断并退出中断处理程序,清中断通过往AINT相应的中断标志位写“1”来完成。

4 PCB 板绘制要点

(1)推荐采用四层板。

(3)AMCCS5933 PCI数据线与插口距离小于1.5英寸。

(4)AMCCS5933 PCI时钟线与插口距离等于(2.5+或-0.1)英寸,且只能在PCB的同一层。

(5)AMCCS5933 其他PCI引脚与插口距离小于2英寸。

电子发烧友App

电子发烧友App

评论