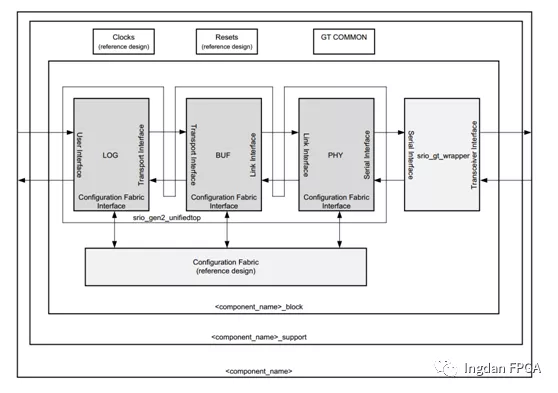

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 855

855

名为XMM8060,两款5G基带芯片将用于2019年上半年问市的5G智能手机。 在5G标准冻结后,华为率先在巴塞罗那世界移动通信大会(MWC)发布首款5G商用芯片--巴龙5G01(Balong 5G01),成为全球第三家发布5G商用基带芯片厂.

2018-02-27 07:06:46 2642

2642 6657的SRIO设计要注意哪些?

2016-10-10 23:18:10

Keystone_SRIO_Init(&srio_cfg);之后,接收即终止了,之后也没办法继续接收FPGA传输的数据。而此时DSP可以正常向FPGA传输数据。

不知道是不是因为没有添加

2018-06-21 13:16:48

; FPGA

1、STK中的external line loopback工作方式好像满足我的需求,但似乎前提是连接双方必须在SRIO协议基础上建立物理层的连接才可以进行测试。由于FPGA端

2018-06-21 06:25:29

各位大佬,你们好。我现在使用TI官方的6678 bootloader源码,改造后实现以下功能:1.通过以太网加载程序;2.能够boot成功;3.以太网功能正常。但是我遇到一个比较棘手的问题,就是当

2021-09-23 09:16:48

各位专家好!请问:我现在想通过6678的SRIO接收来自FPGA的数据,DSP作为从属。用的是论坛给的KI_STK_V1.1的SRIO例程,在test between 2 DSPs的程序段里修改

2019-01-11 07:33:39

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

参考Ti给的例程,发现SRIO中断是直接配置寄存器,然后再SRIO_vector.asm文件中完成中断服务函数入口的映射,而主机PC和DSP的交互是通过利用CSL库函数来完成中断配置,我想问一下:两种中断配置方式能同时写在同一个函数里面吗?

谢谢!

2018-06-21 08:43:37

的,uicompletioncode是LSU_STAT中的。这句程序是函数Keystone_SRIO_wait_LSU_completion的。谢谢。。。

2018-06-21 06:46:55

C6678和C6455使用SRIO通信,1x4p模式,3.125G,其中C6678使用TI的PDK中SRIO LLD

发现C6455发送过快时候C6678的接收缓存不够,触发StarvationQ

2018-06-21 09:01:47

专家好: 调试接口时经常会出现重新load程序的情况,发现如果SRIO双方已经进行数据通信,重新加载程序进行SRIO初始化后,srio链路不通了,需要重新断电重连,这样调试起来比较浪费时间,请问有什么好的方法,可以节省调试时间

2019-01-07 11:15:23

现在,我在ISE13.1软件中使用srio_v5_6 Ip内核。我使用CORE生成器为X6VLX240T-1156-1设备生成一个srio_v5_6 IP内核。然后我用ISE13.1软件打开

2018-10-08 11:10:47

1.我使用的是c6670的例子工程SRIO_LoopbackDioIsrexampleproject,在evm板子上跑了一下,从运行完毕打印出来的log中发现只有核0执行了dio,而核1没有运行

2018-06-21 14:01:07

请教SRIO通信问题,6672和FPGA的SRIO通信,2个lane连接,现象如下:

(1)两端都配置成2x,3.125G,FPGA显示port initial成功,link initial失败。

(2)把6672配置成2个1x,FPGA显示初始化成功,但无法进行数据通信。

请教是什么问题,谢谢。

2018-06-21 13:52:27

请问,6678SRIO自带的loopback例程怎么把内循环改为外循环?除了要把loopback模式设为normal模式外还要怎么改?

2018-06-21 17:47:11

1、SRIO门铃中断的相关寄存器DOORBELL[0-3]_ICSR/ICCR/ICRR,其中的0-3是不是与port对应?

2、通过ICRR配置doorbell到INTDST的映射时,发现

2018-06-21 02:35:54

径:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相关函数定义和功能链接速率配置

2020-09-23 11:08:36

径:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相关函数定义和功能链接速率配置

2020-09-08 10:36:41

我们有一块带有 MPC8640D PowerPC 架构处理器的定制板。一个 sRIO 开关连接到这个处理器。在加载我们的自定义 Linux 映像时,我们无法初始化 sRIO,并且出现分段错误。 附上日志文件供您参考。请找到突出显示的 sRIO init 失败部分请帮我解决这个问题

2023-04-18 07:00:39

保存在资料盘中的Demo\\DSP\\XQ_SRIO_x4LANE_5Gbps文件夹下。1.1.2功能简介实现DSP与ZYNQ之间SRIO接口传输功能。DSP与ZYNQ之间SRIO通道宽度为4,每个

2023-02-21 14:51:50

在资料盘中的Demo\DSP\XQ_SRIO_x4LANE_5Gbps文件夹下。1.1.2 功能简介实现DSP与ZYNQ之间SRIO接口传输功能。DSP与ZYNQ之间SRIO通道宽度为4,每个SRIO

2023-02-02 21:43:20

我想把c6455 srio配置为1P4X的模式,是不是这种模式下只使用一个port,那么我在设置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的时候,只使能

2019-01-21 15:42:20

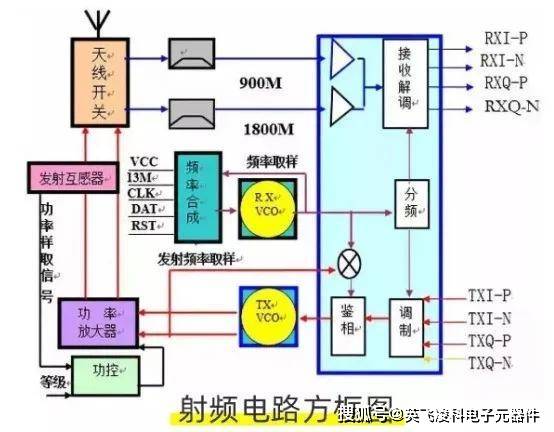

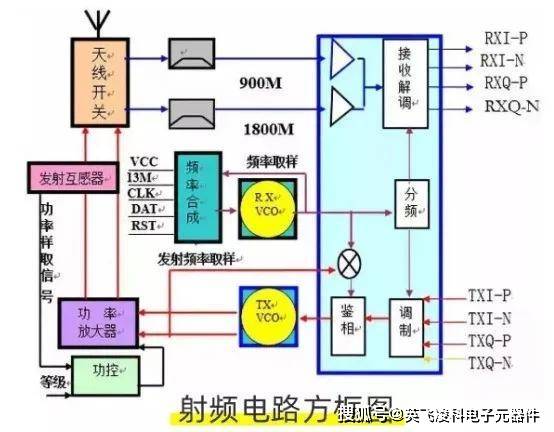

的系带信号,或对接收到的系带信号进行解码.发射时,将音频信号编译成基带码,发射基带码;接收时,将收到的基带码进行解码,转换为音频信号,即电话通话功能.同时也负责地址信息(手机号,网站地址),文字信息(短信,网站文字),图片信息的编解...

2021-07-28 06:42:24

您好,我对“基带”的定义有一些疑问。我现在通过从设计指南中选择设计,在ADS2011中使用负载牵引仿真。在一个音调和两个音源/负载牵引仿真中,参数“Z_Src_Baseband”或

2019-08-06 14:46:43

物理层标准IEEE 802.11a为实例,研究如何在FPGA上实现一个OFDM通信系统的基带收发机。《基于XILINX FPGA的OFDM通信系统基带设计》在系统地给出了收发机模块划分的基础上,对每个

2012-11-02 11:09:37

电路功能与优势该电路是灵活的频率捷变中频至基带接收机。中频和基带上的可变增益用于调整信号电平。 ADRF6510 基带ADC驱动器还包括可编程低通滤波器,可消除通道外阻塞和噪声。 此滤波器的带宽

2019-07-05 07:27:55

Spartan6 SRIO,clk pad是浮动的,有没有办法使用SRIO

2019-08-01 08:59:05

挑战。这些收发器可为模拟RF信号链提供数字接口,允许轻松集成到ASIC或FPGA,进行基带处理。基带处理器(BBP)允许在终端应用和收发器设备之间的数字域中处理用户数据。

2019-09-19 06:20:59

你好,我想请教一个问题,就是我用6474 SRIO,每次发送完一个4Kbyte包后,我需要SRIO响应一个中断。而不是像例程这样:/* Wait for the completion

2018-06-21 14:20:09

您好!

两块6678DSP通过SRIO建立连接,对于SRIO来说:

1.这两块DSP的地址是怎样映射的?

2.映射是怎样建立的?

3. 双方的设备ID有没有参与到映射中来?

4.选择的输出端口号决定了什么?

2018-06-21 09:37:38

目前在调试多片6678与fpga通过cps1848交换芯片通信,使用的是论坛中keystone_srio例程调试过程中有几个问题。1.dap向dpga发数时而成功时而失败,失败时查看error

2019-06-04 11:03:34

现在使用的是官方提供的:K1_STK_v1.1下SRIO驱动,用于测试SRIO通信。对原代码SRIO_Loopback_Mode loopback_mode= SRIO_NO_LOOPBACK;流程

2018-08-03 06:19:00

你好!我现在尝试实现FPGA通过SRIO接口向DSP TMS320C6670发送数据,代码基于CCS5.0下的SRIO_Loopbacktestproject,但发现在sriodevice_init

2018-08-06 06:38:43

基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机。

2021-05-24 07:00:30

建立标准模板的目的是什么呢?单片机标准模板建立的操作步骤有哪些?

2022-01-21 07:50:42

如何建立一个基于STM32标准库的工程模板?

2021-11-26 06:28:02

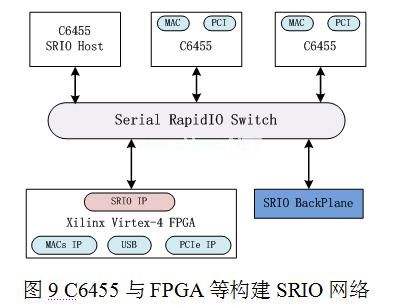

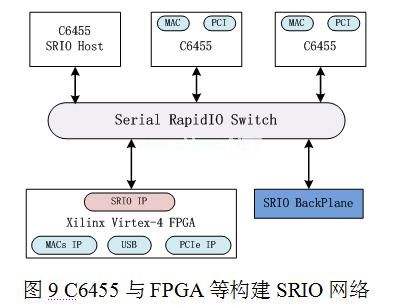

C6455特性是什么?SRIO标准有哪些?如何去实现C6455间的SRIO通信?

2021-06-02 07:12:34

您好,我最近在看C6474的SRIO。

目前手头只有TI官方的C6474的SRIO的资料《TMS320C6474 DSP Serial RapidIO (SRIO) User's Guide》。但是发现该文档读不懂。

请问学习SRIO有哪些好的资料?有视频资料或者中文资料吗?非常感谢您的指导

2018-06-21 02:35:00

集成了音频功率放大器。 此外,展讯通信MAX3232EUE+T还为三星GALAXY S III、GALAXY Note和GALAXY Note II提供基带芯片,支持TD-SCDMA 3G标准。以上

2012-11-09 15:43:30

嗨,我正在使用带有AWGN注入的Agilent N5182A MXG信号发生器,由matlab通过lan连接控制。我想使用C / N噪声模式。因为我使用多个基带发生器同步功能,我无法使用触发类型为

2019-03-22 07:31:28

本文将从几种无线通信系统对终端基带芯片的需求开始讨论,介绍一种由简约纳电子公司设计完成的适用于2G/3G/4G的软件无线终端基带芯片平台。

2021-04-19 08:07:18

您好!我在看论坛下载的K2_STK_DSP_v1.1.zip中的SRIO部分的代码,其中 SRIO_Interrupts.c中的函数 interrupt void SRIO

2018-08-03 06:27:02

本帖最后由 一只耳朵怪 于 2018-6-19 15:13 编辑

最近发现论坛上好多SRIO的帖子,刚好应客户需求我总结了一些SRIO的东西,在这里也分享出来,作为抛砖引玉吧。首先坦白来说我

2018-06-19 04:30:00

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 编辑

因为项目需求,一片C6670需要连接到两片FPGA,但是又觉得没必要使用SRIO SWITCH。所以我的问题是:C6670

2018-06-19 00:53:24

?SRIO_2DSP_Test()中的Keystone_SRIO_match_ACK_ID()是用来检测相应port的链路是否建立成功,函数参数DSP1_SRIO

2018-06-19 00:53:06

你好我对DSP和SRIO之间的通信感兴趣。有人知道virtex-6 FPGA是否有srio引脚,以及如何配置?

2020-06-14 14:22:51

本帖最后由 一只耳朵怪 于 2018-6-19 15:35 编辑

不管用CCS 提供的PDK例子,还是论坛上提供的SRIO例子,得出的结果相同:SRIO external loopback

2018-06-19 06:26:42

本帖最后由 一只耳朵怪 于 2018-6-20 11:00 编辑

在K1_STK_v1.1开发包的srio工程内函数SRIO_PktDM_init内对srio内的PKTDMA

2018-06-20 05:21:38

本帖最后由 一只耳朵怪 于 2018-6-19 10:45 编辑

我用的硬件是TMDSEVM6678LE评估版,CCS5.2,pdk_C6678_1_1_2_5。我想将测试SRIO内环的工程

2018-06-19 04:22:50

Hi,Ti guys,我在使用自己板上的c6678,利用论坛上keystone_srio程序调试dsp和fpga端的通信。同事从fpga(v6,srio核)看来收发地址都是34卫的,但我调DSP互联

2018-12-28 11:08:14

可编程基带滤波器用于软件定义的 UHF RFID 阅读器

2019-08-01 12:35:31

基于TMS320C6455的高速SRIO接口设计

引 言

数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领

2010-02-24 16:58:35 1641

1641

基带传输,基带传输是什么意思

数字信号可以直接采用基带传输,所谓基带就是指基本频带。基带传输就是在线路中直接传送数字信号的电脉冲,这是

2010-03-18 14:36:00 10901

10901 基带网 | ~窄带网),基带网(窄带网)是什么意思

网络从信息传输带宽或传输介质来分:基带网、宽带网。

2010-03-20 13:58:19 1300

1300 基带网络,基带网络是什么意思

计算机网络按照信号频带占用的方式可分为基带网和宽带网。

未经调制的原

2010-03-20 14:02:21 3798

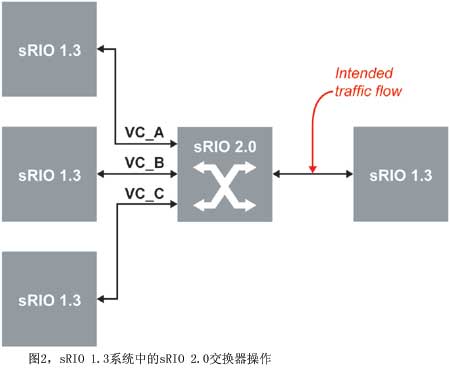

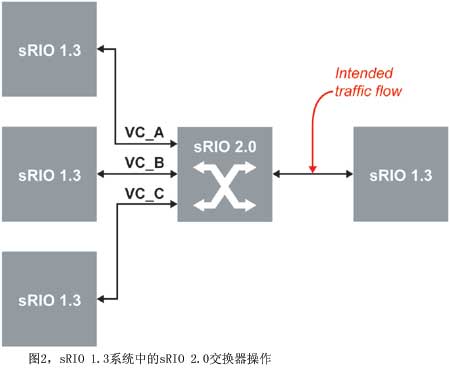

3798 sRIO 2.0中虚拟通道的优势和加速其采用的技术

Serial RapidIO(sRIO)是一种高性能、基于包的技术,可以用于越来越多的应用,包括无线基础设施、存储、医学

2010-01-12 10:20:26 1525

1525

CEVA公司宣布,中国合肥东芯通信股份有限公司(Xincomm Communications,简称东芯通信)已获授权使用CEVA-X DSP内核用于其下一代TDD/FDD-LTE UE基带SoC产品设计

2011-03-25 09:20:45 795

795 本文介绍了这种基于SRIO互联技术的高速实时数据处理硬件平台,并在该平台上研究了多DSP之间、DSP与FPGA之间的SRIO通信技术。

2012-01-10 15:07:55 3561

3561

本内容介绍了手机基带相关内容,手机基带是什么,手机基带版本等

2012-05-24 14:48:32 5527

5527 电路功能与优势 该电路是灵活的频率捷变中频至基带接收机。中频和基带上的可变增益用于调整信号电平。 ADRF6510 基带ADC驱动器还包括可编程低通滤波器,可消除通道外阻塞和噪声。 此滤波器的带宽

2017-11-24 10:48:14 561

561

为了满足2ynq-7000系列芯片的SRIO数据传输要求,提出了一种基于FPGA控制DMA传输进行SRIO通信的设计方案,并完成了ARM与FPGA核间高吞吐率的数据交互操作。系统的FPGA部分主要

2017-12-21 11:37:03 30

30 本文件描述串行RapidIO®(srio)the on the tms320c6474外围设备。

2018-04-16 16:49:07 10

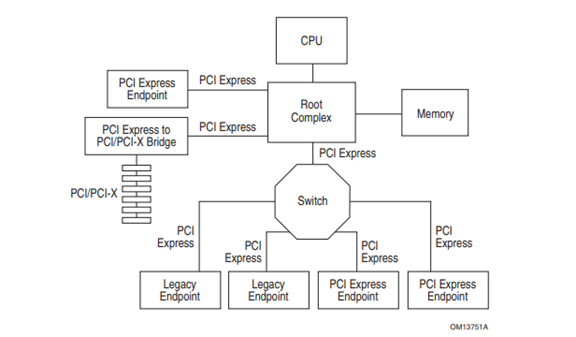

10 SRIO是面向嵌入式系统开发提出的高可靠、高性能、基于包交换的新一代高速互联技术,已于2004年被国际标准化组织(ISO)和国际电工协会(IEC)批准为ISO/IECDIS 18372标准。SRIO则是面向串行背板、DSP和相关串行数据平面连接应用的串行RapidIO接口。

2020-06-17 11:48:12 2555

2555 本文为您分享基于C66x+FPGA的SRIO开发视频教程,适用于创龙TMS320C6678、TMS320C665x、Kintex-7、Artix-7平台。

2020-07-01 10:47:39 1760

1760 CN0320:基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机

2021-03-18 23:25:41 0

0 对SRIO网络中的节点进行枚举并建立网络拓扑信息,以路由跳数定义路由的成本,根据改进 Floyd- Marshal算法计算并保存交换节点间的K最短路径。给岀预期负载的概念和链路上的路由路径数量来定义链路的负载,采用负载均衡算法从K最短路径中进行选路,建

2021-05-11 14:47:51 9

9 随着PCIe接口、以太网接口的飞速发展,以及SOC芯片的层出不穷,芯片间的数据交互带宽大大提升并且正在向片内交互转变;SRIO接口的应用市场在缩小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用场景中仍然占有一席之地。

2022-08-02 10:00:26 3111

3111

基带单元 (BBU) 是电信网络中处理基带信号的设备。BBU 充当基站的集中“枢纽”,处理上行链路和下行链路数据流量,并通过光纤控制 RRU(远程无线电单元)功能。

2022-09-01 18:13:48 10683

10683 目前具备SRIO接口的硬件不多,推荐广州星嵌电子科技有限公司开发的DSP+FPGA+RAM开发板XQ6657Z35-EVM。

2022-11-08 17:22:21 742

742

使用于STM32(符合IEC 61508标准)的X-CUBE-STL功能安全包适应其他安全标准

2022-11-21 17:06:43 2

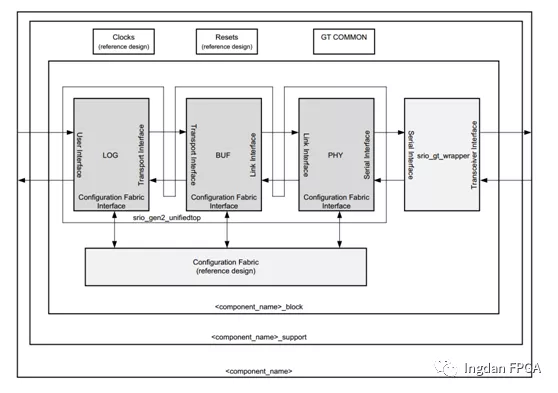

2 数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层

2023-03-03 10:19:53 725

725 摘要: 现代 信号 处理系统通常需要在不同处理器之间实现高速数据 通信 ,SRIO协议由于高效率、低延时的特性被广泛使用。本文研究了在 FPGA 和 DSP 两种处理器之间实现SRIO协议的方法

2023-03-20 15:00:01 1324

1324 SRIO这种高速串口复杂就复杂在它的协议上,三层协议:逻辑层,传输层以及物理层。

数据手册会说这三层协议是干什么的呢?也就是分工(【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 1176

1176

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-09-04 18:19:18 683

683

电子发烧友网站提供《奈奎斯特准则如何运用于基带采样、欠采样和过采样应用.pdf》资料免费下载

2023-11-28 09:25:33 0

0 在于定义、功能的不同。射频芯片是指用于实现无线通讯收发功能的芯片。它可以将模拟信号转换成数字信号,并进行调制、解调等操作,在无线通讯中发挥着非常重要的作用。基带芯片是指完成基础处理功能的芯片,比如数字信号处理、调制解调等功能,但不包含射频信号的处理。

2024-01-06 16:16:17 1506

1506

SRIO(Serial RapidIO)交换芯片是一种高性能的通信芯片,专门设计用于实现基于SRIO协议的数据交换和传输。SRIO是一种点对点串行通信协议,广泛应用于嵌入式系统、高性能计算、网络通信

2024-03-16 16:40:42 1567

1567 SRIO(Serial RapidIO)交换芯片是一种基于RapidIO(快速输入输出)技术的高速网络通信芯片。RapidIO是一种高性能、低延迟的网络通信标准,专为嵌入式系统设计,广泛应用于通信基础设施、军事和航空、工业自动化以及汽车等领域。

2024-03-21 16:30:37 72

72 SRIO交换芯片属于高速网络通信芯片的一种,具体来说,它们是基于RapidIO(快速输入输出)技术的串行通信芯片。RapidIO是一种用于高性能嵌入式系统的互连技术,它支持多种通信协议和拓扑结构,适用于需要高速、低延迟通信的应用场景。

2024-03-21 16:33:20 98

98

电子发烧友App

电子发烧友App

评论