本文介绍了时钟扩频技术的原理、分类,结合它在摄像头的具体应用案例,与传统EMI抑制手段的实际效果进行对比,突显时钟扩频技术在抑制时钟EMI上的优势。目前,时钟扩展频谱技术被广泛使用在图像采集、图像

2018-05-18 02:13:00 2042

2042

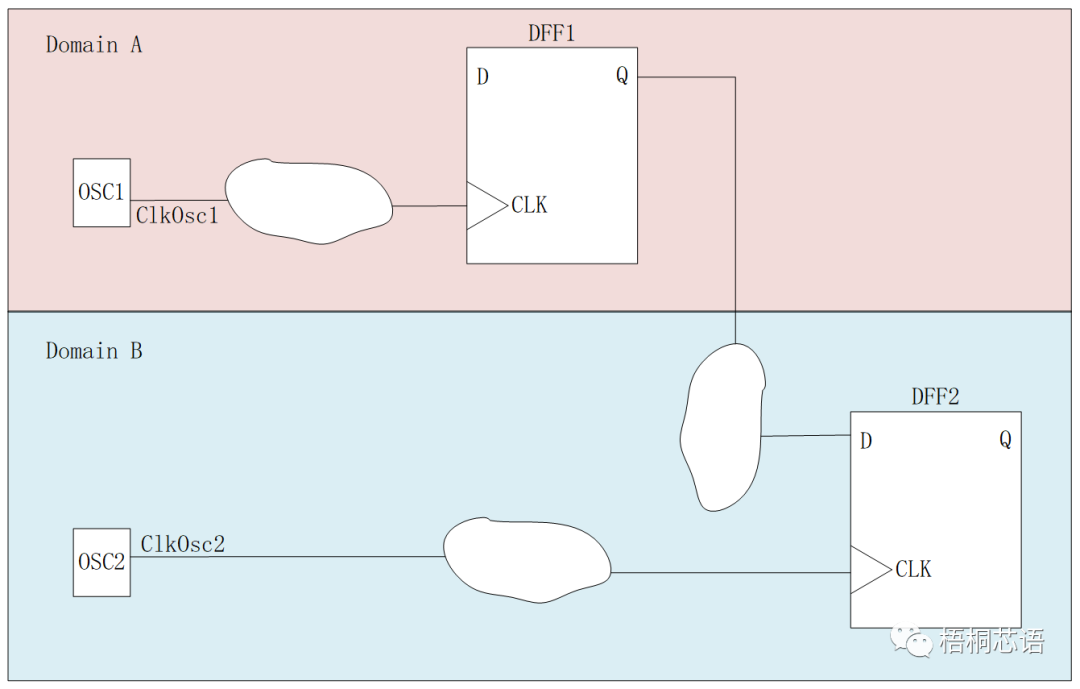

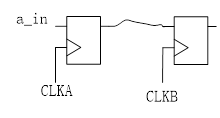

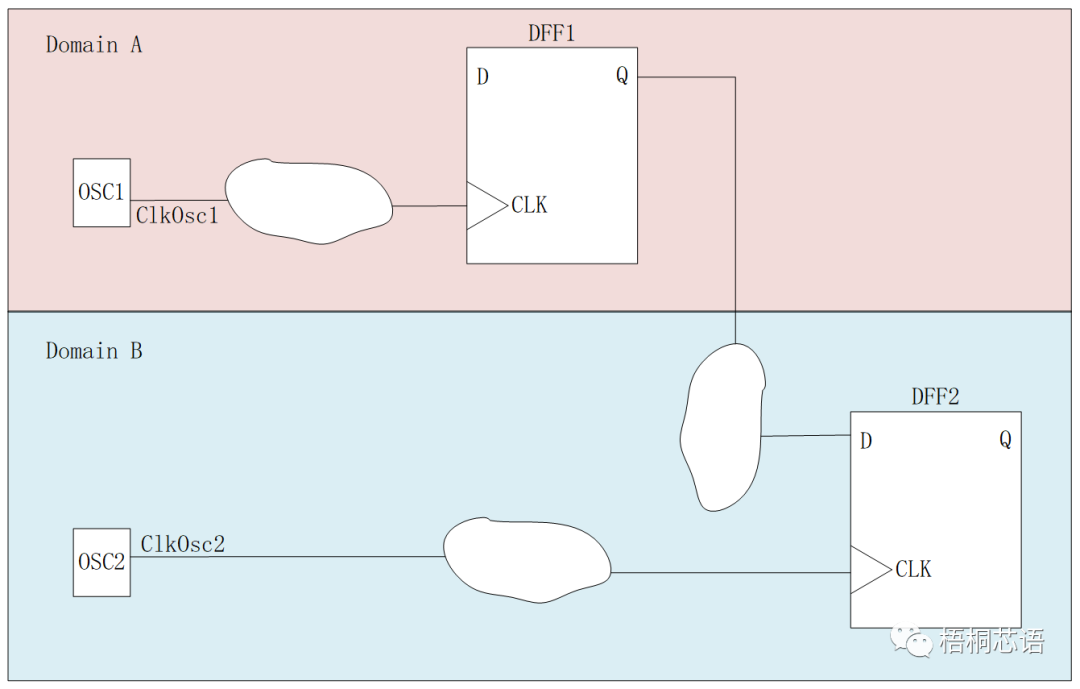

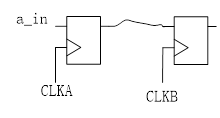

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 5317

5317

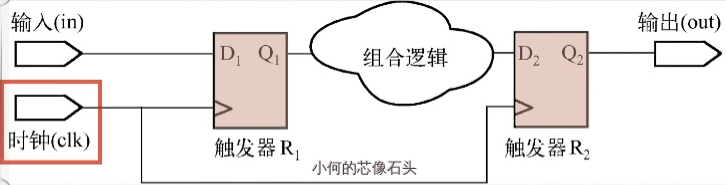

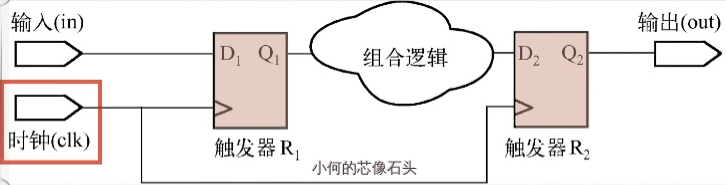

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

跨时钟域路径分析报告分析从一个时钟域(源时钟)跨越到另一个时钟域(目标时钟)的时序路径。

2020-11-27 11:11:39 5449

5449

我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

2022-10-09 10:44:57 4599

4599 今天我们将讨论时钟如何影响精密 ADC,涉及时钟抖动、时钟互调和时钟的最佳 PCB 布局实践。

2023-04-11 09:13:22 645

645 在一个复杂的SoC(System on Chip)系统中,不可能只有一个时钟。我们一般认为,一个时钟控制的所有寄存器集合处于该时钟的时钟域中。

2023-08-01 15:48:20 1052

1052

时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 503

503

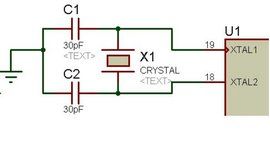

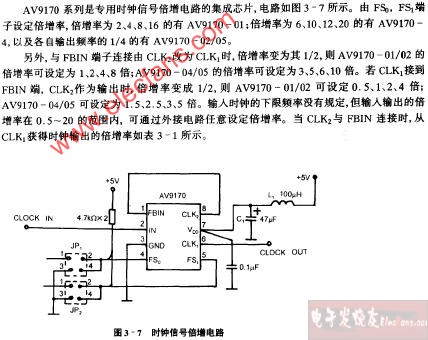

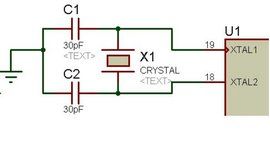

上篇文章我们讲了时钟信号的几个重要参数,今天我们简单讲一下在设计中最常用到的几种时钟信号产生的方法,由于篇幅限制,我们不对具体的原理进行讲述,有兴趣的朋友可以在网上搜索相应的文章进行深入了解,另外

2019-06-05 04:20:28

PLL不仅被广泛用在通信系统中产生方便调节的不同频点的高频率本振信号(LO),还被广泛用在处理器、FPGA、通信器件中用于生成器件内部的高速时钟。USB接口芯片的时钟产生及内部PLLDDS生成任意频率

2019-06-06 04:20:03

了这些寄生信号。整合 BB 滤波器可最大限度地消除这些寄生信号。本文将探讨这些寄生信号是如何出现在调制器输出端的。图 1:OIP3 测量频谱分析仪截图在图 1 所示的频谱分析仪截图中,有两个 RF

2018-09-19 14:43:36

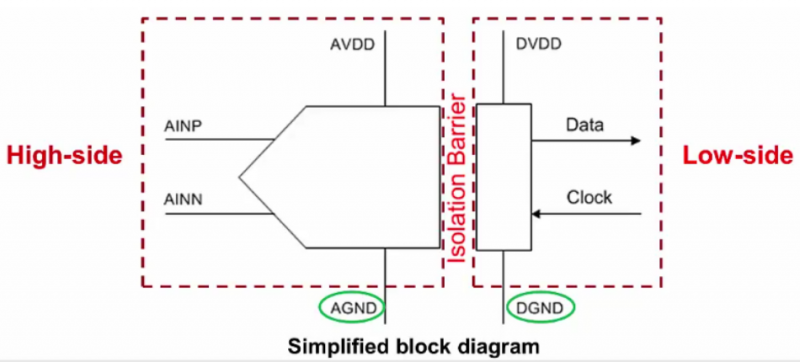

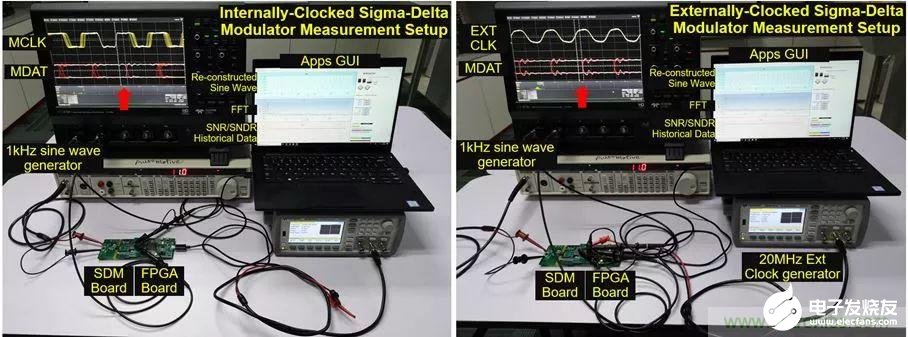

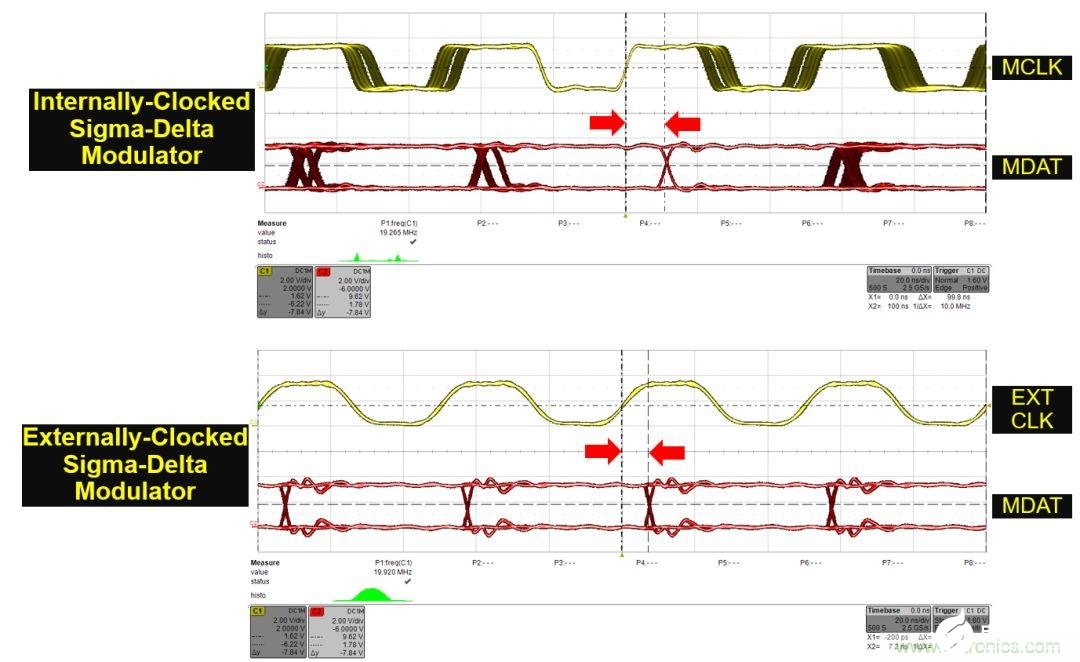

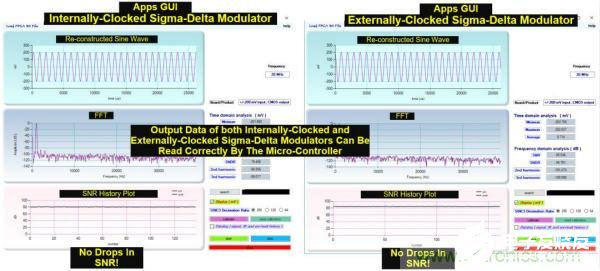

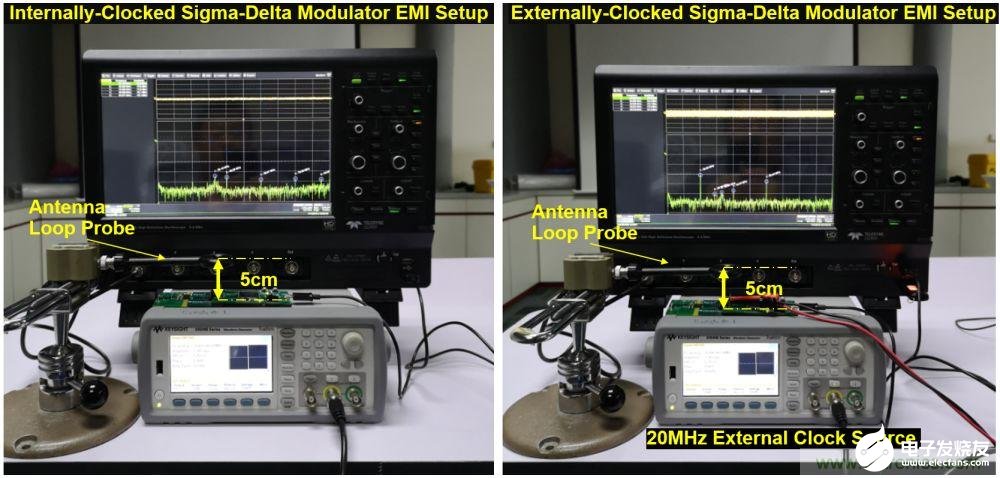

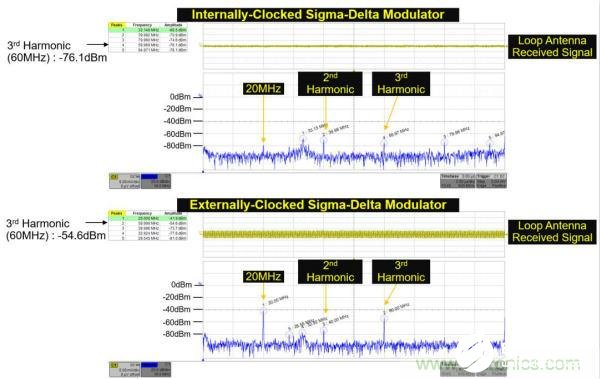

设置,用于测量两类Σ-Δ调制器的时钟信号的EMI从图6中示波器捕获的图像可以清楚看出,外时钟源产生的EMI要高得多,在时钟信号频率及其谐波处达到峰值。例如,对于60MHz的三次谐波,外时钟源产生的EMI比内时钟Σ-Δ调制器输出时钟信号的高20dB。

2020-10-21 16:12:12

速率时钟或数据将被破坏。(使用瞬态脉冲频率为100 kHz。)操作理论电路信息AD7400A隔离∑-Δ调制器将模拟输入信号转换为高速(10 MHz典型)的单位数据流;调制器的单位数据的时间平均值与输入

2020-09-25 17:55:01

什么是时钟脉冲?为什么CPU需要时钟?CPU的时钟信号是如何产生的?

2021-10-20 07:21:14

包括有源晶振、无源晶振、时钟产生器等。MCG 模块提供九种不同的工作模式,分别是:锁频环片内时钟模式( FEI),锁频环片外时钟模式(FEE),锁频环旁路片内时钟模式(FBI),锁频环旁路片外时钟模式

2015-02-10 15:39:48

MSP430 时钟系统3个振荡器 3个时钟信号时钟源1低频时钟源:外接32768Hz晶振工作在低频模式ACLK辅助时钟2 高频时钟源:外接8MHz晶振 MCLK主系统时钟3 数字控制RC振荡器 产生

2021-11-29 07:22:07

滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。 2 时钟线的处理 2.1)建议先走时钟线。 2.2)频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个

2018-09-11 16:05:40

用时钟源来产生时钟!在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①、HSI是高速内部时钟,RC振荡器,频率为8MHz。②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者

2021-08-19 06:49:53

(HSE,HSI,LSE,LSI)产生的过程比430简单许多,430的几个时钟源(XT1CLK,XT2CLK,VLOCLK,REFOCLK,DCOCLK,DLOCLKDIV)在产生时还有一些基础的配置。二、时钟源产生模块分析1、osc模块这一部分是外接了一个振荡器(可以是手表晶体振荡器、标.

2022-02-15 06:17:26

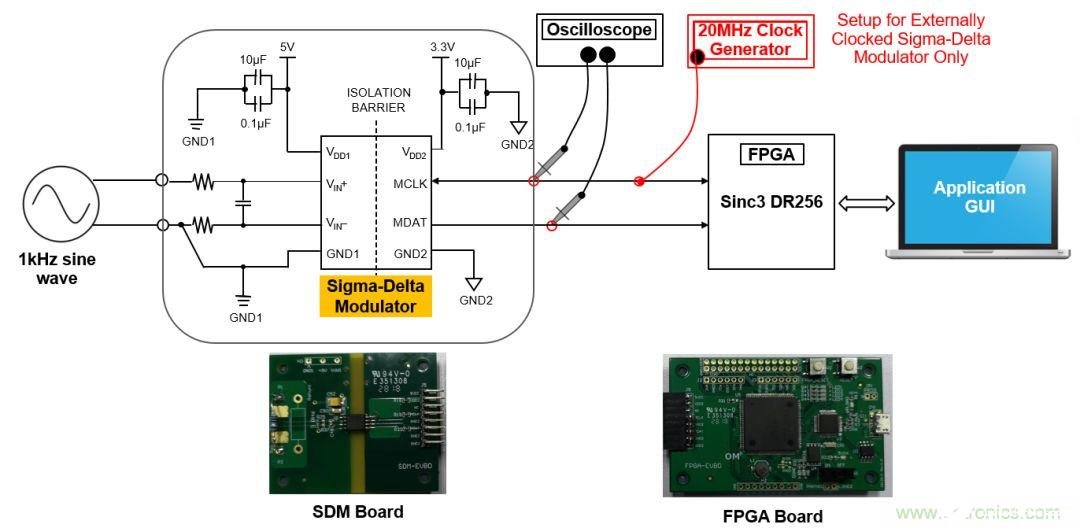

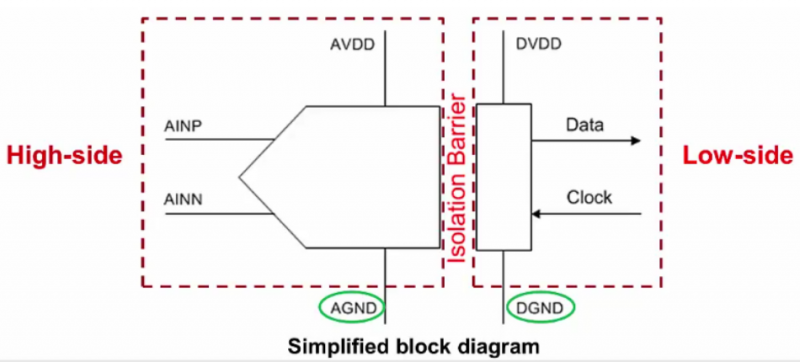

的基本分析开始,如图1所示。 图 1:Δ-Σ调制器内部框图 调制器根据调制器时钟运行,决定了输入的采样间隔。调制循环通过对输入采样和1位DAC之间的差分进行积分而开始。比较器根据积分器值确定下一个调制器

2019-08-12 04:45:06

因素,例如成本、功耗以及性能水平,但对大多数系统设计人员而言,一个重要目标是在成本控制范围内提高效率。F从霍尔效应传感器到分流电阻与隔离式Σ-Δ调制器耦合的分流电阻可提供最优质的电流反馈,其中的电流

2018-10-10 18:14:01

成本、功耗以及性能水平,但对大多数系统设计人员而言,一个重要目标是在成本控制范围内提高效率。F从霍尔效应传感器到分流电阻与隔离式Σ-Δ调制器耦合的分流电阻可提供最优质的电流反馈,其中的电流

2018-10-18 11:27:14

电阻 与隔离式Σ-Δ调制器耦合的分流电阻可提供最优质的电流反 馈,其中的电流电平足够低。目前,系统设计人员明显倾向于 从霍尔效应传感器转移到分流电阻,并且与隔离式放大器方案 相比,设计人员更倾向于采用隔离式

2018-10-18 10:49:28

如何设计一个程序,使它可以收到外界指令调整信号速率,产生信号速率可调的0,1信号?我的想法时先产生一个速率很高的时钟,然后按不同抽样率对它抽样,但明显这样效率不够高,请问大家有什么办法呢

2014-11-06 21:43:10

扩频时钟调制器DS1081L资料下载内容主要介绍了:DS1081L引脚功能DS1081L功能和特性DS1081L应用范围DS1081L内部方框图DS1081L极限参数DS1081L典型应用电路

2021-04-02 07:34:06

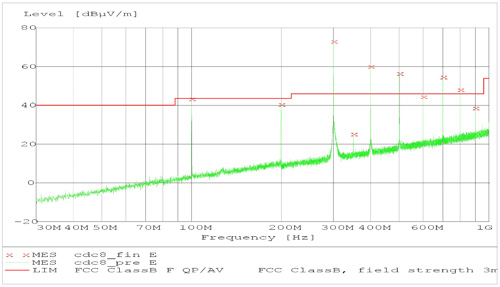

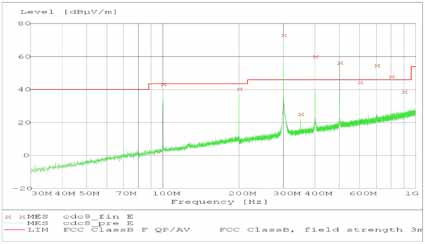

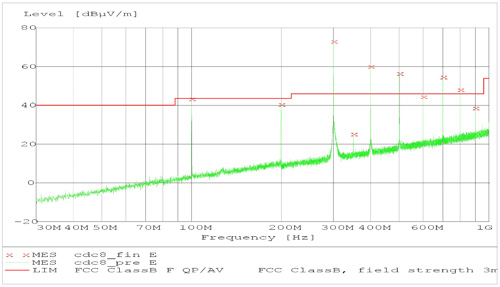

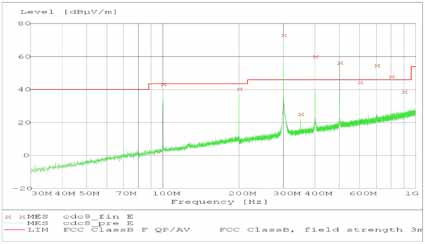

,EMI 可通过频谱分析仪测量,如图1 所示。图中,绿色信号存在一些超出红色 FCC 屏蔽的频率分量(300MHz、400MHz 和 500MHz 等)。 控制时钟引起 EMI 的一些方法都基于上述两种

2018-09-19 14:42:35

MS2400是瑞盟科技推出的一款二阶Σ-Δ调制器,集成片上数字隔离器,能将模拟输入信号转换为高速1位码流。调制器对输入信号连续采样,无需外部采样保持电路。模拟信号输入满量程为±320 mV,转换后

2021-10-12 12:14:32

存在于信号之间的寄生电感/电容,或者通过电源或接地连接的无用耦合,从而产生 EMI;或者2)直接通过电子/磁辐射,即辐射性 EMI。由于两个原因,时钟信号常归咎于 EMI。即使时钟低频率运行,较好的时钟

2022-11-23 06:43:42

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统的逻辑控制和译码。DSP的时钟输入为15MHz

2023-06-19 06:43:17

你们好,

我们正在使用AD9779A进行设计,有如下疑问:

(1) 使用AD9779A的数据时钟信号(DATACLK)作为FPGA内部PLL的参考时钟,再用FPGA PLL产生的时钟信号把数据

2023-12-20 07:12:27

我们一般使用FPGA都需要有外部时钟信号输入,在经过分频倍频等操作实现特定的功能,我想问问,能不能用FPGA自己产生时钟信号,不需要外部输入时钟信号???求解答!

2019-05-24 04:05:29

时钟产生和分发设计指南:在您设计时钟电路时是否仅仅因为某些方法在过去一直沿用,所以就采用它呢?或者您曾经使用过某个器件仅仅是因为其他设计中使用了它?这种现象在如

2009-09-06 09:01:45 0

0 16MHZ至134MHZ扩展频谱时钟调制器DS1083L是扩展频谱时钟调制器IC可降低时间数字电子设备的EMI

2010-04-09 15:19:22 18

18

SPWM调制方法对比分析

摘要:对比分析了三种正弦波脉宽调制(SPWM)控制方法,指出各自的优缺点及应用,给出了一些数学

2009-07-06 13:33:51 12452

12452

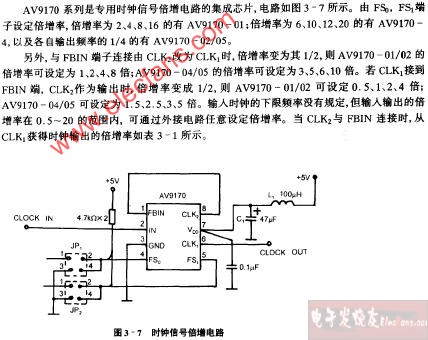

时钟信号倍增电路图

2009-07-14 17:18:36 741

741

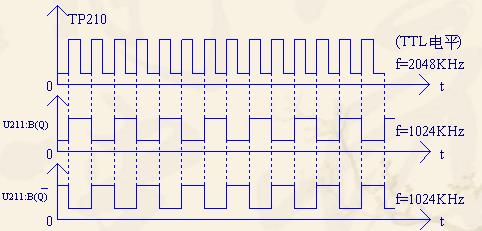

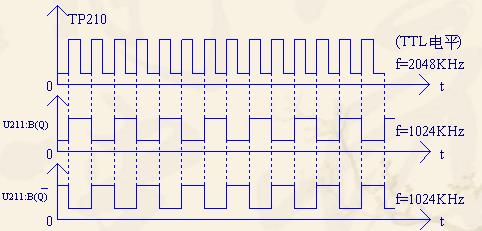

2048KHz(2M)时钟信号产生电路

2009-10-11 10:20:02 2807

2807

控制板级时钟分配期间出现的EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI&n

2010-01-19 11:13:14 1958

1958

控制板级时钟分配期间出现的 EMI

今天,我们来谈谈所有电子系统都存在的一种常见问题——电磁干扰也即 EMI,并侧重讨论时钟的影响。

从广义来讲,EMI 是

2010-01-21 09:36:19 874

874

本文简要介绍了SSC扩频时钟的基本概念以及如何使用力科示波器进行信号的扩频时钟的测试。

2011-05-17 11:23:34 4648

4648

所谓门控时钟就是指连接到触发器时钟端的时钟来自于组合逻辑;凡是组合逻辑在布局布线之后肯定会产生毛刺,而如果采用这种有毛刺的信号来作为时钟使用的话将会出现功能上的错

2011-09-07 16:11:32 34

34 基于片上偏差对芯片性能的影响,分析对比了时钟树设计与时钟网格设计,重点分析了时钟网格抗OCV影响的优点,并利用实际电路应用两种方法分别进行设计对比,通过结果分析,验证

2012-05-07 14:13:14 36

36 时钟抖动时域分析(下):

2012-05-08 15:26:25 29

29 跨时钟域信号的同步方法应根据源时钟与目标时钟的相位关系、该信号的时间宽度和多个跨时钟域信号之间的时序关系来选择。如果两时钟有确定的相位关系,可由目标时钟直接采集跨

2012-05-09 15:21:18 63

63 ASM3P2182A是一个多才多艺的扩频频率调制器专门为范围广泛的输入时钟频率从25兆赫到210兆赫。 ASM3P2182A可以产生EMI减少时钟从OSC或生成一个系统时钟。 ASM3P2182A

2017-04-06 10:24:19 7

7 的直列式电机相电流感应。调制器输出采用曼彻斯特编码,简化了 MCU 和调制器之间的时钟和数据信号路由。该调制器具有高 CMTI,有助于抑制逆变器开关噪声瞬变在控制器侧造成数据损坏。采用小尺寸调制器,实现了

2017-12-10 09:34:48 0

0 时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成一个最基本的动作。时钟周期是一个时间的量。时钟周期表示了SDRAM所能运行的最高频率。更小的时钟周期就意味着更高的工作频率。

2018-03-11 10:07:52 49788

49788 ,SSCG通过时钟内部集成电路调制频率的手段来达到抑制EMI峰值的目的。SSCG不仅调制时钟源,其它的同步于时钟源的数据、地址和控制信号,在时钟展频的同时也一并得以调制,整体的EMI峰值都会因此减小,所以说,时钟展频是系统级的解决方案。这是SSCG相比其它抑制EMI措施的最大优势。

2018-08-22 14:45:27 8872

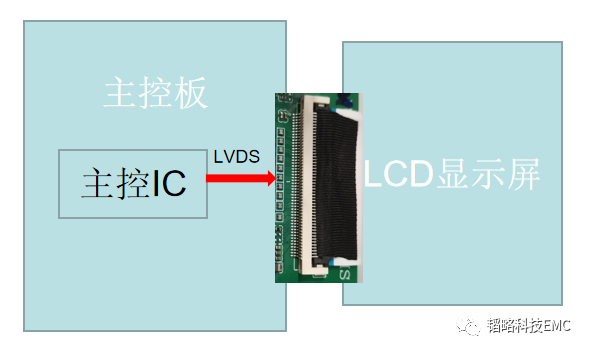

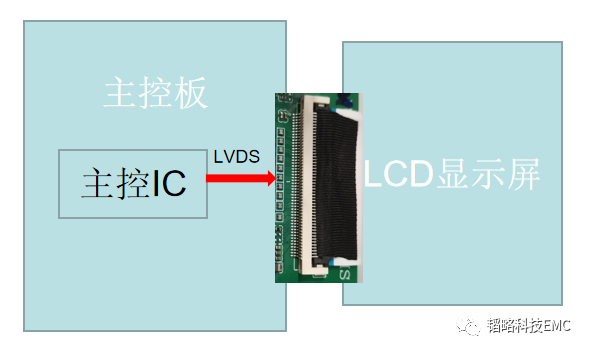

8872 对信号进行调制,将信号能量扩展到一个较宽的频率范围内,能有效的抑制系统的EMI问题。一、具体案列分析:客户的样机是工业类机器人,样机中带屏,屏的时钟取自主芯片。如上图,这是客户没有整改之前测试的实验

2018-11-06 14:53:48 742

742 首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行

2018-12-06 11:53:10 59988

59988

想象一下,如果频率较高的时钟域A中的信号D1 要传到频率较低的时钟域B,但是D1只有一个时钟脉冲宽度(1T),clkb 就有几率采不到D1了,如图1。

2019-02-04 15:52:00 10841

10841

电子产品多功能化、高速化、小型化的发展,意味着对内部时钟频率的要求将越来越高。因为时钟信号是周期信号,所以在频域上的能量是集中在某个频率上的,这也就造成了时钟EMI测试超标的问题。

2019-02-02 16:25:00 5368

5368 隔离的Σ-Δ调制器长期以来被证明可以在嘈杂的工业电机应用环境中提供非常高的精度和强劲的电流和电压感测能力。有两类隔离型Σ-Δ调制器:一种是在IC内部产生时钟信号;另一种是从外部时钟源接收时钟信号。

2019-07-27 09:22:29 750

750 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2854

2854 隔离调制器是一种将模拟输入信号转换为由0和1组成的高速数字比特流,同时使用隔离层将输入和输出电路隔离开来的Δ-Σ调制器。该隔离层对电磁干扰有很强的抵抗力,电磁干扰通常称为EMI。干扰由外部源产生且会对电路产生负面影响。

2019-09-14 10:02:00 1655

1655

SSDCI1108AF是减少电磁干扰(EMI)的时钟发生器。利用内调制器对振荡频率进行周期性的微调,可以使不必要的电磁干扰(EMI)峰值衰减。SSDCI1108AF接收来自基本晶体或外部基准的输入时钟,并锁定到该输入时钟,以传递1x调制时钟输出。

2020-04-17 08:00:00 10

10 。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 1482

1482 电子产品多功能化、高速化、小型化的发展,意味着对内部时钟频率的要求将越来越高。因为时钟信号是周期信号,所以在频域上的能量是集中在某个频率上的,这也就造成了时钟EMI测试超标的问题。

2020-11-11 10:33:28 5091

5091 在本文中,将详细研究这两类隔离-调制器的输出数据信号完整性。并通过简单的电磁干扰(EMI)测试设置、对由这两类-调制器的高频时钟信号产生的EMI进行比较。 对输出数据信号完整性和时钟信号电磁干扰

2020-11-18 14:59:50 996

996 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 的错误操作而泄露文中对时钟故障的产生原因进行了分析,并描述了几种主要的毛刺注入机制,包括相同频率时钟切换、不同频率时钟切换以及模糊时钟注入。最后介绍了3种时钟毛刺注入攻击的最新实际运用和未来的发展方向。

2021-04-26 14:20:04 9

9 时钟芯片运行需要时钟支持,如果没有时钟电路来产生时钟驱动时钟芯片,那时钟芯片就不能执行程序。时钟芯片可以看成是在时钟驱动下的时序逻辑电路。

2021-05-18 09:29:14 12258

12258 PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 stm32内部时钟有哪些时钟源 在STM32中,可以用内部时钟,也可以用外部时钟,在要求进度高的应用场合最好用外部晶体震荡器,内部时钟存在一定的精度误差。 内部时钟有2个时钟源可以选分别是HSI

2021-07-22 10:38:57 15728

15728 门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。 一、什么是门控时钟 门控时钟技术(gating

2021-09-23 16:44:47 12193

12193

/4,1/8;(4)RTC时钟单独控制时钟,时钟频率1KHz;(5)各外设时钟可以单独门控,满足低功耗要求。1.2 时钟设计要点 (1)DFT可控,隔离,可观测。(2)上电工作外部参考...

2021-11-05 17:35:59 8

8 振荡器 产生内部时钟 SMCLK 子系统时钟时钟系统配置寄存器DCO控制寄存器 DCOCTL1、DCOx 频率选择 8种频率2、MODx DAC调制器设定 微调DCO 的输出频率基本时钟系统控制寄存器 BCSCTL1 BCSCTL2BCSCTL11、XT2OFF :XT2高速晶振开关

2021-11-19 21:06:06 18

18 信号-SOC-IN OSC-OUT悬空HSI:8MHz RC产生 做系统时钟或2分频后PLL输入相对HSE优点为启动时间短 置“1”,输出时钟释放系统复位1 HSIAL[7:0]位...

2021-12-02 13:36:06 0

0 信号-SOC-IN OSC-OUT悬空HSI:8MHz RC产生 做系统时钟或2分频后PLL输入相对HSE优点为启动时间短 置“1”,输出时钟释放系统复位1 HSIAL[7:0]位...

2021-12-22 18:59:46 0

0 如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

2022-09-16 08:58:49 1919

1919

本章的主要内容: 分析时钟驱动器、时钟信号的特殊布线 改进时钟信号分配的特殊电路

2022-09-20 14:55:40 0

0 时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的时钟容易出现毛刺,影响设计的功能实现;组合逻辑固有的延时也容易导致时序问题。

2022-10-26 09:04:51 823

823 控制板级时钟分配期间出现的 EMI

2022-11-07 08:07:32 0

0 时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源时钟同相

2023-01-05 14:00:07 949

949 隔离放大器的输入级由一个驱动输入放大器-ΔΣ调制器的输入放大器组成。输入放大器的增益由内部精度电阻器进行固定和设置,ΔΣ调制器则使用内部参考电压和时钟发生器来将模拟输入信号转换为数字位流。

2023-02-10 15:12:49 749

749 RF DAC的无杂散动态范围受到严重的数字do主开关的限制,这会干扰模拟输出信号。介绍了一种扩频时钟发生器(SSCG)的设计、布局和仿真。SSCG调制用于切换DAC数字块的时钟频率,以减少DAC

2023-02-14 16:43:56 0

0 时钟电路是一种电路,它可以产生定期的时钟信号,用于控制电子设备的运行。

它的特点是可以产生定期的时钟信号,可以控制电子设备的运行,可以提高电子设备的精度和可靠性。时钟电路的应用非常广泛,它可

2023-02-20 18:16:38 5974

5974 系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 理想值附近的一个范围内,从而造成相邻的时钟边沿存在偏差。在时序分析时,时钟抖动是一个重要的因素。多种因素会导致时钟抖动,包括PLL回路噪声、电源纹波、热噪声以及信号之间的串扰等。

2023-06-09 09:40:50 1128

1128

即电路中的所有受时钟控制的单元,全部由一个统一的全局时钟控制

2023-06-27 09:54:21 377

377

跨时钟域是如何产生的呢?现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率下。

2023-06-27 11:39:41 902

902

时钟电路用于产生稳定的时钟信号,常见于数字系统、微处理器、微控制器、通信设备等。时钟信号用于同步各个电子元件的操作和数据传输,确保系统的正常运行。

2023-08-03 14:46:04 1242

1242 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器

2023-08-16 09:53:23 462

462

如何抑制时钟电路产生的电磁辐射? 在现代电子工业中,时钟电路是不可或缺的,尤其是在数字电路中,时钟电路起着控制数据流动的作用。然而,在时钟电路运行时,它会产生电磁辐射,这会对周围的设备和人体健康造成

2023-09-12 17:06:49 557

557 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1767

1767 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 1370

1370 时钟信号怎么产生的 时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作

2023-09-15 16:28:22 1496

1496 是数据信号(SDA)。SCL信号是在IIC通信中非常重要的一个信号,它确定了数据的传输速率以及同步时序。 IIC时钟信号的产生需要硬件支持,一般通过外部晶振或者内部时钟源产生。在IIC总线使用过程中,时钟信号的频率很重要,必须要与所有设备的时钟频率保持一致。一般来说,为了保证

2023-09-19 17:16:02 735

735 方法来使不同步的时钟信号同步。下面我们就来详细讲解这些方法。 1. 时钟缓冲器同步法 时钟缓冲器同步法是指通过一个时钟缓冲器来同步两个不同步的时钟信号。其原理是将一个时钟信号通过一个缓冲器反转,产生一个相反的信号,

2023-10-18 15:23:48 771

771 可以说是计算机运行的重要组成部分之一。 时钟芯片的工作原理: 时钟芯片是通过一系列简单的电路来实现的,它内部包含一个晶体振荡器,用来产生一个稳定的基准信号。这个基准信号通过分频器分成不同频率的信号输出到不同的电

2023-10-25 15:02:33 2317

2317 什么器件可以产生时钟信号?时钟信号是用来做什么用的?时钟信号起什么作用? 时钟信号是一个精确的电信号,它可以通过电子器件来产生,并且具有一定的频率和周期。时钟信号在电子系统中具有非常重要的作用,因为

2023-10-25 15:07:45 637

637 如何用时钟振荡器产生稳定的100hz或1hz的时钟信号? 时钟信号是电子系统中至关重要的组成部分,用于同步各种信号和操作。它需要稳定、准确、可靠地工作,以确保系统性能。时钟信号的产生可以通过许多

2023-10-25 15:07:55 959

959 什么是时钟电路?什么是脉冲?时钟电路是如何生成脉冲的? 时钟电路是一种电路,它产生的周期性的信号被用作计算机系统的基准。时钟电路产生的信号被称为时钟脉冲或时钟信号。在计算机系统中,时钟信号用于同步

2023-10-25 15:14:17 795

795 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 298

298 如何有效解决LVDS时钟EMI问题

2023-11-23 09:04:46 485

485

对测试结果产生一定的影响。本文将详细探讨差分探头对时钟测试的影响。 首先,差分探头的接触电阻是一个重要的因素。接触电阻会产生测量误差,并且对于高频时钟信号来说影响更加显著。由于差分探头通常连接在被测电路的信号路

2024-01-08 15:36:28 178

178 什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号

2024-01-25 15:40:52 909

909 芯片为什么要时钟信号 时钟芯片的作用是什么? 时钟信号在芯片中起着非常重要的作用。它是芯片的“心脏”,相当于人体的心脏,用于同步和控制芯片中的各个功能模块之间的操作。时钟信号可以提供一个稳定的时间

2024-01-29 18:11:31 626

626 SPICE是一种用于模拟和分析电子电路的计算机程序。在SPICE仿真中,产生时钟信号是许多电路设计和模拟任务中的关键步骤。

2024-02-06 14:22:01 265

265

电子发烧友App

电子发烧友App

评论