电磁干扰(EMI)是一种会通过导致意外响应或完全工作实效从而影响电气/电子设备性能的能量。

EMI是由辐射电磁场或者感应电压和电流产生的。当前高速数字系统中的高时钟频率和短边率也会导致EMI问题。

传导和发射EMI的一个重要产生源是连接交流电源线的电气设备,例如电脑和开关电源,以及带有电动马达的电气设备,例如冰箱、空调和电单车等。

一旦电气设备的EMI传导到一个电路里,里面的线缆就会像一根天线一样,将传导EMI以RFI(无线电干扰)的形式“广播”到整个电路中。

EMI可能影响不大,也可能导致灾难性的故障,所以对EMI的有效控制是非常重要的。电磁兼容性(EMC)是指系统能在指定环境下运行而不会传导或发射过量电池干扰的能力。

EMI标准和相关成本

EMC标准的宗旨是为了确保电子设备不会影响其它电子设备的运行甚至导致设备的故障。

各国针对“电视、广播、便携式娱乐设备、电子游戏和互联网设备”等消费电子设备的EMI屏蔽功能的要求各有不同。

目前为止已经有各种各样的组织发布了EMI规范。在美国,FCC发布了针对A?级和B级电子设备的第15部分J章规范。A?级和A层规范针对的是工业设备,而B级和B层规范则适用于消费电子产品。EMI规则减少了电子设备之间的干扰,解决了健康和安全方面的问题。

如何控制EMI,一般要考虑以下几个因素:

1) PCB设计-“灵敏元件、电源和地面层的隔离”

2) 电路电流-“EMI辐射会随电流增大而增加”

3) 频率,包括回转率-“EMI辐射会导致频率升高”

4) 带宽

5) 电路回路区域-“保持在最小”

6) 屏蔽/过滤-“结合合理的设计、过滤、屏蔽和其它技巧,来以最低成本的方法将EMI控制在所需等级”

7) 展频时钟-“合适的展频数量和调制频率”

8) 抖动应用系统中时钟的中心频率,以便将辐射能量扩展到多个频段,而不是让所有能量辐射到一个频率。

控制和降低EMI的方法

控制和降低EMI有两个基本方法:抑制和吸收。最常用的降噪方法包括合理的设备电路设计、屏蔽、接地、过滤、隔离、分隔和定向、电路阻抗级控制、线缆设计和噪音消除等。

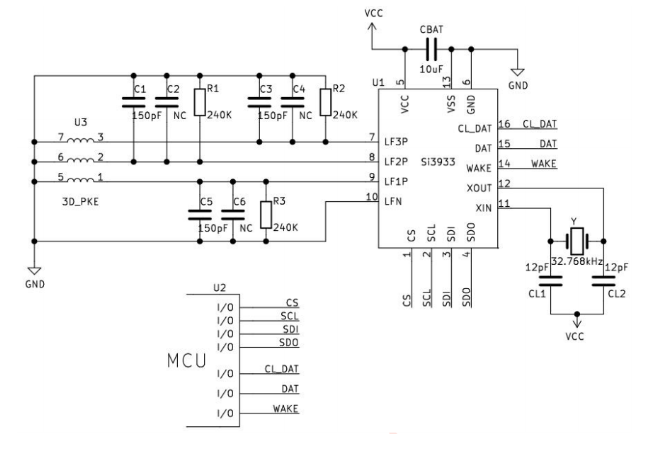

这些方法要求使用无源和有源元件,例如滤波器、扼流器、铁氧体磁珠、箔片和??件,并结合PCB设计规则和展频时钟生成器(SSCG)。

在源头处解决EMI问题

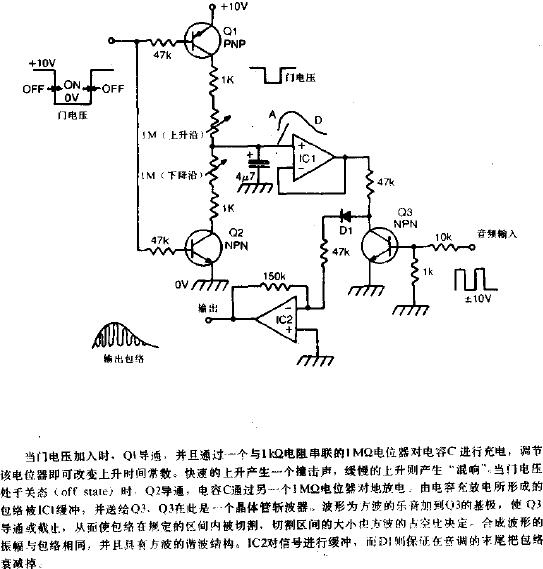

EMC设计的一个基本原则是在PCB的源头处减弱EMI。展频法是指有意将特别带宽中产生的辐射能量扩展到频率域,产生一个带宽更大的信号。展品时钟生成器(SSCG)就可以执行这一功能。

在选择展频时钟来减弱消费电子产品的EMI时,开发人员必须确保以下几点:

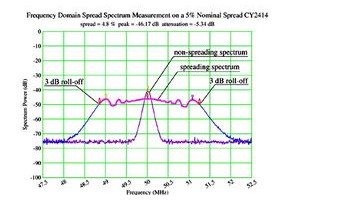

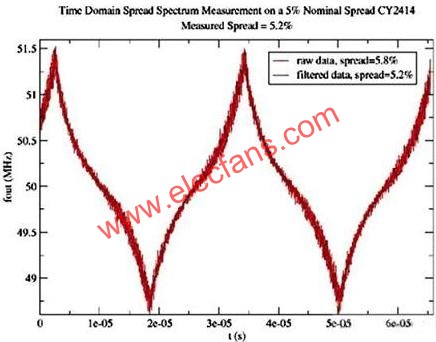

1) 系统必须通过EMI型式测试。良好的频率概图和调制频率是最重要的。高质量的Hershey Kiss频率概图在降低EMI上是性能最好的;与之相比,三角频率概图需要更大的扩展量才能将EMI降低到同样等级(见图1至图3)。调制频率越高,就能将EMI降到更低的程度(如图4)。

2)即便展频有副作用,也要保持系统性能。首先,PLL必须运行于一个理想状态,例如较高的PFD和VCO频率和适当的带宽等等。第二,频率扩展量必须尽可能小,以便保持较高的系统时序余度和较低的周期间抖动。频率扩展量更小,系统的平均频率就不会降低太多,因而系统的运行速度也就不会那么慢。

3)要将对系统总成本的影响最小化。在消费电子产品中,展频时钟芯片的价格向来是一个主要的价格问题。但是,在最近几年消费电子产品复杂性越来越高的同时,开发人员也要慎重考虑开发成本和风险。

比如,在抑制EMI和抖动中即便只有一项要求没有达到,消费电子产品的系统时钟需要调整的可能性就更大。可编程型抑制EMI的方法的灵活性,可以大大降低开发成本和风险,从而确保满足所有要求。

展频时钟生成器

展频时钟生成器(SSCG)可分成可编程和不可编程两种,也可以根据其是否有Hershey Kiss频率还是三角展频来分类。不同消费电子产品的展频时钟对于频率、中心或向下扩展、扩展量、调制频率、Hershey Kiss或三角展频等的要求是不同的。

由于非可编程式展频时钟芯片是为特殊应用定制的,频率范围和扩展量只有几个固定的可选项,要在最大化成本/性能的同时满足最优展频要求,就变得非常困难。

市场上大部分固定功能的时钟芯片都有多个固定的可选择输入频率范围(如20-40MHz, 40-80MHz和80-160MHz)以及扩展率(如0.5%, 1%, 2%和3%)。要实现优化,就需要两套PLL参数,一套针对EMI抑制性能,另一套面向PLL性能。

当实际配置和这些理想设置有偏差时,各种副作用就会产生。比如,如果输入频率不在所选范围的正中,VCO和调制频率就会被直线调整。

如果PLL带宽太低,那么频率概图就会变形,从而影响EMI性能。

当输入频率最低时,结果是最糟糕的:因为PDF和VCO频率都很低,周期间抖动大大增加,并且由于调制频率低而频率概图可能变形,EMI抑制性能就会大大降低。

当扩展量的选择受到限制时,开发人员就必须选择一个超出需要的更大扩展量。这常常会增加周期间抖动,并降低系统时序预算。

如果没有一个扩展率可以满足系统要求,开发人员就必须要求时钟供应商对设计作出改动并提供一款新的芯片,而这个过程中,哪怕仅仅是改变一个金属层那么简单,也最少需要数周的时间,并且成本一般都非常高。

与之相比,一个可编程的展频时钟生成器则能够提供支持可现场编程性的通用时钟,并结合片上非易失性存储器,实现动态的展频参数重置,从而不需要让厂家花大量时间和成本对芯片进行改动。

可编程性还让展频时钟性能能够针对所要求的规格进行优化。比如,开发人员可以规定2.1%的精确扩展率(而不是固定选择的3%),或者为实现所需的频率设置而优化调制模式。

如何利用一个带有2个展频PLL的4PLL型时钟芯片,通过调制频率优化来轻松将EMI降低3 ~4 dB的。这些扩展的PLL都有两个独立扩展模式可供选择。

大部分开发人员都更喜欢使用Hershey Kiss展频时钟来实现更好的EMI抑制性能,但很多时钟供应商都只提供线性展频时钟。在理想情况下,一个SSCG必须同时提供Hershey Kiss和线性展频时钟。展示出Hershey Kiss展频时钟在上面所示的4PLL时钟芯片测试条件下一次性EMI降低了1.67dB。

另外,重要的时钟参数,例如PLL电荷泵电流、VCO增益和输出驱动强度,都是必须能够编程设置的。这样的灵活性能够大大提高系统性能,减少系统开发时间,将改动限制到最小并降低风险。

电子发烧友App

电子发烧友App

评论