您的位置:电子发烧友网 > 电子技术应用 > 测量仪表 > 可靠性分析 >

深亚微米CMOS IC全芯片ESD保护技术(3)

2012年03月27日 16:27 来源:本站整理 作者:秩名 我要评论(0)

(2)VDD加电情形

由于CMOS IC在正常工作时,其VDD是偏压在一同定的电压(例如5伏特)。但是在加电瞬间,VDD电压自0伏特逐渐上升到5伏特,这就是一般所谓power-on瞬时。在这power-on瞬时,要保持STFOD器件在这power-on情形下仍保持关闭,但在:ESD放电情形下导通,可通过RC时间常数的设计来达到此目的。因为VDD power-on电压上升时间是约1ms左右,但ESD电压的上升时间约10ns,因此把ESD侦测电路的RC时间常数设在0.1~1.0us之间,它便可以分辨出VDD Power-on与ESD)放电两种不同的工作情形。

5 全芯片ESD保护架构

ESD保护电路的安排必须全方位地考虑到ESD测试的各种组合,因为一颗IC的ESD失效阈值定义为整颗IC所有引脚在各种测试模式下,最低的ESD耐压值。因此,一个全芯片ESD保护电路的安排要如图6所示,输入输出PAD要能够抑制PS、NS、PD、ND四种模式的静电放电,另外,VDD到VSS也要有ESD保护电路。

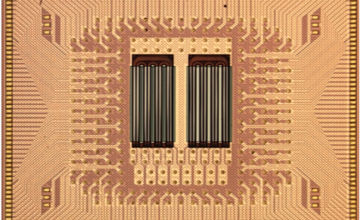

根据实际需要,结合上述各种ESD保护结构,我们提出了一种新颖的深亚微米CMOS IC全芯片ESD保护架构如图7。其中,输入输出PAD外围ESD保护电路都采用改进的SCR结构。其中,输入PAD外围我们选用基于互补式LVTSCR结构设计的ESD保护电路,考虑对下级芯片输入信号的影响,输出PAD上采用抗噪声能力较强HINSCR和HIPSCR器件。实测表明,它们对发生在输入输出PAD上PS、PD、NS和ND四种模式的ESD都起到了很好的抑制作用。

对于VDD与VSS之间的ESD保护电路设计,一方面,要兼顾内部电路版冈设计规则和先进的工艺要求,保护电路在能够实现保护目的的同时,还要尽量节省版图面积;另一方面,由于电源地线较长,VDD与VSS上的寄生电阻电容也较大,如果保护电路的摆放位置离:ESD发生位置较远,其保护作用就会因卜述寄生参数影响而削弱。因此ESD保护电路在芯片中的布局也同样重要。基于以卜考虑我们采用了节省芯片面积的sTFOD结构ESD侦测电路,该电路可完全按照内部芯片的版冈设计规则设计实现,而且不必增加工艺版次。保护电路的安放参照了一套现成的ESD布局设计规则,其布局如图7所示,围绕电源地线均匀地放在芯片四周,巧妙地避免了电源地线之间寄生参数的负面影响。

该全芯片ESD防护设计架构已实际地被用来改善某一IC产品的ESD耐压能力。该IC产品原本ESD耐压能力,在输入/输出脚对VDD/VSS ESD放电测试情形下只能承受1 000V的ESD,在脚对脚的ESD放电测试情形下只能承受500V的ESD。经过图7的应用之后,该IC的ESD耐压能力,在输入/输出脚对VDD/VSS ESD测试下能承受到4000V以上的ESD,在脚对脚ESD测试下能承受到3000V以上的ESD。该全芯片ESD架构在小布局面积下提供了有效而又高水平的ESD保护能力。

6 结论

ESD的防护是整颗集成电路的问题,而不只是输入输出PAD或电源地PAD的问题,即使各个PAl)都有很好的ESD防护能力,不见得整颗集成电路就有很高的ESD防护能力。采用适当的全芯片(whole-chip)防护架构设计,才能真正提升整颗集成电路的ESD防护能力。本文采用改进SCR结构和STFOD器件,提出了一个新颖的深亚微米CMOS IC全芯片ESD保护架构,该架构节省了布局面积,实现了对整个芯片全方位的ESD保护。

本文导航

- 第 1 页:深亚微米CMOS IC全芯片ESD保护技术(1)

- 第 2 页:基于STFOD结构的ESD侦测电路

- 第 3 页:VDD加电情形

标签: