1.1方案选择

阻抗测量通常是向被测对象注入微小的正弦电流信号,同时通过测量电压信号,以获取相关的电阻抗信息。系统不仅要求正弦波信号波形失真小、幅值稳定,而且必须具有频率、幅值、相位可调节的功能。因此正弦波信号发生器的设计是阻抗测量系统的重要环节。

正弦波信号发生器主要有模拟式和数字式两种类型。

模拟方法实现正弦波发生器优点在于电路结构简单、相对成本较低,输出信号失真较小。但也存在明显的不足,即电路的频率、幅值调节困难。

早期的数字式信号发生器是采用向EPROM中写入固定的数字化正弦波信号值,以一定频率读取正弦波表的内存地址,将得到的数字信号进行数模转换,再进一步通过低通滤波器将输出的模拟阶梯波去除高频谐波,从而得到平滑正弦波电压信号。此方法产生的信号稳定可靠,频率、幅值改变灵活,相移补偿方便易行,但相对模拟方法电路复杂,造价较高。

直接数字频率合成技术[21],即DDS(Direct Digital Frequency Synthesizer),是近年来迅速发展起来的第三代频率合成技术。

DDS技术具有频率转换时间短、频率稳定度高、相位噪声低、相位分辨率高等突出优点。而且具有体积小,功耗低的特点,因此采用DDS技术对信号源电路进行设计是一种较为合适的方法。

1.1.1 DDS技术的优点

1.输出频率相对带宽较宽输出频率带宽为50%f s(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40%f s。

2.频率转换时间短DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在DDS的频率控制字改变之后,需经过一个时钟周期之后按照新的相位增量累加,才能实现频率的转换。因此,频率转换的时间等于频率控制字的传输时间。时钟频率越高,转换时间越短。DDS的频率转换时间可达纳秒级,比使用其它的频率合成方法都要短数个数量级。

3.频率分辨率极高若时钟f s的频率不变,DDS的频率分辨率就由相位累加器的位数N决定。只要增加相位累加器的位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,许多小于1MHz甚至更小。

4.相位变化连续改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。

5.输出波形的灵活性只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实现调频、调相和调幅功能,产生 FSK、PSK、ASK和MSK等信号。另外,只要在DDS的波形存储器存放不同波形数据,就可以实现各种波形输出。当DDS的波形存储器分别存放正弦和余弦函数表时,既可得到正交的两路输出。

6.其他优点由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价比极高。

1.1.2 DDS技术原理及实现方法

直接数字频率合成(Direct Digital Frequency Synthesis即DDFS。一般简称DDS)是一种新的频率合成技术。同传统的直接频率合成(DS)、锁相环间接频率合成(PLL)方法相比,它具有很多优点:频率切换时间短、频率分辨率高、相应变化连续、容易实现对输出信号的多种调制等。

直接数字频率合成是基于奈奎斯特抽样定理和数字波形合成原理而发展起来的一种数字化的频率合成技术。

DDS的基本原理是利用采样定理,通过查表法产生波形。

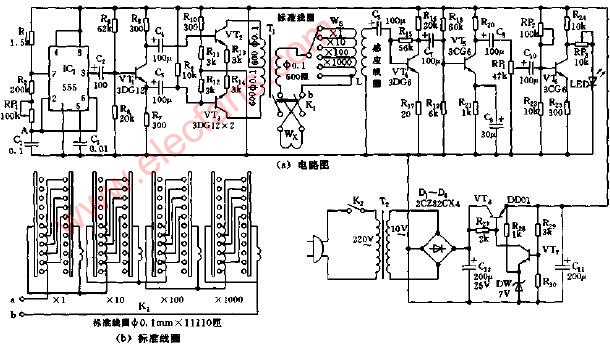

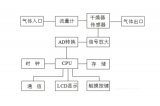

DDS的结构有很多种,其基本的电路原理如图3-1所示。

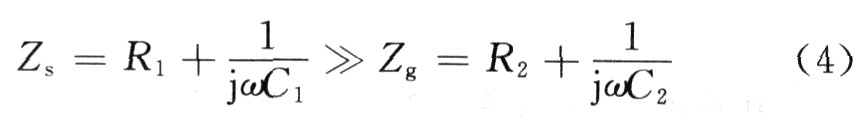

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲f s,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的

结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。

由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)

的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

DDS在相对带宽、频率转换时间、高分辨力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。

DDS的实现方法有以下几种方案:1.采用高性能DDS单片电路的设计方案;2.采用低频正弦波DDS单片电路的设计方案;3.自行设计的基于FPGA芯片的设计方案;在对DDS性能要求不苛刻、控制要求灵活的应用场合,优先选用基于FPGA设计的DDS电路;在需要的频率点很多,特定频率时谐波失真要求较小的场合,优先选用低频正弦波DDS单片电路;而在对输出信号性能要求高的场合,则优先采用采用高性能DDS单片电路,这样可以减小设计和调试难度。

而基于本系统的宽频带、分辨率高的设计要求,采用高性能DDS单片电路的设计方案。

电子发烧友App

电子发烧友App

评论