为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 14342

14342

我们在使用示波器的时候,要想稳定的显示波形,我们往往需要选择一个合适的触发方式。而在功率测量领域,如何实现“电压”和“电流”的同步测量至关总要,今天我们就来揭秘周立功致远电子是如何来实现功率测量的“神同步”!

2015-07-22 16:30:56 3013

3013

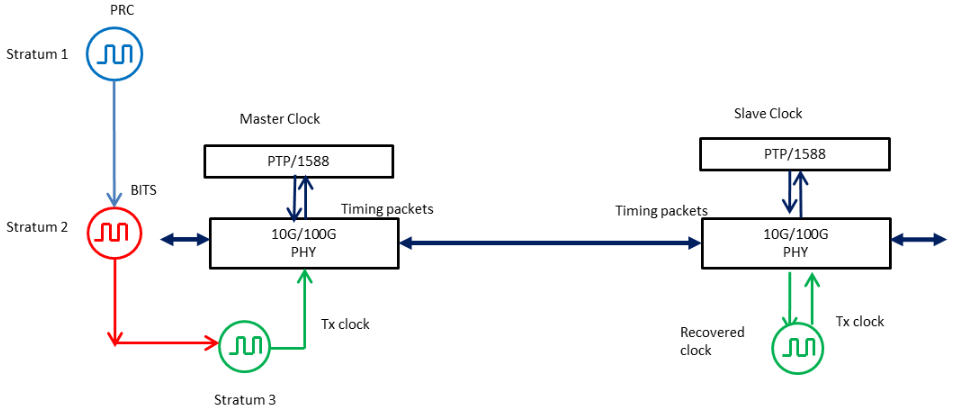

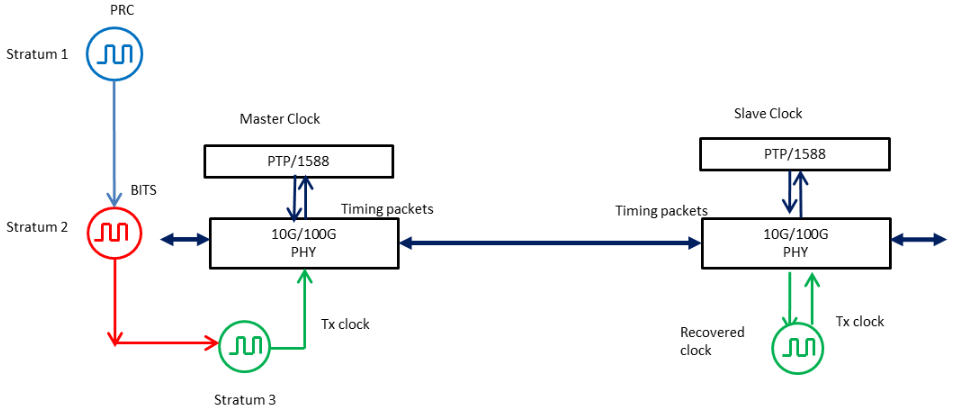

同步以太网是一种采用以太网链路码流恢复时钟的技术, 简称SyncE。同步以太网通过从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。但SyncE不能提供时间同步。

2020-05-12 09:24:02 1945

1945

学习STM32的同学知道,STM32有好多时钟,如32.768Khz,8Mhz,被时钟树搞迷糊了,下面一一解析。HSE:高速外部时钟信号(4--16Mhz常用的为8Mhz)HSI:高速内部时钟信号

2017-04-27 16:34:26

其他时间源。同步时钟服务器能够精确测量到不同设备的时间偏差,并能够自动校准时间,使得整个网络中的时间保持同步。这种设备不仅在通信和计算机领域得到广泛应用,而且在现代工业生产、安防监控等领域也大受欢迎

2023-04-14 13:36:20

请教各位,同步源和PLL源有什么异同,它们的作用是什么?

2021-04-29 06:16:23

同步源和PLL源有什么异同?作用是什么?

2021-05-07 06:17:21

工作。唯有通过参考时钟来同步这样的“对表操作”,才能让它们步调一致,从而紧密连接形成网络。

对于参考时钟,它首先要确定一个参考源,然后再是不同节点之间的同步关系。在通信系统中,一般来说精度较低的节点

2023-05-10 17:09:50

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

利用9401测量频率,采用“隐式测量”,可以测量,但是采样率与信号频率一致。现在希望可以自己设定采样率,所以必须要设置成“采样时钟”但是设置成采样时钟后,必须要提供“外部时钟”(测量频率必须要提供

2017-04-12 23:48:44

,这个选通信号也可以称为源同步时钟信号。源同步时钟系统中,数据和源同步时钟信号是同步传输的,我们保证这两个信号的飞行时间完全一致,这样只要在发送端的时序是正确的,那么在接收端也能得到完全正确的时序。整个

2014-12-30 13:54:22

处于正常工作的状态)。比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。解析STM32的时钟树[hide][/hide]

2011-10-21 14:36:05

您好:ADRF6602的参考时钟源能给我一个推荐型号或是哪个公司的吗?我找了好久都没找到峰峰值1V,最大功率13DBM的晶振。

2019-03-08 09:05:31

)。我还使用V5中的PLL_base而不是DCM_base进行了一些测试。这比我的DCM产生更多的位错误。但在我的PLL设计中,我使用了源同步(我不知道为什么,一位同事把它放在我的代码中,我不知道他

2020-06-15 15:27:25

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

我正在使用带有两个内部源和组合器的N5241A PNA-X进行IMDx测量;端口1是输入,端口2是输出。我在DUT输出端测量相对于载波的IM3,在音调功率对话框中输出音调功率设置为-5dBm;我还将

2018-12-13 16:54:52

RTC是什么?RTC工作过程是怎样的?RTC的时钟源来源有哪些?如何选择RTC的时钟源?

2021-09-29 09:18:39

STM32中定时器的时钟源是什么?

2021-11-24 06:22:09

一、在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①HSI是高速内部时钟,RC振荡器,频率为8MHz。②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。③LSI是低速内部时钟,RC振荡器,频率...

2021-08-13 07:24:19

:时钟频率速度,英语:clock rate),是指同步电路中时钟的基础频率,它以“若干次周期每秒”来度量,量度单位采用SI单位赫兹(Hz)。它是评定CPU性能的重要指标。一般来说主频数字值越大越好...

2021-08-18 07:21:56

用时钟源来产生时钟!在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①、HSI是高速内部时钟,RC振荡器,频率为8MHz。②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者

2021-08-19 06:49:53

在学习STM32的过程中,一个需要我们理解的知识点就是时钟STM32的时钟源有4个:HSL :内部高速时钟源HSE:外部高速时钟LSl:低速内部时钟LSE:低速外部时钟STM32输入时钟源1.1

2021-08-19 07:06:25

一、综述:1、时钟源在 STM32 中,一共有 5 个时钟源,分别是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。 ①HSI 是高速内部时钟, RC 振荡器,频率为 8MHz

2021-08-23 06:24:59

在看u***,书上说u***数据包的同步域可以同步主机端和从机端的时钟,这个怎么理解u***接口没有时钟线,我又想到了单片机串口的波特率,不知道有没有关系,向大家请教了这个简单的问题,很想知道答案

2019-07-02 18:06:13

就是时钟同步,计数器输出脉冲和数字I/O口接受脉冲数据同时进行,如何将计数器通道的时钟作为数字通道的时钟源啊?同时数字通道中还有触发,触发的时钟源也是计数器的时钟 如图中所示,这是别人做的,但是我

2015-01-14 11:26:01

对stm32时钟源的进一步理解stm32中五个时钟源的介绍HSI 是高速内部时钟,RC 振荡器,频率为 8MHz。HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz

2021-08-18 07:45:18

stm32时钟源1.HSI high speed internal,即高速内部时钟,时钟频率约为8Mhz,因为是由RC振荡器产生,所以不稳定。2.HSE High Speed External

2021-08-20 08:07:15

stm32可选的时钟源在STM32中,可以用内部时钟,也可以用外部时钟,在要求进度高的应用场合最好用外部晶体震荡器,内部时钟存在一定的精度误差。准确的来说有4个时钟源可以选分别是HSI、LSI

2021-08-18 07:32:05

源同步输入的1080P视频信号,148.5M时钟,从fifo写入端输入。读出端时钟采用50M主时钟经2级DCM产生148.5M的时钟clkfx。然后输出到pad给下级器件。请问此方案是否合理?疑问是输出时序如何确定?调整?器件选用spartan3 1400a。希望***下

2015-01-21 14:20:53

你好社区, 当SAI子块时钟源与另一个子块处于同步从动模式时,它是否重要?换句话说,两个子块是否应该具有相同的时钟源?谢谢。以上来自于谷歌翻译以下为原文 Hello Community, Does

2019-07-18 08:00:32

为什么功率测量需要时钟?同步源是什么?

2021-05-11 06:39:23

的 。 那么为什么FREERTOS 不是用SYSTIMER 做TICK的时钟源呢? 或者我对这几个时钟的作用理解是否还存在误区。 能帮解答一下吗?

2023-02-20 06:28:24

如图所示:左侧两个寄存器中没有DATA1和DATA2啊之前看网站举办过关于源同步的沙龙,求大神帮忙解答一下!!!

2015-01-26 14:07:42

一个紧密同步的仪器中。图1.一个ADALM1000 SMU通道的框图。所述ADALM1000处于其心脏一个源测量单元,但它也可以被看作是一个独立的示波器和函数发生器。但是,由于输出功能(发生器)和输入

2018-10-24 10:34:08

我正在使用由计时器触发的注入转换来测量缓冲电压。如参考手册中所述,我已将 ADC 的频率限制为 F_adc < F_adc_hclk/4。当我使用同步时钟

2023-01-04 07:11:27

,这个接口是不是读FD的数据的时钟啊?就一个输入时钟,它同步到底是和谁同步?异步是与谁异步?我理解的意思是:同步就是读和写的速度一样,异步就是不一样,要注意它到底能缓存多少,最终的速率是否满足。我只要

2016-12-15 10:34:51

STM32F103学习笔记四时钟系统本文简述了自己学习时钟系统的一些框架,参照风水月1. 单片机中时钟系统的理解1.1 概述时钟是单片机的脉搏,是单片机的驱动源用任何一个外设都必须打开相应的时钟不使

2021-08-12 08:06:09

性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。在FPGA中,同步信号、异步信号和亚稳态的理解PGA(Field-Programmable Gate Array),即现场

2023-02-28 16:38:14

一、综述: 1、时钟源在 STM32 中,一共有 5 个时钟源,分别是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。①HSI 是高速内部时钟, RC 振荡器,频率为 8MHz

2021-08-18 07:56:26

—————————————————————————————————————————————————————————在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。 其实是四个时钟源,如下图所示(灰蓝色),PLL是由锁相环电路倍频得到PLL时钟

2021-08-23 07:54:07

一、综述:1、时钟源在 STM32 中,一共有 5 个时钟源,分别是 HSI 、 HSE 、 LSI 、 LSE 、 PLL 。①HSI 是高速内部时钟, RC 振荡器,频率为 8MHz ;②HSE

2021-08-18 06:00:53

一、在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。①HSI是高速内部时钟,RC振荡器,频率为8MHz。②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率

2021-08-06 09:01:16

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

1、源同步接口设计之master篇源同步接口在设计中十分常见,例如SPI接口,async NAND FLASH接口。这类接口的时钟由master生成,并经过IO发送到slave中。对master

2022-06-21 17:38:18

如何利用大功率数字源表构建多源测量单元系统?

2021-05-14 06:11:56

在串行数据传输的过程中,如何在FPGA中利用低频源同步时钟实现LVDS接收字对齐呢?

2021-04-08 06:39:42

我最初在错误的论坛上发布了这个,我无法编辑它 - 可能是因为我太新了。如果你再看到这个,我道歉。大家好 - 我有一个设计,我需要读取源同步DDR数据与500MHz时钟,所以1GHz比特率。时钟到达

2020-08-14 08:46:30

我想知道如果 STM 和 FTM 共享相同的时钟源,如何检查它们之间的漂移。

我假设,由于时钟源配置树,STM 和 FTM 定时器之间的同步不能保证所有可用配置(例如:STM 的时钟源来自 CORE PLL,FTM 来自 FIRC 或 PERIPH PLL)

我的假设正确吗?

2023-05-22 08:32:38

【追踪嫌犯的利器】定位技术原理解析(4)

2020-05-04 12:20:20

在SDRAM的代码中,有的模块工作频率50MHz,有的100MHz,不同时钟域间的数据同步太难理解了,请各位前辈指点。代码如下所示。//同步SDRAM初始化完成信号always @(posedge

2023-09-12 20:39:18

微波作为无线和传输设备的重要接入设备,在网络设计和使用中要针对接入业务的类型,提供满足其需求的时钟同步方案。当前阶段,微波主要支持的时钟同步类型包括:GPS,BITS,1588,1588

2019-07-12 07:46:39

`手机通信原理解析:第 1 章 无线通信原理第2 章 移动通信系统第3 章 移动通信系统的多址接入技术第4 章 移动通信系统的语音编码第5 章 GSM移动通信系统的数字

2011-12-14 14:31:20

子系统部分射频子系统部分就是实现各种尤源互调测量功能的组件,包括正向和反射接收频段互调测量,正向发射频段互调测量,反向互调测量,跨频段互调测量,谐波测电,多载频互调测量,大功率稳定性测量和大功率合成系统

2017-11-14 14:47:20

子系统部分射频子系统部分就是实现各种尤源互调测量功能的组件,包括正向和反射接收频段互调测量,正向发射频段互调测量,反向互调测量,跨频段互调测量,谐波测电,多载频互调测量,大功率稳定性测量和大功率合成系统等

2017-11-15 10:36:31

我对使用源同步时钟将大量数据从一个FPGA移动到另一个FPGA感兴趣。但由于设计的性质,我没有很多可用的PLL,因此我无法发送许多时钟数据对。假设所有迹线具有相同的延迟,是否可以将一个源同步时钟与多个数据线相关联?非常感谢你

2020-08-07 09:14:30

氮化镓功率半导体技术解析基于GaN的高级模块

2021-03-09 06:33:26

本篇文章为永磁同步电机谐波电流注入控制策略原理解析及仿真教程目前关于此方向的资源教程较少,我个人对其进行了原理总结,仿真实验分析希望大家有所收获,喜欢本篇文章的话点个关注收藏赞吧!!!!!!永磁

2021-06-30 06:16:44

。 1 电力系统时间同步概况 目前,电力系统中的时间同步处于变电站内GPS统一的状态,甚至有很多老旧变电站还没有实现GPS统一,需要对时的每套设备都配置一套独立的时钟系统。由于GPS设备

2012-10-18 10:20:47

E4418B功率计上执行了这些测量,并使用手册中调出的方法计算出它为0.981 mW,这意味着我需要调整功率参考以满足规范。但是,当我测量功率参考时。使用E4419B和功率传感器,我的读数为1.001

2019-07-26 14:29:45

大家好,又到了每日学习的时候了。今天我们来聊一聊异步电路中的时钟同步处理方法。既然说到了时钟的同步处理,那么什么是时钟的同步处理?那首先我们就来了解一下。时钟是数字电路中所有信号的参考,没有时钟或者

2018-02-09 11:21:12

我已经尝试了一些使用计数器的UDB组件,但看起来它们与ButhLoCH同步。我们的应用需要一个异步时钟,因为数字PLL通常会产生太多的抖动(或者相反地,我们可能想要运行一个慢速的系统总线来节省功率

2019-09-11 11:33:23

IEEE 1588标准诞生于2002年,主要定义网络分布式时钟的同步协议。测试与测量、电信和多媒体流处理等许多不同应用,都开始首选这种时钟同步方法。这种标准化时钟同步法成本效益高,支持异构系统,并可提供纳秒级同步精度。

2019-11-01 06:07:58

在介绍了GPS 同步时钟基本原理和FPGA 特点的基础上,提出了一种基于FPGA 的GPS同步时钟装置的设计方案,实现了高精度同步时间信号和同步脉冲的输出,以及GPS 失步后秒脉冲的平

2009-07-30 11:51:45 40

40 高精度时钟同步芯片高精度时钟芯片典型应用场景:·核心网路由器、交换机·同步以太网设备·电信级边界时钟(T-BCS)和从时钟设备(TimeSlave)·高速以太网端口设备·时钟时间源设备BITS、时间

2023-12-29 09:37:02

基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 2890

2890

同步网时钟及等级

基准时钟 同步网由各节点时钟和传递同步定时信号的同步链路构成.同步网的功能是准确地将同步定时信号从基

2010-04-03 16:27:34 3661

3661 虚拟存储器部件原理解析

2010-04-15 14:25:20 2909

2909 触摸屏的应用与工作原理解析

2017-02-08 02:13:17 38

38 分享到:标签:嵌入式; 同步时钟 同步时钟系统是同步设备中实现同步通信的核心,因此,要实现数字同步网的设备同步就要求同步时钟系统一方面要能提供精确的定时同步,另一方面还要能方便实现网络管理中心对同步

2017-11-04 10:21:44 6

6 时钟同步是分布式系统的核心技术之一,为实现基于ARM-WinCE嵌入式系统平台的测试仪器组建分布式测试系统,在介绍IEEE1588精确时钟协议基本原理的基础上,提出了使用具有IEEE1588协议硬件

2017-11-28 10:56:07 9

9 微波作为无线和传输设备的重要接入设备,在网络设计和使用中要针对接入业务的类型,提供满足其需求的时钟同步方案。当前阶段,微波主要支持的时钟同步类型包括:GPS,BITS,1588,1588

2017-12-07 20:51:01 559

559 现在的硬件设计中,大量的时钟之间彼此相互连接是很典型的现象。为了保证Vivado优化到关键路径,我们必须要理解时钟之间是如何相互作用,也就是同步和异步时钟之间是如何联系。 同步时钟是彼此联系的时钟。

2018-05-12 10:15:00 19562

19562 我们系统中,主板与从板之间通过交换网片的HW0、HW4互连,要使主板与从板的交换网之间能够正常交换,必须使这两个交换网片有一致的帧同步时钟及位同步时钟。在现在的单板中,从板的时钟由主板直接送出。整个系统采用的时钟源有3种方式:

2018-10-30 11:36:23 7

7 同步相量测量装置(PMU:phasor measurement unit)是利用全球定位系统(GPS)秒脉冲作为同步时钟构成的相量测量单元。可用于电力系统的动态监测、系统保护和系统分析和预测等领域.是保障电网安全运行的重要设备。目前世界范围内已安装使用数百台PMU。

2019-11-25 09:21:02 38951

38951 本发明提供了一种将异步时钟域转换成同步时钟域的方法,直接使用同步时钟对异步时钟域中的异步写地址状态信号进行采样,并应用预先设定的规则,在特定的读地址位置对同步时钟域中的读地址进行调整,使得在实现

2020-12-21 17:10:55 5

5 在UWB定位系统中,TDOA定位算法那的优势明显。我们知道TDOA算法中需要测量UWB信号的到达时间差。如果说TDOA定位的前提是需要测量到达时间差,那么测量到达时间差的前提就是时间需要同步一致

2021-09-26 15:14:44 9908

9908 解析MSP430系统时钟资源

2021-09-26 11:39:09 1

1 异步复位,同步释放的理解目录目录 同步复位和异步复位 异步复位 同步复位 那么同步复位和异步复位到底孰优孰劣呢? 异步复位、同步释放 问题1 问题2 问题3 问题4 问题5 参考资料同步

2022-01-17 12:53:57 4

4 史密斯圆图和阻抗匹配原理解析

2022-11-02 20:16:23 1620

1620 什么是晶振 晶振工作原理解析

2022-12-30 17:13:57 3726

3726

时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 两个机器的时钟怎么同步? 在现代社会中,时间同步对于各种科学研究、工业生产和通信技术都具有重要意义。在许多应用程序中,如分布式系统、计算机网络和数据同步等领域,为了确保数据的一致性和准确性,需要确保

2024-01-16 14:26:32 254

254 时钟同步怎样组网? 时钟同步是计算机网络中的重要问题,主要用于确保在多个节点之间保持时间的一致性。时钟同步对于网络的可靠性和性能至关重要,因此组网时时钟同步必须仔细考虑。 在计算机网络中,各个节点

2024-01-16 15:10:13 168

168 忽视,因为5G网络具有更高的速率和更低的延迟需求,网络时钟同步可以实现更有效和准确的数据传输和通信。 首先,让我们理解一下网络时钟同步的基本原理。计算机网络中使用的时钟体系主要有两种,分别是物理时钟和逻辑时钟。物理

2024-01-16 16:03:23 227

227 网络时钟同步有哪些要求?要注意哪些问题?如何在5G网络中测试时间与时钟同步? 网络时钟同步是指在计算机网络中,各个时钟节点之间通过协议和算法进行时间的同步,以确保网络中的各个设备拥有相近的时间,从而

2024-01-16 16:03:25 276

276

电子发烧友App

电子发烧友App

评论