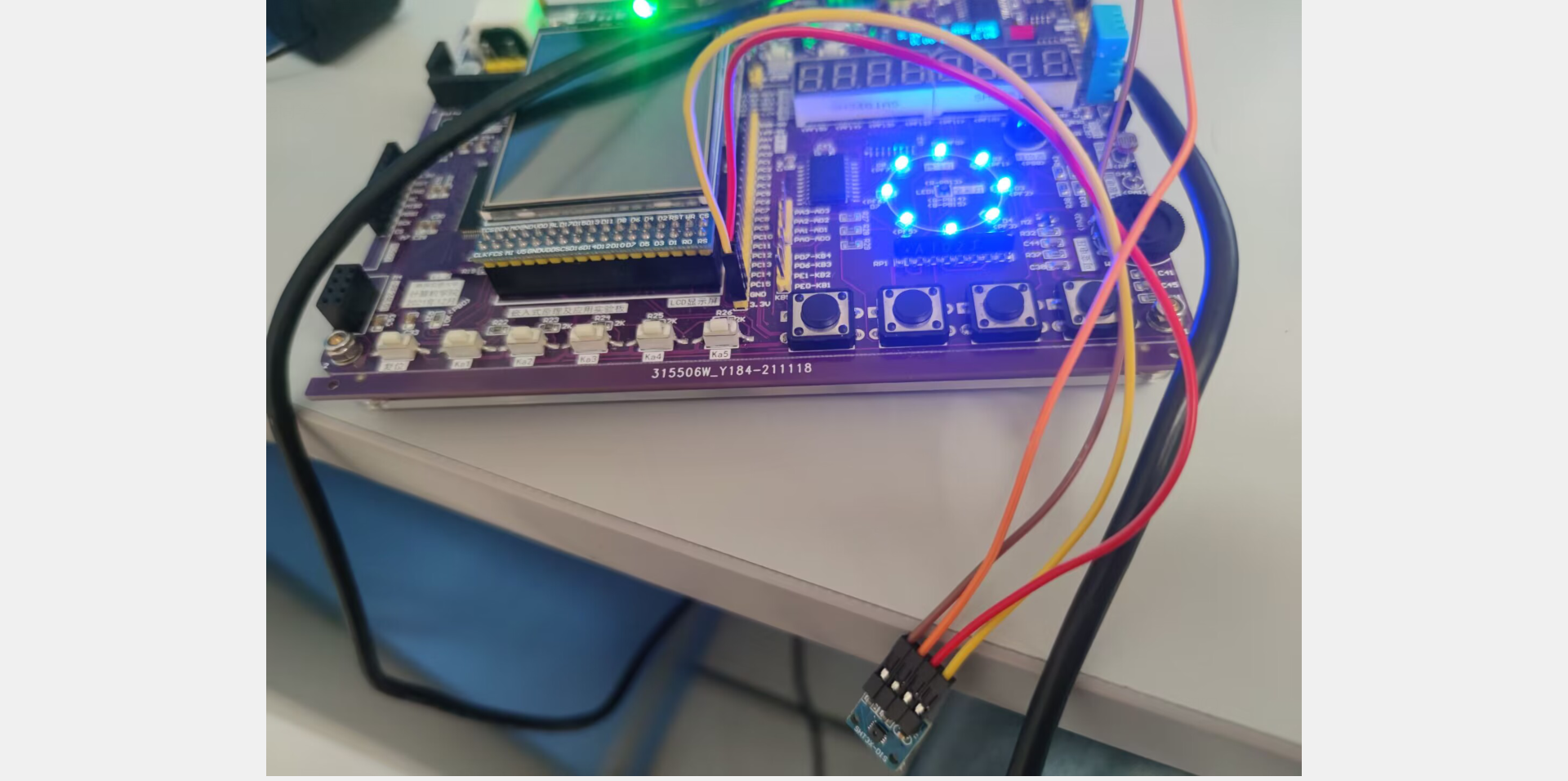

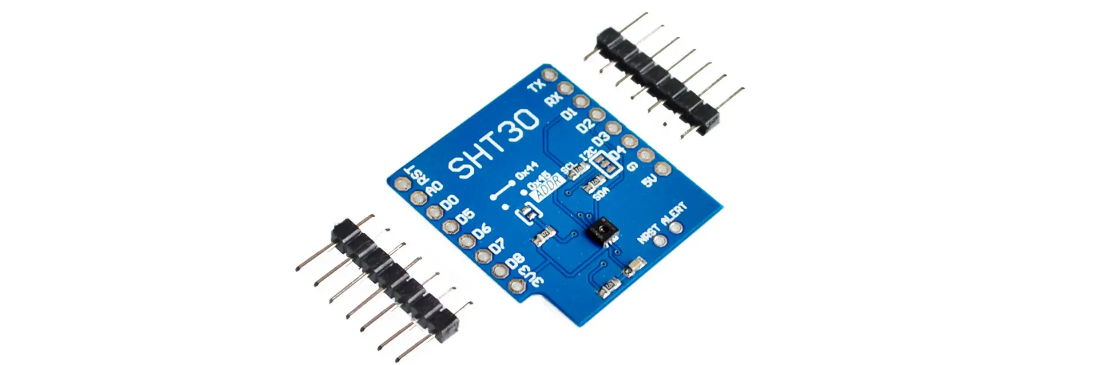

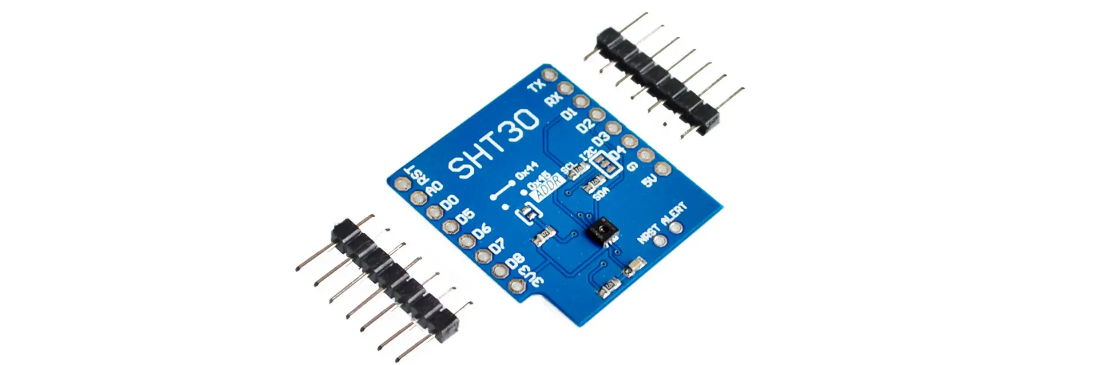

当前介绍基于STM32F103ZCT6芯片设计的环境温度与湿度检测系统设计过程。当前系统通过SHT30温湿度传感器采集环境温度和湿度数据,并通过模拟IIC时序协议将数据传输到STM32芯片上。然后

2023-06-20 09:16:57 1210

1210

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期

2020-11-25 11:03:09 8918

8918

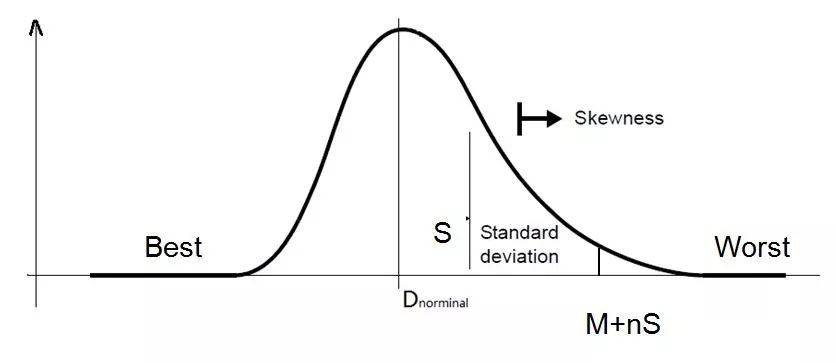

时序分析是FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 在本项目中,使用了51单片机作为主控芯片,SHT30传感器作为温湿度传感器,LCD显示屏作为数据显示模块。通过51单片机的GPIO口模拟IIC通信协议,实现了与SHT30传感器的数据通信。

2023-06-19 09:02:51 1580

1580

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 490

490

0.96寸4针IIC OLED显示模块

2023-04-06 21:56:22

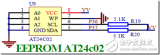

51模拟IIC时序,读写访问AT24C02,STM32操作类似

2022-03-01 06:33:03

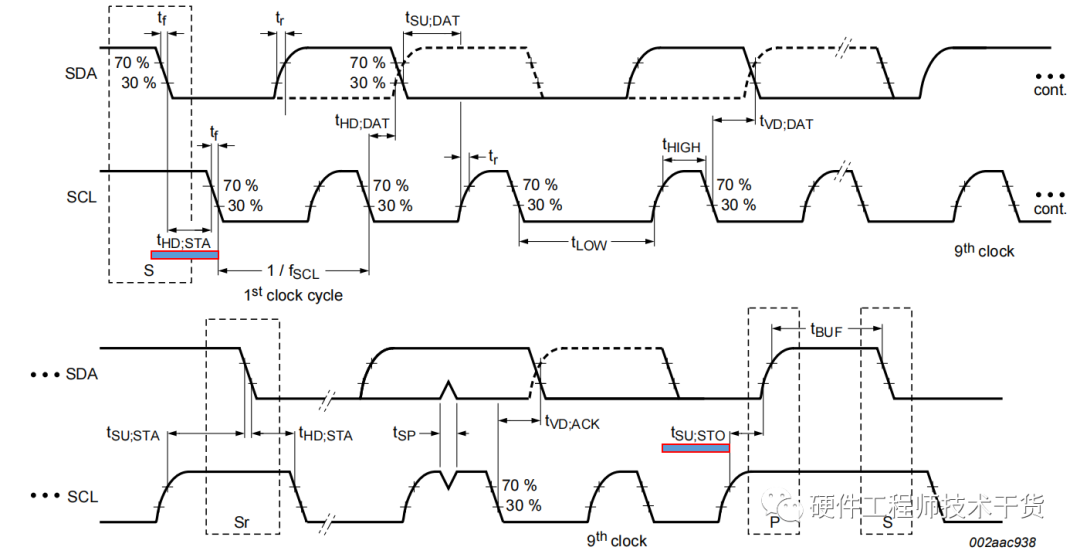

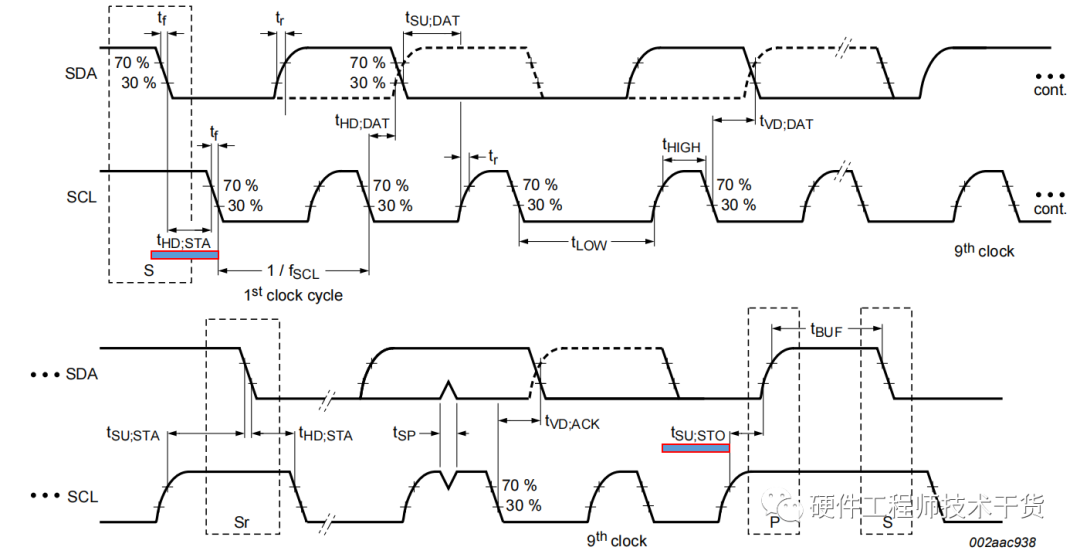

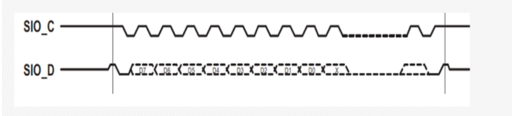

IIC时序理解IIC 的特征:两条总线:串行数据总线(SDA)和串行时钟总线(SCL)数据有效性规定:IIC总线在进行数据传输时,SCL在高电平区间,SDA上的电平必须保持稳定SDA的数据的高或者

2022-01-07 06:05:52

IIC协议分析

2020-04-30 15:49:10

配合实现,传输速率包含标注准(100kps)、快速(400kps)、高速(3.4Mbps)三大类。2. IIC总线时序启动时序:当SCL为高电平时,SDA下降沿,表示启动。...

2021-11-29 06:20:06

按照IIC时序编写的程序

2017-11-05 20:37:44

IIC的使用IIC相关IIC开始/结束 信号IIC数据有效性(位传输)IIC响应信号IIC写数据地址控制字写操作协议示例IIC读数据示例IIC相关IIC开始/结束 信号开始和停止时序,如上图

2022-01-07 08:29:06

了IIC的一些定义后,要想写代码必须知道它的时序。一、空闲状态,IIC在空闲状态时SDA和SCL都是处于高电平。二、开始信号,当SCL电平不发生变化的时候,SDA由高电平变为低电平的这一个过程...

2022-02-23 06:07:18

玩单片机的朋友都知道IIC通信这个工具,但好多人只是会用,内部的原理不求甚解,或是想要了解其原理,但却对抽象的时序描述一头雾水。本文将从实测的IIC波形入手,带你看到真实的IIC样子,进而去理解

2022-02-24 06:01:06

spurious scl transition detected at有人知道这是什么问题么?仿真的时候全是这个 用的pcf8563。还有,一样的方式,读取秒分时,到小时没有发送,时序有偏移什么的??实在是无从下手啊? 大家有建议类的书籍么?

2017-01-06 09:32:34

这种时序图第一次见,不会分析。1.希望技术支持或者哪位大神从编程的角度分析一下这个时序。2.上面的线为什么是曲线,代表什么意思?3.CLK正负的产生源可否是由DSP的引脚产生,经反相器,通过电容,形成两路互补的信号?附件图像 1.png35.7 KB

2018-12-03 09:15:27

DAC时序分析

2021-07-29 09:14:26

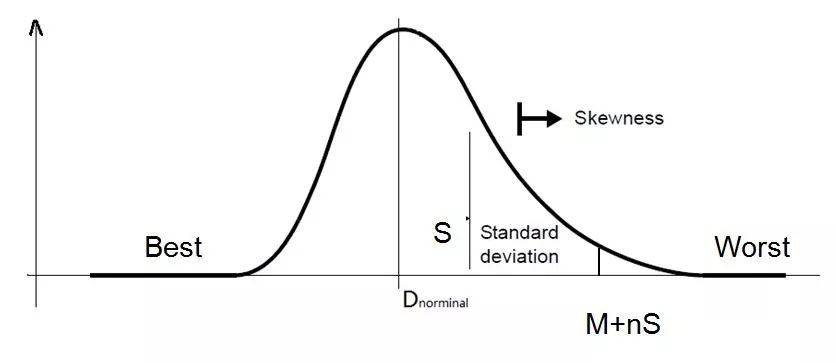

FPGA时序分析系统时序基础理论对于系统设计工程师来说,时序问题在设计中是至关重要的,尤其是随着时钟频率的提高,留给数据传输的有效读写窗口越来越小,要想在很短的时间限制里,让数据信号从驱动端完整

2012-08-11 17:55:55

FPGA时序分析与约束(2)——与门电路代码对应电路模型的时序分本文中时序分析使用的平台:quartusⅡ13.0芯片厂家:InterQuartesⅡ时序分析中常见的时间参数:Tclk1:时钟从时钟

2021-07-26 08:00:03

FPGA时序相关的资料。都看完看懂时序就没问题了。分了三个附件:第一个是通过一些例子教你如何搞定时序分析。第二个附件是网上各种大神们对时序的理解,主要是他们的博客链接以及网站链接。第三个是其他的一些零散的关于时序的资料。

2012-11-12 17:45:28

水平放置,移动为垂直放置,传感器需要延迟5秒~30+秒后,传感器的加速度数据才会变化。请问这是正常指标吗?还是哪个地方未正确操作。

采用IIC总线,每1秒读取一次传感器加速度数据(XYZ)。传感器

2024-03-21 07:48:01

的128*64的OLED显示屏为例。下图为OLED的外观图。二、SSD1306芯片的IIC时序图这里我们需要看清楚START信号和STOP信号。关于时间,芯片的数据手册也有说明。...

2022-02-18 07:09:46

IIC时序网上一搜一大把,我就不在这里啰***程序已经配置好了,只需要修改一下引脚就可以使用。这里强调一下,这里面的delay延时函数用的SysTick定时器,延时比较精确。具体配置可以看一下

2021-12-08 08:21:16

STM32软件模拟IICIIC硬件连接模拟I2C 的GPIO配置IIC协议模拟IIC时序函数IIC写一个字节函数的debug介绍IIC的两篇博客,(最后都是读取AT24C02)介绍IIC时序的博客

2022-01-19 07:49:21

自己做了一个工程,静态时序分析的结果CLK信号的SLACK是负值(-7.399ns),书上说该值是负值时说明时序不对,但是我感觉时序仿真的结果是对的。是不是时序仿真波形正确就不用管静态时序分析的结果了?请高手指点

2010-03-03 23:22:24

如题:fpga时序分析一般都做哪些分析我自己研究时序分析也有一段时间了 ,从理论到altera的timequest,差不多都了解了 ,但就是不知道一个具体的项目都要做哪些约束。求大神知道,或者有没有这方面的资料(网上资料基本都看过了,没有说明具体项目的)。

2012-10-22 22:20:32

转自:VIVADO时序分析练习时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里

2018-08-22 11:45:54

什么是时序分析?时序约束的作用是什么?FPGA组成的三要素分别是哪些?

2021-09-18 06:05:51

单片机IIC通信中EEPROM时序分析总结根据时序,一步一步写代码,比如说写字节1是S表示开始Start,后面依次看时序代码中涉及到的0Xa0,0Xa1需要讲解一下,我们知道EEPROM是8位的器件

2022-01-07 07:40:01

各位,我想知道怎么根据这些时序参数来确定IIC启动或者读写数据的时候延时多少啊,我看网上很多程序都是4us这个不适用吧

2018-11-21 10:16:12

本文将要讲解和实现的内容主要分为两个部分:代码实现IIC接口管理、代码实现IIC时序。IIC接口管理接口管理的目的是想在后期扩展时,一个工程里可使用多个IIC接口。这里暂不考虑使用复杂的数据结构

2020-01-04 07:00:00

以下针对目前项目所用到的SRAM时序进行分析,同时也对SRAM应用在STM32F4上进行详细解说。以此也可以类推出NAND/PSRAM等时序的应用技巧。时序当前用到的是模式A,其中读时序如下。图片截

2022-01-07 07:20:20

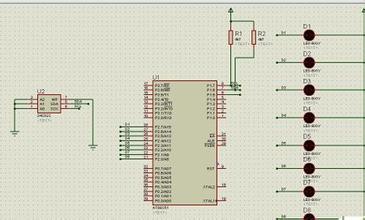

一、实验目的:通过单片机普通IO口,模拟IIC时序,掌握IIC通讯协议。二、实验用到的主控芯片:STM32F103RCT6,IIC通讯引脚IIC_SDA:PC11,IIC_SCL:PC12三

2022-02-17 06:30:09

OLED的主要优点有哪些呢?模块IIC协议时序和时间要求分别有哪些呢?

2022-01-21 07:42:36

本帖最后由 alasga 于 2016-1-30 15:56 编辑

附件有3部分:1、时序分析基本模型;2、如何设计好的时序;3、整体的时序策略。

2016-01-30 15:52:57

今天调试板子eeprom的时候遇见一个很奇怪的问题:上电后发现eeprom写不进去,然后我将IIC的两根线和GND飞线出来接到逻辑分析仪上,一上电eeprom正常读写,逻辑分析仪看时序没有问题。但是

2021-05-10 19:09:19

我用软件模拟IIC时序,用逻辑分析仪做出的波形见下图;在AT24C08EEPROM的8地址上,写入182,波形貌似没什么问题,但就是读出来的都是0,能否帮我看一下哪里出问题了?谢谢了。

2016-07-10 09:48:52

请教如何做时序分析

2013-06-01 22:45:04

在使用CH341 USBIOX.DLL 做上位机控制,读取MCU的IIC 从机时,发现IIC读取数据时序时,在读取ACK或者发送ACK后,下一个时钟周期立刻开始读取从机数据.因为8位MCU作为从机

2022-07-13 07:20:25

请问下CH579 引脚模拟的IIC时序,读取数据 逻辑分析仪抓取的数据是正常的,但是串口打印出来全是0?调了好几天,一直没找到是哪里的问题,还请大佬们帮忙解决下,或者有提供相关参考的历程参考下 ,谢谢

2022-08-30 07:04:33

用的是ADS1110,模拟的IIC时序,发现读数偏小,经过仔细寻找原因发现是读取字节数据的最高位恒为0,配置字写为0xff,读出来是0x7f,写0x8c,读出来是0x0c。望各位高手帮忙分析一下,不胜感激!!!

2019-06-10 22:48:14

时序的,本文采用的是模拟时序,下篇文章就介绍配置STM32的IIC硬件时序读写AT24C02和AT24C08。模拟时序更加方便移植到其他单片机,通用性更高,不分MCU;硬件时序效率更高,单每个MCU配置方法不同,依赖硬件本身支持。目前器件: 采用AT24C02 EEPROM存储芯...

2021-12-08 06:27:13

时序的,上篇文章已经介绍了采用IIC模拟时序读写AT24C02,这篇文章介绍STM32的硬件IIC配置方法,并读写AT24C08。文章地址:https://xiaolong.blog.csdn.net/article/details/117586108模拟时序更加方便移植到其他单...

2021-11-30 07:48:38

静态时序分析STA是什么?静态时序分析STA的优点以及缺点分别有哪些呢?

2021-11-02 07:51:00

高速电路的时序分析电路中,数据的传输一般都是在时钟对数据信号进行有序的收发控制下进行的。芯片只能按规定的时序发送和接收数据,过长的信号延迟或信号延时匹配不当都会影响芯片的建立和保持时间,导致芯片无法

2012-08-02 22:26:06

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一次的连载中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份时序分析的案

2010-04-05 06:37:13 0

0 时序约束与时序分析 ppt教程

本章概要:时序约束与时序分析基础常用时序概念QuartusII中的时序分析报告

设置时序约束全局时序约束个别时

2010-05-17 16:08:02 0

0 静态时序概念,目的

静态时序分析路径,方法

静态时序分析工具及逻辑设计优化

2010-07-09 18:28:18 129

129 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

69 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这

2010-09-15 10:48:06 1461

1461

讨论了静态时序分析算法及其在IC 设计中的应用。首先,文章讨论了静态时序分析中的伪路径问题以及路径敏化算法,分析了影响逻辑门和互连线延时的因素。最后通过一个完整的IC 设计

2011-12-20 11:03:16 95

95 24C02中IIC总线的应答信号(ACK)时序图分析,很好的单片机学习资料。

2016-03-21 17:30:06 93

93 _静态时序分析(Static_Timing_Analysis)基础及应用[1]。

2016-05-09 10:59:26 31

31 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 静态时序分析基础及应用

2017-01-24 16:54:24 7

7 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

AT24C02是由ATMEL公司提供的,IIC总线串行EEPROM(electronic eraser programmer read only memory),其容量为2kbit(256B),工作电压在2.7v“5.5v之间,生产工艺是CMOS。

2017-11-16 14:29:04 11599

11599

时序分析基本概念介绍——STA概述,动态时序分析,主要是通过输入向量作为激励,来验证整个设计的时序功能。动态时序分析的精确与否取决于输入激励的覆盖率,它最大的缺点就是速度非常慢,通常百万门的设计想全部覆盖测试的话,时间就是按月来计算了。

2017-12-14 17:01:32 27850

27850

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

2018-04-03 15:56:16 10

10 一 IIC概念及特点

1、IIC概念

2、主要特点

二 IIC时序介绍

1、IIC总线时序

2、IIC通信过程

三 编程时使用的几个概念

1、时钟速率

2、起始条件和停止条件

2018-07-02 10:07:12 5446

5446 在之前的MCS-51系列单片机中内部没有IIC通信资源,所如果要想用51单片机实现IIC通信,就只能通过软件模拟其时序,这样也能实现IIC通信的功能。

2018-11-20 15:52:28 15925

15925

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。建立时间和保持时间是FPGA时序约束中两个最基本的概念,同样在芯片电路时序分析中也存在。

2019-12-23 07:01:00 1894

1894

静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析

2019-11-22 07:07:00 3179

3179 时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

停止条件即示波器停止“统计分析”的条件,当测试条件满足预设条件时,时序分析软件会停止统计完成分析工作。

2020-04-29 15:18:52 2425

2425 静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序分析,静态时序分析不需要测试矢量,而是直接对芯片的时序进行约束,然后通过时序分析工具给出

2020-11-11 08:00:00 58

58 本文档的主要内容详细介绍的是华为FPGA硬件的静态时序分析与逻辑设计包括了:静态时序分析一概念与流程,静态时序分析一时序路径,静态时序分析一分析工具

2020-12-21 17:10:54 18

18 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 忠告一、如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

2021-01-12 17:48:06 13

13 本文档的主要内容详细介绍的是时序分析的静态分析基础教程。

2021-01-14 16:04:00 14

14 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 3

3 本文档的主要内容详细介绍的是时序分析的Timequest教程免费下载。

2021-01-14 16:04:00 15

15 方法,能够有效减少时序路径问题分析所需工作量。 时序路径问题分析定义为通过调查一条或多条具有负裕量的时序路径来判断达成时序收敛的方法。当设计无法达成时序收敛时,作为分析步骤的第一步,不应对个别时序路径进行详细时序分

2021-05-19 11:25:47 2677

2677

华秋PCB设计分析软件-BOM坐标Gerber,一步搞定

2021-07-16 16:57:12 0

0 配合实现,传输速率包含标注准(100kps)、快速(400kps)、高速(3.4Mbps)三大类。2. IIC总线时序启动时序:当SCL为高电平时,SDA下降沿,表示启动。...

2021-11-19 18:21:06 13

13 STM32入门开发: 采用IIC硬件时序读写AT24C08(EEPROM)

2021-11-21 13:51:04 45

45 STM32F103 模拟IIC时序

2021-11-25 09:51:10 32

32 时序的,本文采用的是模拟时序,下篇文章就介绍配置STM32的IIC硬件时序读写AT24C02和AT24C08。模拟时序更加方便移植到其他单片机,通用性更高,不分MCU;硬件时序效率更高,单每个MCU配置方法不同,依赖硬件本身支持。目前器件: 采用AT24C02 EEPROM存储芯...

2021-11-25 20:06:02 39

39 IIC的使用IIC总线简介IIC通信时序IIC总线寻址IIC总线简介1、IIC总线是一种由PHILIPS公司开发的两线式串行总线2、IIC在硬件上是时钟总线SCL和数据总线SDA两条线构成3、器件

2021-12-04 16:06:09 12

12 一、实验目的:通过单片机普通IO口,模拟IIC时序,掌握IIC通讯协议。二、实验用到的主控芯片:STM32F103RCT6,IIC通讯引脚IIC_SDA:PC11,IIC_SCL:PC12

2021-12-22 18:49:11 34

34 玩单片机的朋友都知道IIC通信这个工具,但好多人只是会用,内部的原理不求甚解,或是想要了解其原理,但却对抽象的时序描述一头雾水。本文将从实测的IIC波形入手,带你看到真实的IIC样子,进而去理解

2022-01-12 17:35:17 8

8 玩单片机的朋友都知道IIC通信这个工具,但好多人只是会用,内部的原理不求甚解,或是想要了解其原理,但却对抽象的时序描述一头雾水。本文将从实测的IIC波形入手,带你看到真实的IIC样子,进而去理解

2022-01-12 17:59:22 15

15 时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095 AXI IIC 和 PS IIC 控制器都符合 NXP IIC 总线规范。用户必须确保其选择使用的从设备的时序参数与UM10204 的第 48 页上的“表 10”中的参数相同。

2022-08-25 10:29:08 1169

1169 振弦采集模块的通讯协议( IIC) IIC 通讯协议本身即是基于设备地址和寄存器的物理层通讯协议, VMXXX 使用 IIC 接口对传感器的访问,请遵循前述硬件接口时序及协议说明即可。 振弦采集模块

2022-11-17 10:02:45 515

515

最近硬件测试工程师反馈一个BUG,和IIC的时序有关,这个BUG目前没有带来使用方面的影响,但是不符合规范,要求整改。我们使用的单片机是cortex-m3内核的芯片,美信公司生产,使用此芯片读取电容

2023-06-14 17:52:31 1571

1571

引言 在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行 静态时序分析 ,即 在最坏情况下检查所有可能的时序违规路径,而不需要测试

2023-06-28 09:38:57 714

714

今天要介绍的时序分析基本概念是lookup table。中文全称时序查找表。

2023-07-03 14:30:34 665

665

今天我们介绍的时序分析概念是 **SOCV** 。也被叫作POCV,全称为 **Statistic OCV** . 这是一种比AOCV更加先进的分析模式。

2023-07-03 15:19:00 1347

1347

本文主要介绍了静态时序分析 STA。

2023-07-04 14:40:06 528

528

逻辑分析仪能读IIC信号不? 逻辑分析仪是一种常用的电子测试工具,它能够监测和分析数字电路中的信号,帮助工程师诊断问题并进行优化。IIC(Inter-Integrated Circuit)是一种串行

2023-09-19 16:50:03 740

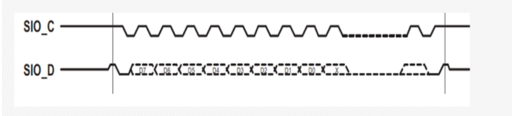

740 SCCB协议是类似于IIC协议,它常用于OV系列摄像头配置接口中。下图为sio_c和sio_d的时序图,具体的时序协议请看《SCCB接口时序.pdf》文档。

2023-11-06 10:42:28 237

237

电子发烧友App

电子发烧友App

评论