在同步电路设计中,边沿检测是必不可少的!

2012-03-01 09:59:04 4918

4918 在同步电路设计中,边沿检测是必不可少的!后一种方法所耗的资源要比前一种方法多(一个触发器),但是就可以大大提高可靠性,这绝对是物有所值!!

2012-02-01 10:53:05 894

894

这里FPGA牛人一些经验和大家分享,希望能对IC设计的新手有一定的帮助,能使得他们能少走一些弯路!

2012-03-21 10:17:49 1054

1054 当然,任何编程语言的学习都不是一朝一夕的事,经验技巧的积累都是在点滴中完成,FPGA设计也无例外。下面就以我的切身体会,谈谈FPGA设计的经验技巧。

2022-10-25 15:51:21 787

787 电子发烧友网为大家提供了IC检测经验。集成电路常用的检测方法有在线测量法、非在线测量法和代换法。

2011-10-28 11:40:06 634

634 信号都是这样,我找xilinx公司的技术人员咨询过,他们也从来没有遇到这种现像,他们说要达到这种效果得专门设计一个双边沿的触发器才行。大家都来分析分析,这到底是怎么回事!或者大家可自已去做个实验试一下,比如外部一个按键信号送入FPGA的一个口子触发一个D触发器,来看一看是不是会有同样的现像!

2012-07-17 21:46:37

FPGA CPLFPGA CPLD 数字电路设计经验分享FPGA/CPLD数字电路设计经验分享摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应

2012-08-11 10:17:18

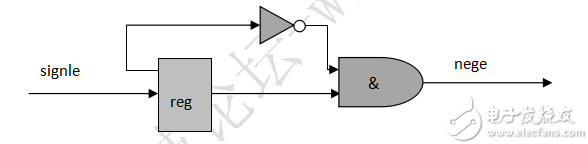

边沿监测代码常用在接口逻辑设计中,通过监测接口信号的高低电平边沿的变化控制模块中其它信号的操作;也可用在时序的实现中,通过监测时钟沿的监测信号,做出相应的逻辑操作;逻辑代码如下:`timescale

2012-05-26 10:14:47

本帖最后由 xianer317 于 2014-6-21 19:34 编辑

FPGA/CPLD数字电路设计经验分享

2014-06-21 19:33:20

FPGA经验之谈 摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型

2009-10-21 17:30:31

` 本帖最后由 eehome 于 2013-1-5 10:00 编辑

FPGA经验谈(西安大唐电信)`

2011-09-29 11:05:40

FPGACPLD数字电路设计经验分享

2012-08-07 21:46:49

FPGA_100天之旅_边沿检测

2017-09-28 13:37:44

华为FPGA关于FIFO的经验之谈!

2015-07-16 16:05:45

应用,它的优点在这里无庸赘述。从个人实用角度看,对于学生,掌握FPGA可以找到一份很好的工作,对于有经验的工作人员,使用fgpa可以让设计变得非常有灵活性。掌握了fpga的设计,单板硬件设计就非常容易(不是

2011-10-14 13:31:46

以xinlixFPGA为载体 ,实现 FPGA 对电梯异常的检测 ,并能进行显示。。。。至于后期报告 ,后面发布。。

2012-07-05 01:32:00

FPGA牛人的经验分享

2012-08-17 22:27:09

fpga经验谈

2012-08-06 14:38:33

本帖最后由 qiang6 于 2012-8-17 09:59 编辑

fpga经验谈(西安大唐电信)https://bbs.elecfans.com/forum.php?mod=viewthread&tid=266102&fromuid=483505

2012-08-17 09:49:14

fpga经验谈(西安大唐电信)

2012-08-18 07:25:33

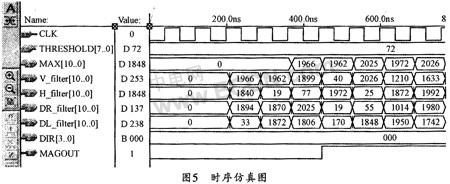

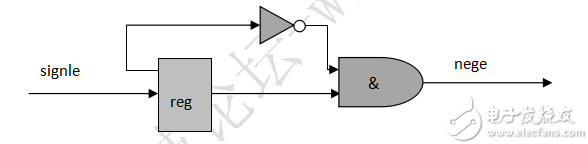

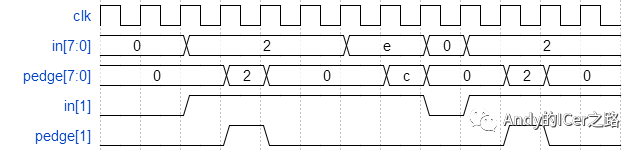

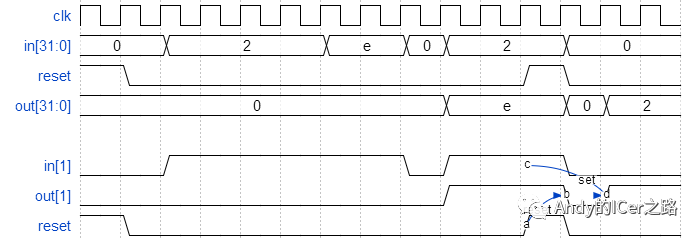

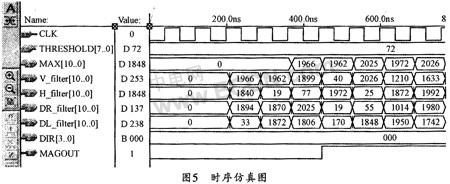

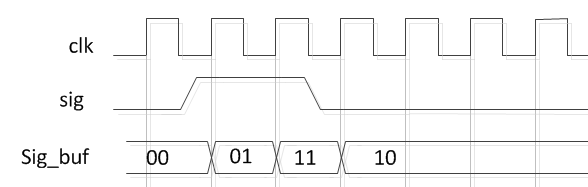

`fpga应用篇(二):边沿检测上一篇介绍了阻塞赋值与非阻塞赋值,这次我们利用非阻塞赋值产生一个简单的应用即边沿检测,边沿检测一般用来产生使能信号。程序如下:综合后电路:clk为主时钟分频之后得到

2017-04-06 21:28:08

fpga设计经验分享

2013-04-14 23:18:23

fpga高手经验谈

2012-08-20 15:23:42

边沿检测设计报告

2017-09-26 15:38:19

形成的反射就变强,将会导致位宽度失调的错误。ISO11898中只规定1M波特率下分支不超过0.3米,但是在其它情况下并没有做声明,这个便取决于现场工程师们的经验。二、消除边沿台阶边沿台阶是造成错误波形

2019-10-07 07:00:00

STM32定时器怎样通过ETR模式进行边沿检测并计数呢?如何去实现?

2021-11-24 06:51:27

请问各位大佬,stm32外部中断的边沿检测时,对上升沿或者下降沿是否有要求,必须小于或者大于多少时间,或者在多少时间内必须上升或者下降多少V才算触发。在spec中只看到了最小是10ns就可以,同时边沿检测的电平是GPIO的VIH和VIL吗?

2024-03-20 08:31:04

本帖最后由 mengyi1989 于 2019-12-7 12:40 编辑

立即学习>>梦翼师兄的FPGA实战课程众筹写在前面的话在项目设计中,我们经常需要检测信号由高到低或者由

2019-12-04 10:24:31

程序边沿检测下降沿并统计数量(数量到达2后重新计数,并发送动作信号),但是最终发现检测结果不准确,有时候能检测到,有时候检测不到。万分感谢您的解答和建议!下面是verilog代码[code]//边沿检测initial numinitial led

2021-08-21 12:58:00

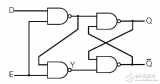

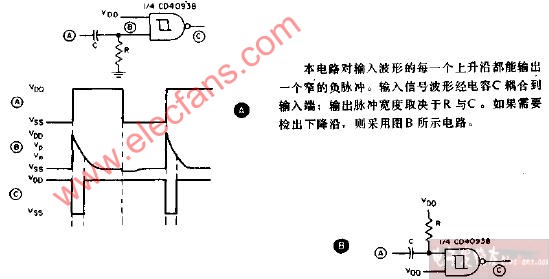

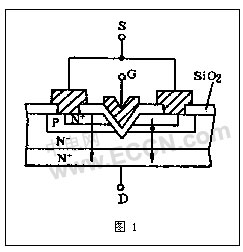

入图,有没有大神分析一下,是怎实现边沿检测的,它各个时期的电平状态是什么

2016-04-13 14:36:25

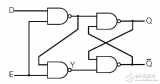

我看到网上关于边沿检测的讲解,有个地方不理解,t0时刻和t1时刻分别是怎样的时刻,trigger在时钟上升沿经过触发器输出的信号和经过非门的信号是什么样的关系?我的理解是trigger分别输出后是两个电平相反的信号,为什么相与之后就可以检测是否为上升沿或者下降沿?谢谢。

2023-05-10 14:52:22

新手入门FPGA,求入门经验{:1:}

2015-08-01 16:57:07

有谁有设计过DSP于FPGA通讯的经验,求讲解一下思路

2015-10-30 18:16:15

二极管的检测方法与经验三极管的检测方法与经验

2021-04-09 06:54:46

请求大神分享一些关于FPGA设计的学习经验

2021-04-15 06:47:08

本文分享了一些常见电子元器件的检测经验和技巧。

2021-06-07 07:08:50

电路设计[FPGA]设计经验

2012-05-23 19:49:45

电路设计[FPGA]设计经验

2012-08-20 15:37:36

电路设计[FPGA]设计经验

2019-01-03 14:19:28

1、本人现有四年的FPGA设计及测试经验,硕士学历,目前在职。 2、曾经作为某重要项目的FPGA软件负责人,项目管理经验丰富。3、熟悉xilinx芯片的底层结构,优化芯片资源以及时序约束。4、熟练

2014-01-02 11:16:50

至芯昭哥带你学FPGA之FPGA_100天之旅_边沿检测

2017-08-17 09:46:51

我在手册上看到AD9361 LVDS模式发送数据的时钟要使用双边沿,在FPGA中,我将FB_CLK倍频到2倍使用单边沿发送数据,再将FB_CLK不变输出到ad9361,这样可以吗?还是必须在FPGA中直接使用FB_CLK双边沿发送数据?

2018-10-15 09:21:23

打开开关的时候,功耗就上来了,无法进入低功耗模式,如何让我们的蓝牙模块监测到高低电平之后,进入低功耗模式?群里问了下,说需要让该io口支持双边沿触发,即,上升沿和下降沿同时触发检测,请问,方向是否是正确的?其二,如果正确,如果设置双边沿触发?

2019-11-07 15:55:30

的数据进行计数;停止位不参与,起始位加上数据位共9bit。该计数器的计数周期为9。本工程使用了检测信号下降沿的方法,信号下降沿的检测方法:检查uart_rx的下降沿,就要用到FPGA里的边沿检测技术

2019-11-29 10:08:59

本人想做黑白块的边沿检测,但是为了达到检测的高精度,普通光电对管与光电传感器的区别在哪里?因为原理相同,也不知道到底性能差别在哪里?有没有大神可以一起讨论一下?

2015-05-31 09:47:10

二极管的检测方法与经验 1?检测小功率晶体二极管 A?判别正、负电极 (a)?观察外壳上的的符号标记。通常在二极管的外壳上标有二极管的符号,带有三角形箭头的

2009-10-07 12:02:21 12

12 三极管的检测方法与经验 1?中、小功率三极管的检测 A?已知型号和管脚排列的三极管,可按下述方法来判断其性能好坏 (a)?测

2009-10-07 12:03:17 36

36 FPGACPLD设计经验与技巧

2010-02-09 09:43:56 73

73 三极管的检测方法与经验

2006-04-17 21:41:56 4596

4596 二极管的检测方法与经验

2006-04-17 21:41:58 1459

1459

电感器、变压器检测方法与经验

2006-04-17 21:42:11 660

660 电容器检测方法与经验

2006-04-17 21:42:16 576

576 电阻器的检测方法与经验

2006-08-08 09:56:00 760

760

常用电子元器件检测方法与经验

2006-06-30 19:26:14 2969

2969

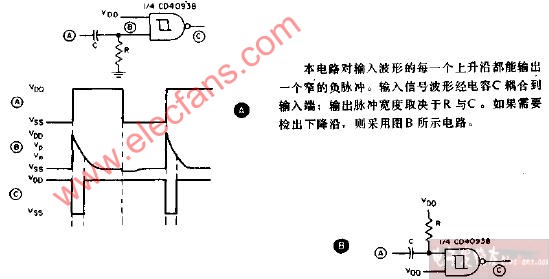

脉冲边沿检出器电路图

2009-03-28 09:20:16 560

560

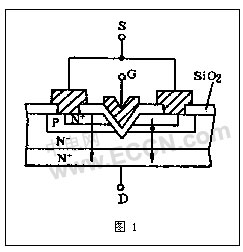

场效应管检测方法与经验

一、用指针式万用表对场效应管进行判

2009-07-02 18:28:30 427

427

CMOS触发器在CP边沿的工作特性研究

对时钟脉冲(简称CP)边沿时间的要求,是触发器品质评价的重要指标之一。触发器只有在CP边沿陡峭(短的边沿时

2009-10-17 08:52:12 1621

1621

电容器的检测方法与经验 1 固定电容器的检测 A 检测10pF以下的小电容 因10pF以下的固定电容器容量太小,用万用表进行测量,只能定性的检查其是否有漏

2009-11-24 11:15:59 840

840 电感器、变压器检测方法与经验 1 色码电感器的的检测 将万用表置于R×1挡,红、黑表笔各接色码电感器的任一引出端,此时指针应向右摆动。根据测出

2009-11-24 11:17:22 1005

1005 效应管检测方法与经验

一、用指针式万用表对场效应管进行判别(1)用测电阻法判别结型场效应管的电极根据场效应管的PN结

2009-11-30 10:52:21 1462

1462 基于FPGA的图像边缘检测

引言

图像边缘检测是图像处理的一项基本技术,在工业、医学、航天和军事等领域有着广泛的应用。图像处理的速度一直是一

2010-01-14 11:07:57 1714

1714

可以将电平触发器转换成更为灵活的边沿触发器(采用时间控制方法)。边沿触发器只在上升沿或下降沿处对输入采样。这种转换可以这样来实现:将原来的时钟信

2010-08-10 11:10:26 5657

5657

为了满足对随机数性能有一定要求的系统能够实时检测随机数性能的需求,提出了一种基于FPGA的随机数性能检测设计方案。根据NIST的测试标准,采用基于统计的方法,在FPGA内部实现了

2013-07-24 16:52:06 45

45 100条FPGA经验 非常值得收藏

100条FPGA经验 非常值得收藏

2015-11-11 17:01:11 22

22 分析了FPGA器件发生单粒子效应的空间分布特性,设计并实现了一种面向FPGA单粒子软错误的检测电路。将该电路放置在FPGA待检测电路的附近,利用单粒子效应的空间特性,则可以根据检测模块的状态变化

2015-12-31 09:25:13 8

8 sobel_FPGA l边缘检测.源代码。

2016-05-03 16:42:45 8

8 fpga经验谈,有需要的朋友可以下来看看。

2016-05-10 10:46:40 23

23 电路设计[FPGA]设计经验,有需要的下来看看

2016-05-20 11:16:35 46

46 电子专业单片机相关知识学习教材资料——FPGACPLD数字电路设计经验,感兴趣的小伙伴们可以瞧一瞧。

2016-09-13 17:46:48 0

0 一种单锁存器CMOS三值D型边沿触发器设计

2017-01-17 19:54:24 25

25 边沿触发一般时间短,边沿触发一般时间都是us级的,响应要快的,而电平触发只须是高和低就可以了,没时间要求,比如10s 时间内总是低电平,那么它也是触发的,比如中断计时或计数,最好用边沿触发,用电平触发误差会很大,电平触发一般用于简单报警,开关一类(时间要求不高的

2017-11-14 11:38:47 27141

27141

边沿检测与提取程序

2018-01-29 14:56:31 0

0 本文开始介绍了JK触发器工作特性与边沿JK触发器的特点,其次介绍了边沿JK触发器工作原理与特点,最后介绍了集成边沿式JK触发器边沿式JK触发器设计及波形仿真图形。

2018-01-30 17:17:49 35481

35481

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 69649

69649

本文记录一下关于用移位寄存器实现边沿检测的技巧。要学会硬件思维式的“模块式”读写代码,那么请多看别人的代码,并用ISE或者VIVADO综合出来看看。 边沿检测 边沿检测,顾名思义,就是检查信号的边沿

2018-04-15 10:26:01 2933

2933 设计背景: 在我们工程设计中,有时会需要到上升沿和下降沿这么一个说法,通过上升沿和下降沿来驱动一个电路,那么学习边沿检测就非常的重要了。 设计原理 : 在学习边沿检测前我们先学习一下下面的电路,这样

2018-06-13 11:20:07 5161

5161

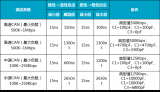

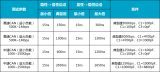

边沿时间分为上升沿时间、下降沿时间。下降沿时间是按照电压(20%~80%电压区间,有些按照10%~90%电压区间测量边沿时间,文中以20%~80%电压区间测量边沿时间)。表中给出时间范围,如果超出

2018-09-22 08:51:00 16710

16710

CAN总线边沿时间会影响采样正确性,而采样错误会造成错误帧不断出现,影响CAN总线通信。

2018-11-23 14:04:27 7540

7540

元器件的检测方法和经验很有必要以下对常用电子元器件的检测经验和方法进行介绍供对考包括了:一电阻器的检测方法与经验 ,二电容器的检测方法与经验,三电感器变压器检测方法与经验

2019-02-18 08:00:00 14

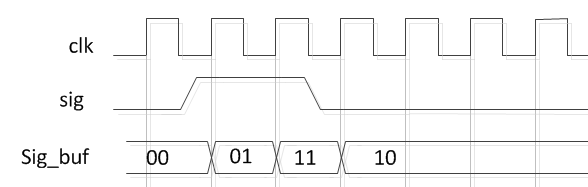

14 边沿检测电路(edge detection circuit)是个常用的基本电路。所谓边沿检测就是对前一个clock状态和目前clock状态的比较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测

2019-11-19 07:09:00 10011

10011 ADSY8401:带VCOM、NRS缓冲器和高压边沿检测器的LCD电平移位器数据表

2021-04-30 09:55:16 10

10 FPGA CPLD数字电路设计经验分享.(电源技术发展怎么样)-FPGA CPLD数字电路设计经验分享

2021-09-18 10:58:03 51

51 “ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34:56 1747

1747 边沿采样技术实现上升沿捕获进而实现外部信号的上升沿触发。 边沿检测电路的实现方法; 1、always @ (posedge signal) FPGA不便于处理此类触发信号,除非外部输入信号作为全局时钟使用。另外众所周知由于电路不能能避免抖动现象,所以用这

2022-11-26 10:20:09 914

914 边沿检测指令有扫描操作数的信号下降沿指令和扫描操作数的信号上升沿指令。

2023-04-10 09:38:27 884

884 边沿检测指令有扫描操作数的信号下降沿指令和扫描操作数的信号上升沿指令。

2023-04-12 09:23:26 4666

4666 本文将从Verilog和边沿检测的基本概念入手,介绍Verilog边沿检测的原理和应用代码示例。

2023-05-12 17:05:56 2183

2183

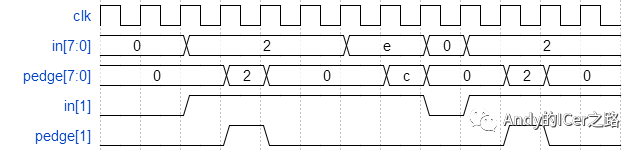

对于8位向量中的每个位,检测输入信号何时从一个时钟周期的0变为下一个时钟周期的1(类似于上升沿检测)。应在从0到1的跳变发生后的周期内设置输出位。

2023-06-05 16:24:02 541

541

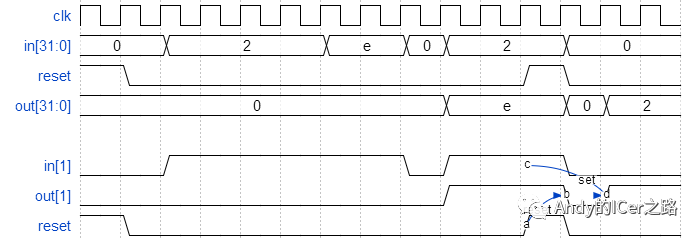

在设计双边沿采样电路(Dual-edge triggered flip-flop)之前,先从单边沿采样电路设计(Edge capture register)开始。

2023-06-05 16:27:30 852

852

1、什么是边沿检测 边沿检测用于检测信号的上升沿或下降沿,通常用于使能信号的捕捉等场景。 2、采用1级触发器的边沿检测电路设计(以下降沿为例) 2.1、设计方法 设计波形图如下所示: 各信号说明如下

2023-06-17 14:26:40 1244

1244

边沿检测大致分为:上升沿检测,下降沿检测和,双沿检测。原理都是通过比输入信号快很多的时钟去采集信号,当出现两个连续的采集值不等的时候就是边沿产生处。

2023-06-28 15:19:12 1037

1037

。如果该指令检测到 RLO 从“0”变为“1”,则说明出现了一个信号上升沿。 每次执行指令时,都会查询信号上升沿。检测到信号上升沿时,该指令输出 Q 将立即返回程序代码长度的信号状态“1”。在其它任何情况下,该输出返回的信号状态均为“0”。 说明 修改边沿

2023-06-28 16:20:11 355

355

FPGA设计经验谈

2022-12-30 09:20:07 1

1 电子发烧友网站提供《FPGA/CPLD数字电路设计经验分享.pdf》资料免费下载

2023-11-21 11:03:12 3

3

电子发烧友App

电子发烧友App

评论